тую, вторые входы которьрс подключены к информационному входу-выходу магистрального приемопередатчика, выходы элементов И первой и третьей групп подключены к входам соответствующих элементов ИЛИ первой группы, выходы элементов И второй и четвертой групп подкхпочены к входам соответствующих элементов ИЛИ второй группы, выходы элементов ИЛИ первой

и второй групп подклю-чены к информационным входам центральных процессорных элементов группы, вход режима работы контроллера состояний подключен к входу признаков режима работы микропроцессора, адресные выходы центральных процессорных элементов группы объединены и подключены к адресному входу блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

МИКРОПРОЦЕССОР, содержащий группу центральных процессорных элементов, контроллер состояний, блок микропрограммного управления, память микрокоманд, магистральный приемопередатчик и блок синхронизации, причем выход блока синхронизации подключен к входам синхронизации центральных процессорных элементов группы, контроллера состояний, блока микропрограммного управления и к управляющему входу магистрального приемопередатчика, первый информационный вход которого подключен к выходу блока памяти микрокоманд и к входам кода микрокоманды блока мнкррпвргрэммного управлений, KQHTpejfJieps 姧т(яннй н ixe f(m коде операции центральшх процессорН1 1х злементов группы, вьпсоды признаков состояния которых подключены к входам признаков контроллера состояния, яыход признака модицикации адреса которого подключен к входу признака модификации блока микропрограммного управления, второй и третий информационные входы магистрального приемопередатчика подключены соответственно к адресным и информационным входам центральных процессорных элементов группы, информационные выходы центральных процессорных элементов группы объединены и подключены к информационному входу контроллера состояний , вход-выход кода команды и выход адреса блока микропрограммного управления подключены соответственно к информационному входу-выходу магистрального приемопередат(Л чика и к адресному входу блока памяти микрокоманд, отличающийся тем, что, с целью повышения быстродействия, в него введены два регистра, два дешифратора, две группы элементов ИЛИ, четыре группы элементов И и блок памяти, 00 причем выход блока синхронизации о со подключен к синхровходам первого и второго регистров, выходы которых подключены соответственно к входам со первого и второго дешифраторов, информационные входы первого и второго регистров подключены к выходу блока памяти микрокоманд, fc-и выход первого дешифратора подключен К У-му ВХОДУ выборки блока памяти ( k t, Ill где М кодачество модулей блока памяти), выход которого подключен к информационному входу-выходу магистрального приемопередатчика, выход второго дешифратора подключен к первым входам элементов И группы с первой по четвер

1

Изобретение относится к вычислительной технике и может быть использовано при разработке специализированных ЦВМ систем управления и контроля.

Цель изобретения - повышение быстродействия.

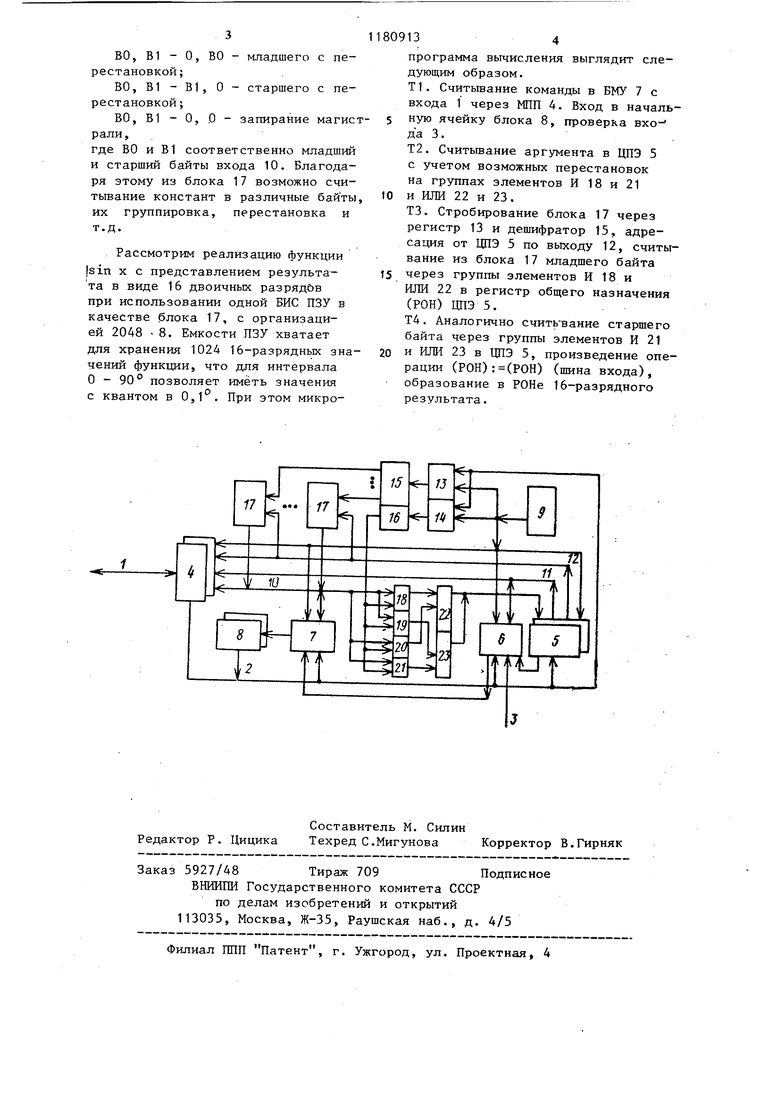

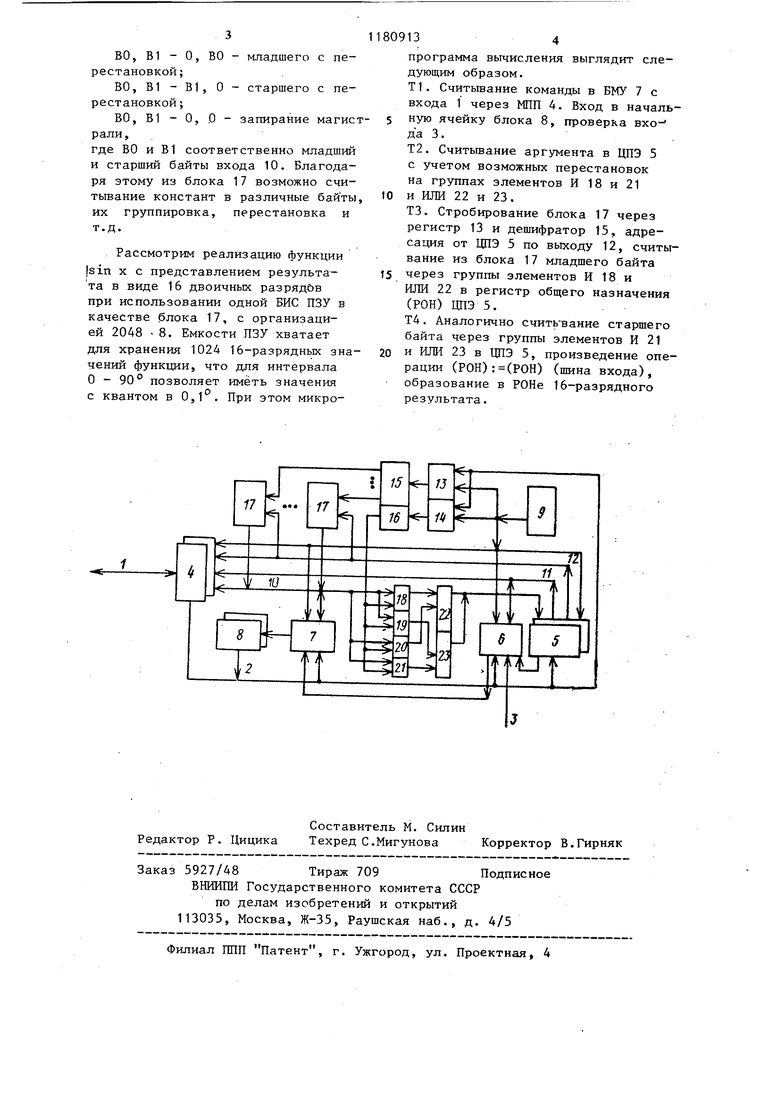

На чертеже представлена функциональная схема микропроцессора.

Микропроцессор содержит входвыход 1 микропроцессора, выход 2 кода микрокоманды, вход 3. признаков режима работы, магистральный приемопередатчик 4, группу 5 центральных процессорных элементов (ЩТЭ), контроллер 6 состояний (КС) блок 7 микропрограммного управления (БМУ), блок 8 памяти микрокоманд, блок 9 синхронизации, информационный вход-иыход 10, второй 11 и третий 12 информационные входы магистрального приемопередатчика, регистры 13 и 14, дешифраторы 15 и 16, блок 17 памяти, группы элементов И 18-21, группы элементов ИЛИ 22 и 23,

,Для повышения реальной производительности микропроцессора в составе специализированных систем в нем имеется блок 17 с таблицей коэффициентов, необходимых для реализации часто встречающихся функций. При этомсоответствующий разряд входа 3,.прдключенный к входу КС 6, переключается в единичное состояние, а одному из кодов несуществующих команд сопоставляется микропрограмма вычисления функции, заноСИМОЙ в блок 8, При прочтении кода такой команды в БМУ 7 происходит переход к микропрограмме прерывания по несуществующему коду с адре5 сом вектора входа-выхода 10, Но в этой микропрограмме до формирования вектора в ЦПЭ 5, стоит проверка разряда входа 3, соответствующего .коду принятой команды. Если КС 6 устанавливает, что соответствующий разряд входа 3 находится в состоянии 1, то в БМУ 7 происходит переход в микропрограмму вычисления функции вместо подпрограммы прерывания. Из блока 8 читается микрокоманда, загруженная в регистры 13 и 14, и через дешифратор 15 стробирующая выбор блока 17 с нужной таблицей коэффициентов,. ЦПЭ 5

повыходу 12 выдают аргумент на адресные входы блока 17, и на вход 10 подается значение функции. Код из регистра 14 через дешифратор 16, группы элементов И 18-21 и группы элементов ИЛИ 22 и 23 осуществляет необходимую коммутацюо входов ЦПЭ 5, Вход 10 имеет разрядность, равную 16, Группы элементов И 18-21 и ИЛИ 22 и 23 содержат по

0 в элементов. Управляя ими от дешифратора 16, можно осуществлять следующие пересылки:

ВО, В1 - ВО, В1 - прямая;

ВО, В1 - В1, ВО - с перестановкой байтов;

ВО, В1 - ВО, О - только младшего байта;

ВО, В1 - О, В1 - только старшего байта;

3

во, В1 - о, во - младшего с перестановкой;

ВО, В1 - В1, О - старшего с перестановкой ;

ВО, В1 - О, О - запирание магисрали ,

где ВО и В1 соответственно младший и старший байты входа 10. Благодаря этому из блока 17 возможно считывание констант в различные байты их группировка, перестановка и т.д.

Рассмотрим реализацию функции jsin X с представлением результата в виде 16 двоичных разрядЬв при использовании одной БИС ПЗУ в качестве блока 17, с организацией 2048 - 8. Емкости ПЗУ хватает для хранения 1024 16-разрядных значений функции, что для интервала 0-90 позволяет иметь значения с квантом в 0,1. При этом микро809134

программа вычисления выглядит следующим образом.

Т1. Считьшание команды в ЕМУ 7 с входа 1 через МПП 4. Вход в начальную ячейку блока 8, проверка вхо- да 3.

Т2. Считывание аргумента в ЦПЭ 5 с учетом возможных перестановок на группах элементов И 18 и 21

10 и ИЛИ 22 и 23.

ТЗ. Стробирование блока 17 через регистр 13 и дешифратор 15, адресация от ЦПЭ 5 по выходу 12, считывание из блока 17 младшего байта

t5 через группы элементов И 18 и

ИЛИ 22 в регистр общего назначения (РОН) ЦПЭ 5.

Т4. Аналогично считьвание старшего байта через группы элементов И 21

20 и ИЛИ 23 в ЦПЭ 5, произведение операции (РОН):(РОН) (шина входа), образование в РОНе 16-разрядного результата.

| Электронная промышленность, 1981, № 4, с | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Смолов В.В., Хвощ С.Т | |||

| Разработка процессоров с регулярной структурой для систем централизованного контроля и управления, отчет по НИР ВТ-89, ЛЭТИ, Л.: 1981, с | |||

| Счетная таблица | 1919 |

|

SU104A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-05—Подача