групп, выход второго элемента ИЛИ вой группы, второй выход регистра соединен с пятым входом коммутатора ошибок подключен к входу счетчии вторь(ми входами элементов.И пер- ка.

1180984

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК, содержащее регистровую матрицу, входы первой группы которой соединены с выходами элементов И-ШШ первой группы, а выходы первой группы подключены к соответствующим входам формирова- теля ошибок, вход и выход которого соединен соответственно с вторым выходом и третьим входом коммутатора, первый и второй входы которого соединены с соответствующими выходами элемента И-ШШ первой группы и регистровой матрицы, а первый и третий вьрсоды подключены к соответствующему входу регистровой матрицы и первому входу регистра ошибок второй вход которого соединен с выходом первого элемента ШШ, а первый выход и выходы первой и второй групп подключены соответственно к первым, вторым и третьим входам элементов И третьей группы, причем первые входы одних элементов И-ШШ первой группы соединены с выходами блока оперативной памяти, входы которого подключень к выходам элементов И первой группы, первые входы других элементов И-ШШ первой группы соединены с выходами накопителя, входы которого подключены к выходам элементов И второй группы, вторые входы одних элементов И-ШШ первой группы соединены с четвертым входом коммутатора и вторыми входами элементов И второй группы и подключены к входу записи устройства, вход воспроизведения которого соединен с вторыми входами других элементов И-ИЛИ первой группы, блок мажоритарных элементов, второй элемент ШШ, счетчик, отличающееся тем, что, с целью повышения надежности за счет коррекции большего количества ошибок, в него введена вторая группа элементов И-ИЛИ, причем первые входы одних элементов И-ШШ второй группы соединены с выходами мажоритарных элементов блока, первый, второй и третий входы которых подключены к перг- § вому выходу и соответствующим выходам второй и третьей групп регистра ошибок, первые входы других ii элементов И-ШШ второй группы соединены с выходами элементов И третьей группы, вторые входы одних элементов И-ИЛИ второй группы соединены с первым входом второго элемента ИЛИ и являю ся входами коррекции устройства, вторые входы других элементов И-ШШ второй группы соединены с вторым входом второго элемента ИЛИ и являются входом воспроизведения устройства, а выходы элементов И-ШШ второй группы соединены с входами первого элемента ИЛИ, входами группы регистра ошибок и входами второй группы регистровой матрицы, выходы второй группы которой подключены к первым входам элементов И первой и второй

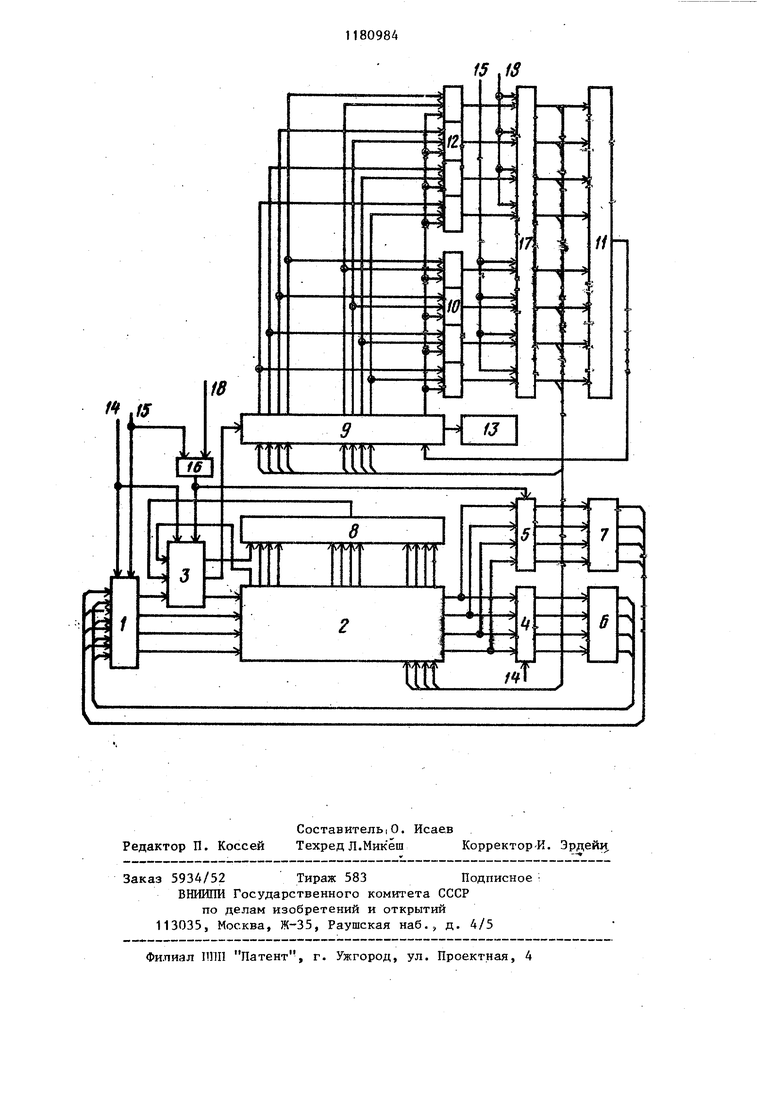

Изобретение относится к йьтислительной технике и может быть использовано для обнаружения сбоев и исправления информации, поступаю щей с внешних накопителей. Целью изобретения является повы шение надежности устройства за счет коррекции большего количества ошибок. На чертеже представлена структу ная схема устройства, . Устройство содержит первую груп пу элементов И-ШШ 1, регистровую матрицу 2, коммутатор 3, первзпо 4 и вторую 5 группу элементов И, накопитель 6, блок 7 оперативной памяти, формирователь 8 ошибок, регистр 9 ошибок, третью группу элементов И 10, первый элемент ИЛИ 11, блок 12 мажоритарных элементов, 13, вход 14 записи, вход 15 воспроизведения, второй элемент ИЛИ 16, вторую группу элементов И-ИЛИ 17, вход 18 коррек ции. Устройство работает следующим образом. Информация, подлежащая записи в накопитель 6, поступает по трем каналам из блока оперативной памяти на входы элементов И-ШШ 1 первой группы. По сигналу 14 записи третий вход коммутатора 3 подключается к его первому выходу, а второй и третий выходы коммутатора 3 подсоединяются внутри него к общей шине. В регистровой матрице 2 по внешним тактам (не показаны) происходит последовательный, сдвиг информации, поступающей Hd ее вход. Формирователь 8 ошибо в каждом такте суммирует по модул два выходные сигналы регистровой матрицы 2 с выходов разрядов одной прямой строки и двух диагональных строк. Выходные сигналы формирова теля 8 ошибок через коммутатор 3 в каждом такте поступают на вход четвертого контрольного канала регистровой матрицы 2 одновременно с информацией соответствуницей строки с соответствукщего выхода элемента И-ИЛИ 1 первой группы. Выходная информация матрицы 2, содержащая в каждой строке три информационных и один контрольный разряд через группу 4, открытую сигналом 14 записи, поступает на вход накопителя 6. Таким образом, в процессе записи устройство работает как шифратор, формируя в калздой строке контрольные разряды. В процессе записи информации блоки 5, .9, ..., 13, 16, 17 не участвуют. При воспроизведении информации СОвхода 15 подается команда воспроизведения . В коммутаторе 3 соединяются между собой одноимённые входы и выходы (первый вход с первым выходом и т.д.). Выходная информация накопителя 6 через элементы И-ШШ 1 первой группы и коммутатор 3 построчно параллельно-последовательным кодом поступает на вход регистровой матрицы 2, где происходит последовательный построчный сдвиг этой информации по внешним тактам. Одновременно по тактам сдвигается информация и в регистре 9 ошибок. В формирователе 8 ошибок в каждом такте суммируются по модулю два выходные сигналы регистровой матрицы 2. Отклонение от четности суммы сигналов, поступающих на вход формирователя 8 ошибок, воспринимается как сигнал ошибки, которьй с выхода формирователя 8 ошибок через коммутатор 3 поступает на вход регистра 9 ошибок и продвигается к его выходу параллельно с продвижением информации .в регистровой матрице 2. В процессе воспроизведения инфор мации происходит коррекция ошибок, представленных в регистре 9 ошибок тремя признаками (тремя единицами в определенном сочетании в зависимости от номера сбойного канала). При этом на выходе одного элемента И 10 третьей группы соответствующег го сбойному каналу, формируется импульс, который через вторую группу элементов И-ИЛИ 17 поступает на два третьих входа регистра 9 ошибок и на один третий вход матрицы 2, а через элемент ИЛИ 11 - на второй вход регистра 9 опшбок, изменяя состояние соответствукицего разряда выходной строки матрицы 2 и сбра сывая в О соответствующие разряды регистра 9 ошибок. При этом нулевой сигнал управления коррекцией 1 8 запрещает прохождение выходных сигналов блока 12 мажоритарных элементов через вторую группу элементов И-ИЛИ 17.мКод с выхода регис ровой матрицы 2 через открытую группу элементов И 5 переписывается в блок 7 оперативной памяти. В процессе воспроизведения не корректируются ошибки, представленные двумя признаками. Наличие таких ошибок и их количество фиксируется в счетчике 13. Для исправления ошибок, представ ленных двумя признаками, информация с блока 7 через элементы И-ШШ 1 первой группы и коммутатор 3 вновь подается на входы матрицы 2. На управляющие входы коммутатора 3 и накопителя 6 через элемент 16 и на управляющий вход элементов И-ИЛИ 17 второй группы с входа 18 подается команда коррекции. Блоки 1, 2, 3, 5, 7, 8, 9, 11, 13 работают так же, как и в режиме воспроизведения . Выходная информация с элементов И 10 третьей группы не про-;ходит через элементы И-ИГШ 17 второй группы, закрытые нулевым сигналом команды воспроизведения. Наличие двух признаков ошибок в регистре 9 ошибок в определенном сочетании в зависимости от номера сбойного канала фиксируется одним из мажоритарных элементов блока 12, выходной импульс которого проходит через элементы И-ИЛИ 1.7 второй группы и изменяет состояние соответствующего разряда выходной строки матрицы 2 и сбрасьтая в О соответствующие разряды регистра 9 ошибок. Выходная информация регистровой матрицы 2 через элементы И 5 второй группы записывается в блок 7 оперативной памяти. Количество оставшихся нескорректированных ошибок фиксируется в счетчике 13. При необходимости цикл коррекции повторяется до тех пор, пока в счетчике 13 не будет нулевой код или количество фиксируемых О1ш1бок не будет постоянным, что свидетельствует О наличии некорректируемых ошибок.. Таким образом, введение второй руппы элементов И-ИПИ с соответствующими связями и введение fioBbK связей между элементами известного устройстба позволяет повысить оличество устраняемых ошибок.

| Устройство для записи и воспроизведения информации | 1974 |

|

SU482772A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электроника, 1981, № 9, с | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1985-09-23—Публикация

1984-03-16—Подача