1

Изобретение относится к цифровой вычислительной технике и может быть использовано в высоконадежных вы- числительных средствах. ,

Цель изобретения - повышение надежности устройства.

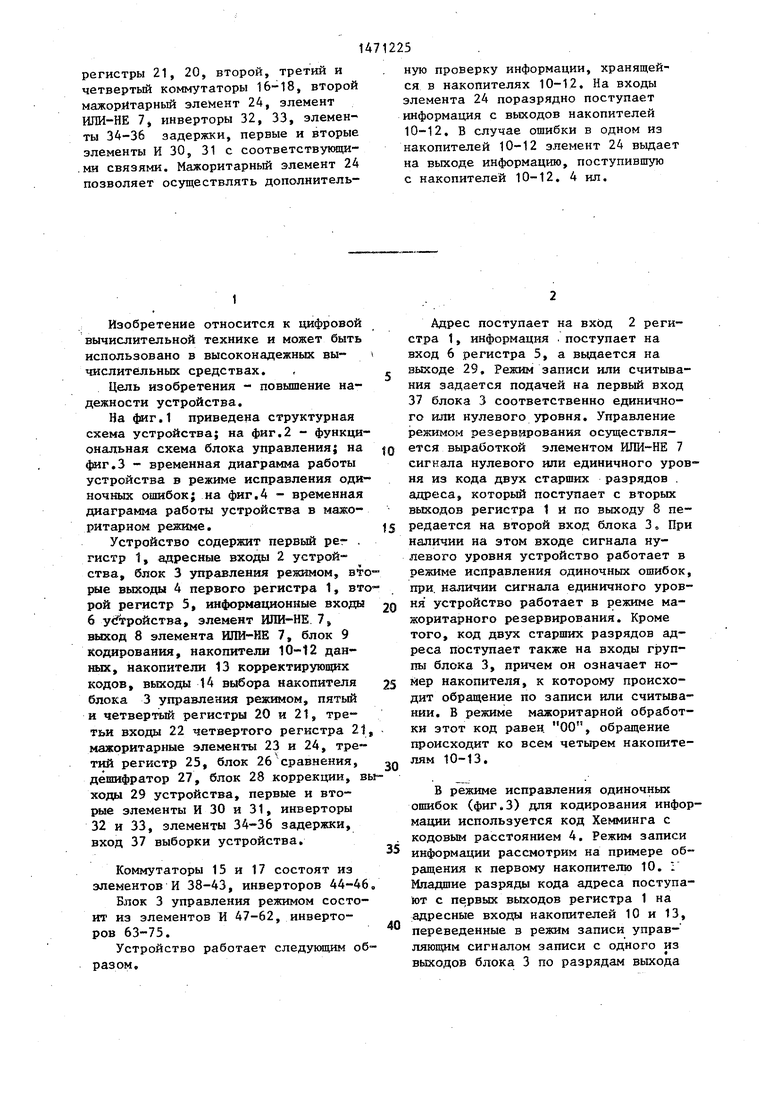

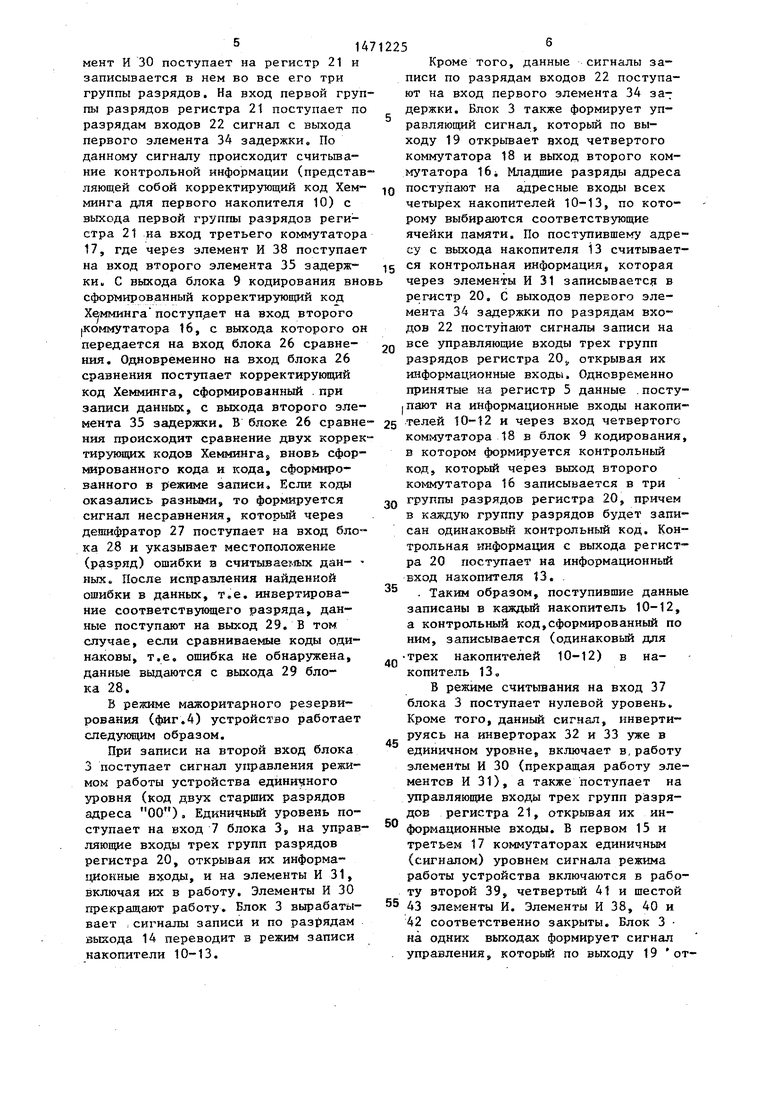

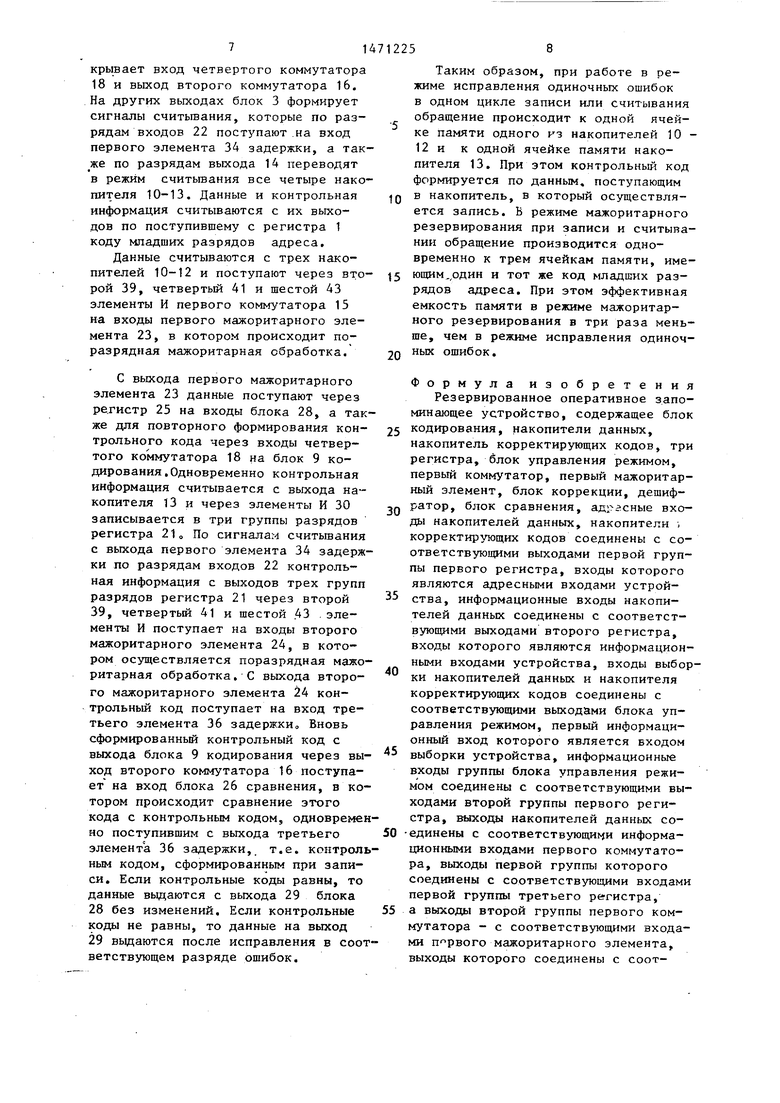

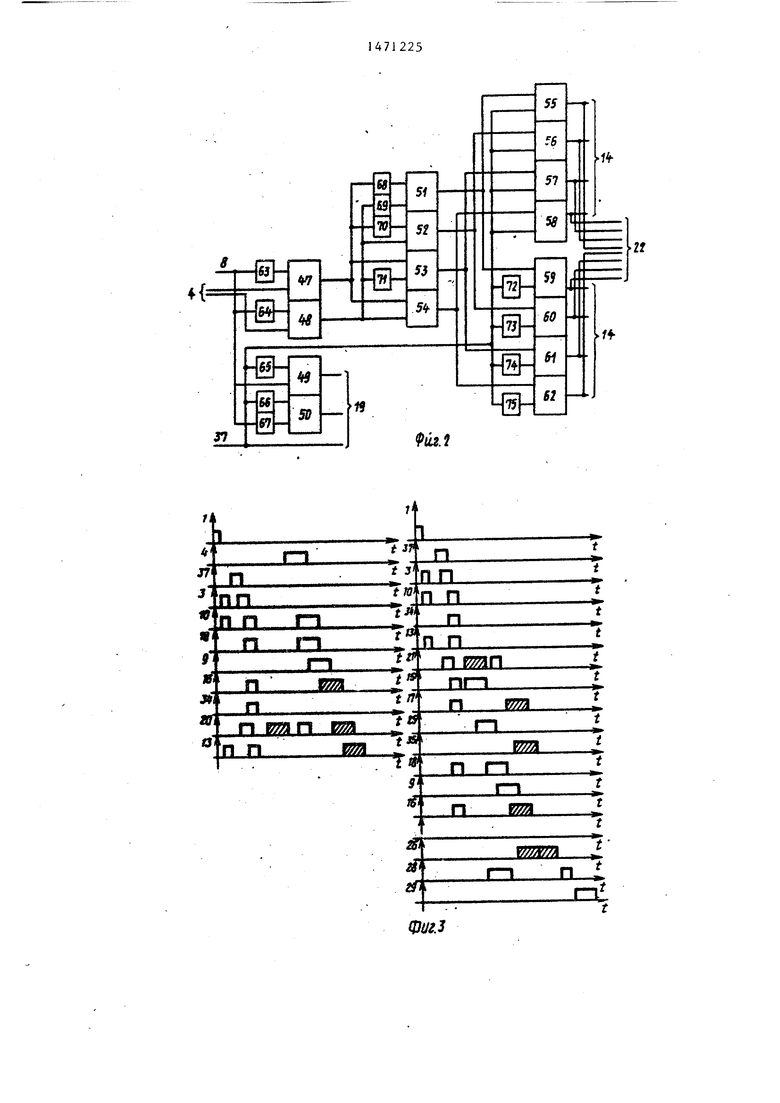

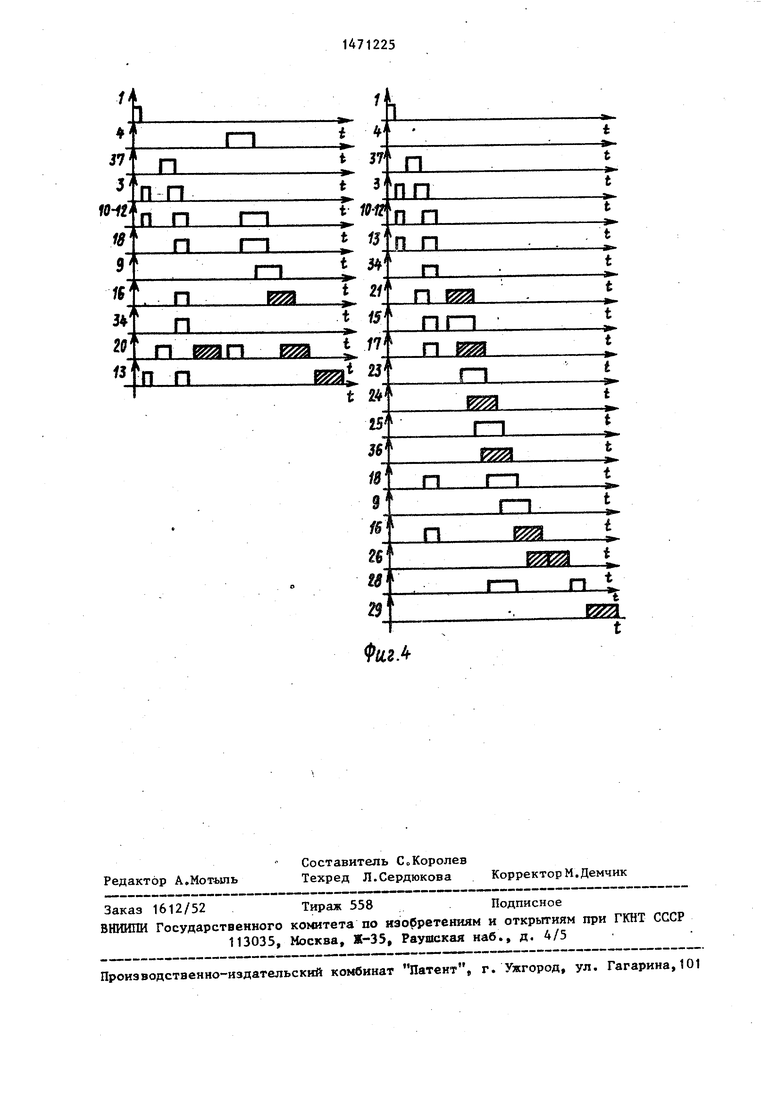

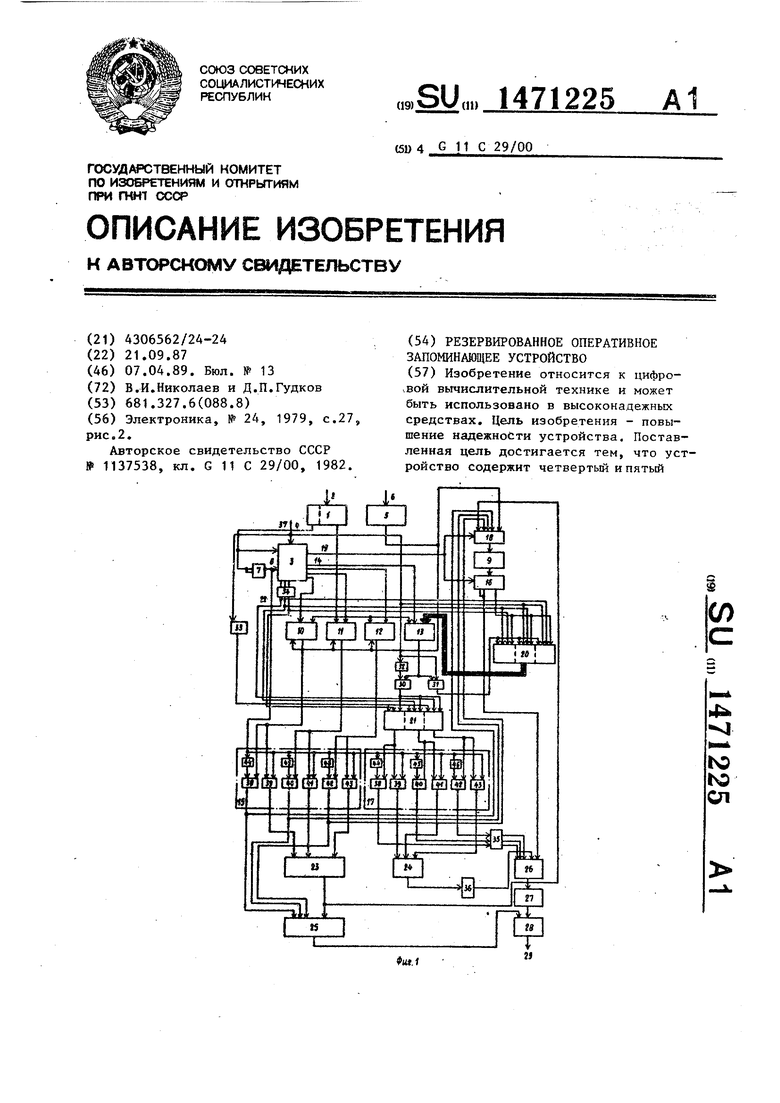

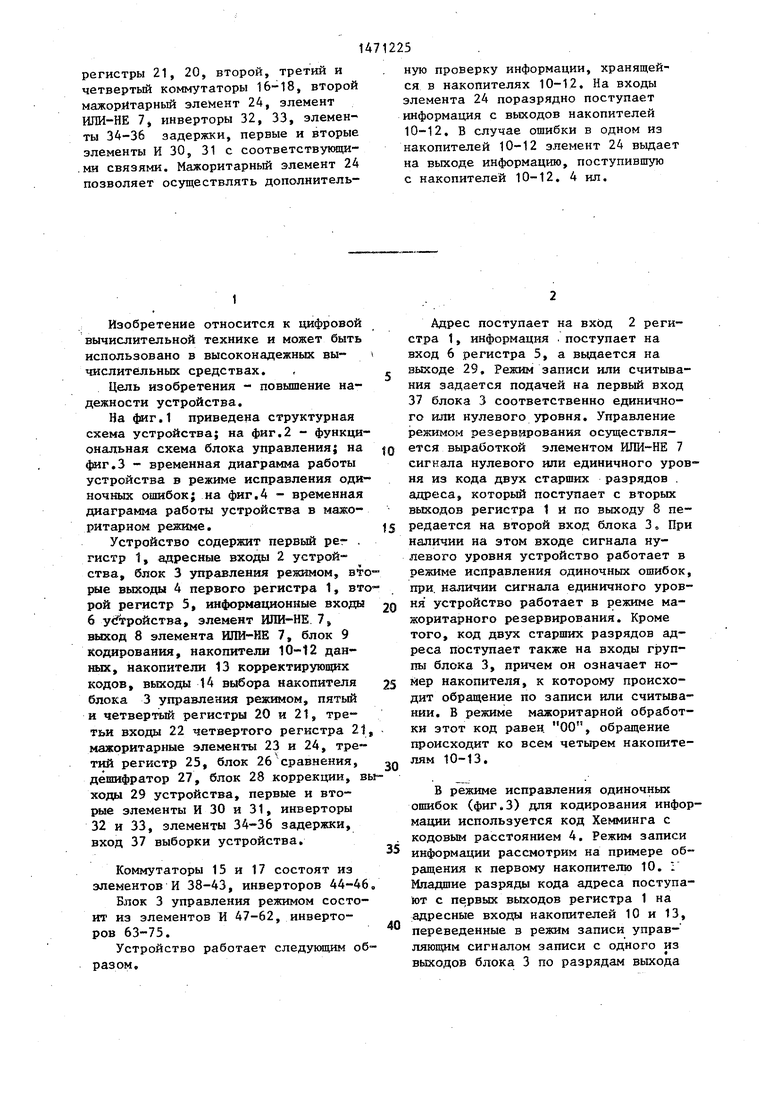

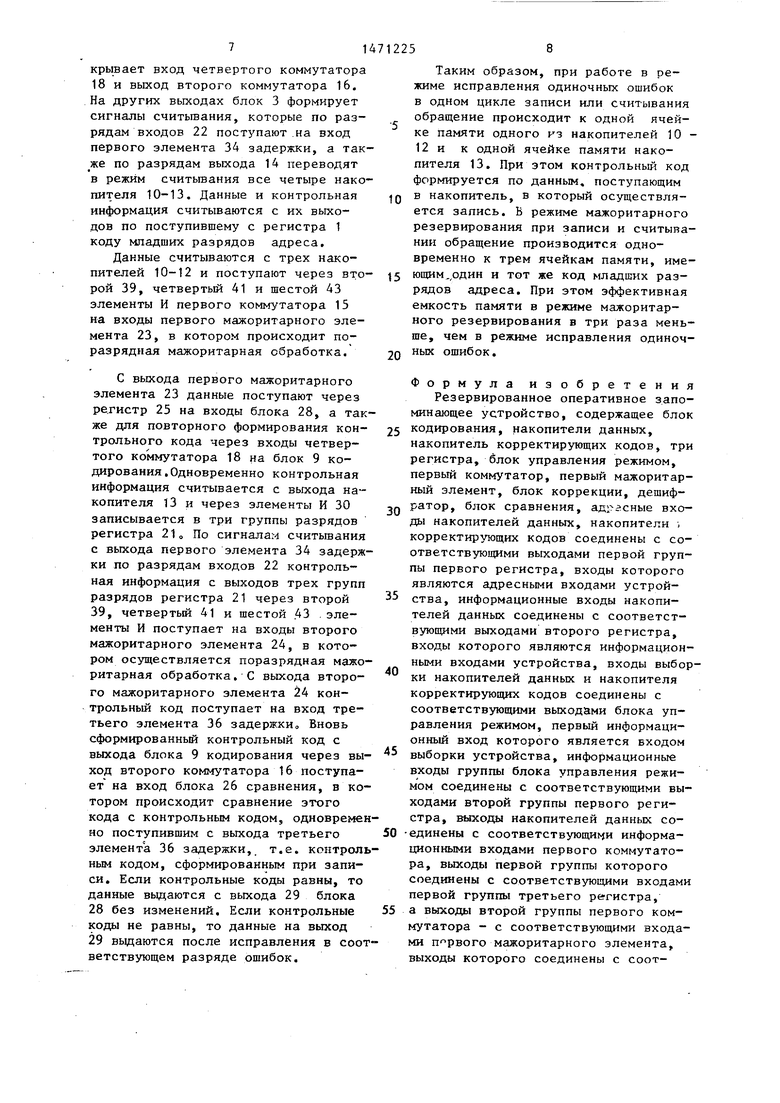

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - временная диаграмма работы устройства в режиме исправления одиночных ошибок; на фиг.4 - временная диаграмма работы устройства в мажоритарном режиме.

Устройство содержит первый per . гистр 1, адресные входы 2 устройства, блок 3 управления режимом, вто fftie выходы 4 первого регистра 1, второй регистр 5, информационные входы 6 устройства, элемент ИЛИ-НЕ. 7, выход 8 элемента ШШ-НЕ 7, блок 9 кодирования, накопители 10-12 данных, накопители 13 корректирующих кодов, выходы 14 выбора накопителя блока 3 управления режимом, пятый и четвертый регистры 20 и 21, третьи входы 22 четвертого регистра 21, мажоритарные элементы 23 и 24, третий регистр 25, блок 26 сравнения, дешифратор 27, блок 28 коррекции, выходы 29 устройства, первые и вторые элементы И 30 и 31, инверторы 32 и 33, элементы 34-36 задержки, вход 37 выборки устройства.

Коммутаторы 15 и 17 состоят из элементов И 38-43, инверторов 44-46.

Блок 3 управления режимом состоит из элементов И 47-62, инверторов 63-75.

Устройство работает следующим образом.

Адрес поступает на вход 2 регистра 1, информация . поступает на вход 6 регистра 5, а выдается на выходе 29. Режим записи или считывания задается подачей на первый вход 37 блока 3 соответственно единичного или нулевого уровня. Управление режимом резервирования осуществляется выработкой элементом ИЛИ-НЕ 7 сигнала нулевого или единичного уровня из кода двух старших разрядов . адреса, который поступает с вторых выходов регистра 1 и по выходу 8 передается на второй вход блока 3. При наличии на этом входе сигнала нулевого уровня устройство работает в режиме исправления одиночных ошибок, при. наличии сигнала единичного уровня устройство работает в режиме мажоритарного резервирования. Кроме того, код двух старших разрядов адреса поступает также на входы группы блока 3, причем он означает но- йер накопителя, к которому происходит обращение по записи или считывании. В режиме мажоритарной обработки этот код равен. 00, обращение происходит ко всем четырем накопителям 10-13.

В режиме исправления одиночных ошибок (фиг.З) для кодирования информации используется код Хемминга с кодовым расстоянием 4. Режим записи информации рассмотрим на примере обращения к первому накопителю 10. 1 Младшие разряды кода адреса поступают с первых выходов регистра 1 на адресные входы накопителей 10 и 13, переведенные в режим записи управляющим сигналом записи с одного из выходов блока 3 по разрядам выхода

14, выбирая ссответствующие ячейки памяти (сигналы записи или считывания на накопители 10-13 в блоке 3 формиру Ьтся с учетом кода двух старших разрядов адреса, в данном примере , и сигналами управления режимом работы и записи-считьгоания устройства).

Кромр того, сформированный в блоке 3 сигнал записи с других выходов блока 3 по разрядам входов 22 поступает на вход первого элемента 34 задержки. Сигнал единичного уровня (записи) , кроме поступления на вход 37 блока 3, поступает на управляющие входы трех групп разрядов регистра 20, открывая их информационные входы На данные входы поступает контрольная информация (представляющая собой корректирующие коды Хемминга для данных, записанных по поступившему адресу для каждого из трех накопителей 10-12), считываемая с выхода накопителя 13 через вторые элементы И 31, включенные в работу сигналом единичного уровня с входа 37 управления записью-считыванием. Таким образом, во все три группы разрядов регистра 20 записывается контрольная информацияj причем в первую группу разрядов записывается корректирующий код Хемминга для первого 10J во вторую группу код Хемминга для второго 11 и в. третью группу - код Хемминга для третьего 12 накопителей. После этой, записи на управляющий вход первой группы разрядов регистра 20 поступает по разрядам входов 22 сигнал записи с выхода первого элемента 34 задержки открывая его информационный вход.

Блок 3 формирует управляющий сигнал, который по выходу |9 открывает вход четвертого кo iмyтaтopa 18 и выход второго коммутатора 16. Одновременно данные с регистра 5 поступают на информационный вход первого накопителя 10 и на вход четвертого коммутатора 18, с выхода, которого они поступают на блок 9 кодирования в котором формируется корректирующий код Хемминга. Сформированный контрольньй код поступает через выход второго коммутатора 16 на вход первой группы разрядов регистра 20, в которой данный код записыватеся вместо корректирующего кода Хемминга, содержащегося в первой груп

0

5

0

5

0

5

0

5

пе разрядов. Полученная контрольная информация с выхода регистра 20 (с выходов его всех трех групп разрядов) поступает на информационный вход накопителя 13 и записывается в него.

Таким образом, по выбранному адресу в первый накопитель 10 записываются поступивпгие данные, а в накопитель 13 записывается контрольная информация t,

В режиме считывания для первого ;накогштеля 10 устройство работает следующим образом.

НЗ вход 37 блока 3 поступает нулевой уровень. Этот уровень прекра- :щает работу элемента И 31 и инвертируясь на инверторах 32 и 33 уже в виде единичного уровня, включает в работу элементы И 30, а также поступает на управляющие входы трех групп разрядов регистра 21, открывая их информационные входы. Младшие разряды кода адреса поступают на адресные входы накопителей 10 и 13, переведенные в режим считывания управлякицим сигналом считыва ния с одного из выходов блока 3 по разрядам выхода 14, выбирая соответствующие ячейки памяти, - роме того, данный сигнал считывания поступает по разрядам входов 22 на вход первого элемента 34 задержки. Одновременно блок 3 формирует управляющий сигнал, который открывает по выходу 19 вход четвертого коммутатора 18 и выход второго коммутатора 16. Сформированный на выходе элемента ИЛИ-НЕ. 7 сигнал управления режимом работы устройства поступает (кроме поступле ния его на вход блока 3) на первый 15 и третий 17 коммутаторы, где, инвертируясь на первом 44, втором 45 и третьем 46 инверторах, включает в работу первый 38, третий 40 и пятый 42 элементы И.

По сигналу считьюания с выхода накопителя 10 данные считываются на первый ко Е- утатор 15, где через элементы И 38 поступают на регистр 25 с выхода которого данные поступают на входы блока 28 и на вход четвертого коммутатора 18, с выхода которого данные поступают на блок 9 кодирования, где формируется по ним код Хемминга. Одновременно по сигналу считывания с выхода накопителя 13 контрольная информация чепез элемент И 30 поступает на регистр 21 и записывается в нем во все его три группы разрядов. На вход первой группы разрядов регистра 21 поступает по разрядам входов 22 сигнал с выхода первого элемента 34 задержки По данному сигналу происходит считьша- ние контрольной информации (представ™ ляющей собой корректирующий код Хем- минга для первого накопителя 10) с выхода первой группы разрядов регистра 21 на вход третьего коммутатора 17, где через элемент И 38 поступает на вход второго элемента 35 задержки. С выхода блока 9 кодирования вновь сформированный корректирующий код Хемминга поступает на вход второго Коммутатора 16, с выхода которого он передается на вход блока 26 сравнения. Одновременно на вход блока 26 сравнения поступает корректирующий код Хемминга, сформированный . при записи данных, с выхода второго эле10

15

20

Кроме того, данные сигналы записи по разрядам входов 22 поступают на вход первого элемента 34 задержки. Блок 3 также формирует управляющий сигнал, который по выходу 19 открывает вход четвертого коммутатора 18 и выход второго коммутатора 16i Младшие разряды адреса поступают на адресные входы всех четырех накопителей 10-13, по которому выбираются соответствующие ячейки памяти. По поступившему адресу с выхода накопителя 13 считывается контрольная информация, которая через элементы И 31 записываете в регистр 20, С выходов первого элемента 34 задержки по разрядам входов 22 поступают сигналы записи на все управляющие входы трех групп разрядов регистра 20j, открывая их информационные входы. Одновременно принятые на регистр 5 данные .посту- |Пают на информационные входы накопи30

35

40

мента 35 задержки, В блоке 26 сравне- 25 телей 10-12 и через вход четвертого ния происходит сравнение двух корректирующих кодов Хеммингаг вновь сформированного кода и кода, сформированного в режиме записи. Если коды оказались разными, то формируется сигнал несравнения, который через дешифратор 27 поступает на вход блока 28 и указывает местоположение (разряд) ошибки в считываег-аж дан- ных. После исправления найденной ошибки в данных, т.е. инвертирование соответствующего разряда, данные поступают на выход 29. В том случае, если сравниваемые коды одинаковы, т.е. ошибка не обнаружена, данные выдаются с выхода 29 блока 28.

В режиме мажоритарного резервирования (фиг.4) устройство работает следукяцим образом.

При записи на второй вход блока 3 поступает сигнал утфавления режимом работы устройства единичного уровня (код двух старших разрядов адреса 00), Едкничньй уровень поступает на вход 7 блока 3, на управляющие входы трех групп разрядов регистра 20, открывая их информационные входы, и на элементы И 31, включая их в работу. Элементы И 30 прекращают работу. Блок 3 вырабатывает .сигналы записи и по разрядам выхода 14 переводит в режим записи накопители 10-13.

коммутатора 18 в блок 9 кодирования, в котором формируется контрольный код, который через выход второго коммутатора 16 записывается в три группы разрядов регистра 20, причем в каждую группу разрядов будет записан одинаковый контрольный код. Контрольная s-шформация с выхода регистра 20 поступает на информационный вход накопителя 13. .

. Таким образом, поступившие данные записаны в каждый накопитель 10-12, а контрольный код,сформированный по ним, записывается (одинаковый для трех накопителей 10-12) в накопитель 13,

В режиме считывания на вход 37 блока 3 поступает нулевой уровень. Кроме того, данный сигнал, инвертируясь на инверторах 32 и 33 уже в единичном уровне, включает в,работу элементы И 30 (прекращая работу элементов И 31), а также поступает на управляющие входы трех групп разрядов регистра 21, открывая их информационные входы. В первом 15 и третьем 17 коммутаторах единичным (сигналом) уровнем сигнала режима работы устройства включаются в работу второй 39, четвертый 41 и шестой 5 43 элементы И. Элементы И 38, 40 и 42 соответственно закрыты. Блок 3 на одних выходах формирует сигнал . управления, который по выходу 19 от

45

50

5

0

Кроме того, данные сигналы записи по разрядам входов 22 поступают на вход первого элемента 34 задержки. Блок 3 также формирует управляющий сигнал, который по выходу 19 открывает вход четвертого коммутатора 18 и выход второго коммутатора 16i Младшие разряды адреса поступают на адресные входы всех четырех накопителей 10-13, по которому выбираются соответствующие ячейки памяти. По поступившему адресу с выхода накопителя 13 считывается контрольная информация, которая через элементы И 31 записываете в регистр 20, С выходов первого элемента 34 задержки по разрядам входов 22 поступают сигналы записи на все управляющие входы трех групп разрядов регистра 20j, открывая их информационные входы. Одновременно принятые на регистр 5 данные .посту- |Пают на информационные входы накопи0

5

0

5 телей 10-12 и через вход четвертого

коммутатора 18 в блок 9 кодирования, в котором формируется контрольный код, который через выход второго коммутатора 16 записывается в три группы разрядов регистра 20, причем в каждую группу разрядов будет записан одинаковый контрольный код. Контрольная s-шформация с выхода регистра 20 поступает на информационный вход накопителя 13. .

. Таким образом, поступившие данные записаны в каждый накопитель 10-12, а контрольный код,сформированный по ним, записывается (одинаковый для трех накопителей 10-12) в накопитель 13,

В режиме считывания на вход 37 блока 3 поступает нулевой уровень. Кроме того, данный сигнал, инвертируясь на инверторах 32 и 33 уже в единичном уровне, включает в,работу элементы И 30 (прекращая работу элементов И 31), а также поступает на управляющие входы трех групп разрядов регистра 21, открывая их информационные входы. В первом 15 и третьем 17 коммутаторах единичным (сигналом) уровнем сигнала режима работы устройства включаются в работу второй 39, четвертый 41 и шестой 5 43 элементы И. Элементы И 38, 40 и 42 соответственно закрыты. Блок 3 на одних выходах формирует сигнал . управления, который по выходу 19 от5

0

крывает вход четвертого коммутатора 18 и выход второго коммутатора 16. На других выходах блок 3 формирует сигналы считывания, которые по разрядам входов 22 поступают .на вход первого элемента 34 задержки, а так же по разрядам выхода 14 переводят в режим считьюания все четыре накопителя 10-13. Данные и контрольная информация считываются с их выходов по поступившему с регистра 1 коду младших разрядов адреса.

Данные считываются с трех накопителей 10-12 и поступают через второй 39, четвертый 41 и шестой 43 элементы И первого коммутатора 15 на входы первого мажоритарного элемента 23, в котором происходит поразрядная мажоритарная обработка.

С выхода первого мажоритарного элемента 23 данные поступают через регистр 25 на входы блока 28, а также для повторного формирования контрольного кода через входы четвертого коммутатора 18 на блок 9 кодирования ,Одновременно контрольная информация считывается с выхода накопителя 13 и через элементы И 30 записывается в три группы разрядов регистра 21,, По сигналам считьшания с выхода первого элемента 34 задержки по разрядам входов 22 контрольная информация с выходов трех групп разрядов регистра 21 через второй 39, четвертый 41 и шестой 43 . элементы И поступает на входы второго мажоритарного элемента 24, в котором осуществляется поразрядная мажоритарная обработка. С выхода второго мажоритарного элемента 24 контрольный код поступает на вход третьего элемента 36 задержки. Вновь сформированный контрольный код с выхода блока 9 кодирования через выход второго коммутатора 16 поступает на вход блока 26 сравнения, в котором происходит сравнение этого кода с контрольным кодом, одновременно поступившим с выхода третьего элемента 36 задержки, т.е. контрольным кодом, сформированным при записи. Если контрольные коды равны, то данные выдаются с выхода 29 блока

28без изменений. Если контрольные коды не равны, то данные на выход

29выдаются после исправления в соответствующем разряде ошибок.

Таким образом, при работе в режиме исправления одиночных ошибок в одном цикле записи или считывания обращение происходит к одной ячейке памяти одного из накопителей 10 - 12 и к одной ячейке памяти накопителя 13. При этом контрольный код формируется по данным, поступающим

Q в накопитель, в который осуществляется запись. В режиме мажоритарного резервирования при записи и считывании обращение производится одновременно к трем ячейкам памяти, име5 и тот же код младших разрядов адреса. При этом эффективная емкость памяти в режиме мажоритарного резервирования в три раза меньше, чем в режиме исправления одиночQ ных ошибок.

Формула изобретения Резервированное оперативное запоминающее устройство, содержащее блок

5 кодирования, накопители данных,

накопитель корректирующих кодов, три регистра, блок управления режимом, первый коммутатор, первый мажоритарный элемент, блок коррекции, дешифР ратор, блок сравнения, ад гсные входы накопителей данных, накопители , корректирующих кодов соединены с соответствующими выходами первой группы первого регистра, входы которого являются адресными входами устрой5 ства, информационные входы накопителей данных соединены с соответствующими выходами второго регистра, входы которого являются информационными входами устройства, входы выборки накопителей данных и накопителя корректируюпщх кодов соединены с соответствующими выходами блока управления режимом, первый информационный вход которого является входом

выборки устройства, информационные входы группы блока управления режимом соединены с соответствующими выходами второй группы первого регистра, выходы накопителей данных со0 -единены с соответствующими информационными входами первого коммутатора, выходы первой группы которого соединены с соответствующими входами первой группы третьего регистра,

5 а выходы второй группы первого коммутатора - с соответствующими входами первого мажоритарного элемента, выходы которого соединены с соот0

914

ветствующими входами второй группы третьего регистра, выход которого соединен с информационным входом бло ка коррекции, входы управления коррекцией которого соединены с соответствующими выходами дешифратора, входы которого соединены с cooTBeTd ствующими выходами блока сравнения,

выходы блока коррекции являются вы-

ходами устройства, отличаю.- щ е е с я тем, что, с целью повышения надежности, оно содержит чет- вер-плй.и пятый регистры, второй,третий и четвертый коммутаторы, второй мажоритарный элемент, элемент ИЛИ-НБ два инвертора, три элемента задержки, первые и вторые элементы И,, первые входы которых соединены с соот- ветствуюпщми выходами накопителя кор .ректирующих кодов, вторые входы соединены с выходом и входом первого инвертора соответственно, вход которого соединен с первым информационны входом блока управления режимом и с входом второго инвертора, выход которого соединен с входами первой группы четвертого регистрав вторые входы которого соединены с выходами первых элементов И, входы третьей группы четвертого регистра соединены с соответств5тощими выходами первого элемента задержки и с соответствующими входами первой группы пятого регистра, входы второй группы которого соединены с входом .Ьервого инвертора,, входы третьей группы с выходами первой группы второго коммутатора, входы четвертой группы - с соответствующими выходами вторых элементов И, выходы пятого регистра соединены с соответствуницими информационными входами накопителя коректирующих кодов, вход управления коммутацией первого коммутатора со

единен с входом управления ко&®4ута-

5 Q 5 Q

AVi

5

0

10

цией третьего коммутатора, с вторым информационным входом блока управления режимом и с выходом элемента ИЛИ-НЕ, входы которого соединены с соответствующими выходами второй группы первого регистра, выходы второй группы первого коммутатора соединены с соответствующими информационными входами первой группы четвертого коммутатора, информационные входы второй группы которого соединены с соответствующими выходами второго регистра, а информа- щюнные входы третьей группьг - с соответствующими выходами первого мажоритарного элемента, входы уп равления коммутацией четвертого ком мутатора соединены с соответствующими входами управления коммутацией второго коммутатог а и с выходами .выборки коммутаторов блока управления , выходы задания режима которого (соединены с соответ- ствуюарми входами первого элемента задержки, выходы четвертого коммутатора соединены с соответствуюврочи входами блока кодирования, выходы которого соединены с соответству- кйдими информационными входами второго коммутатора, вторые выходы которого соединены с соответствующими входами первой группы блока сравнения, входы второй и третьей групп которого соединены с соответствующими выходами второго и третьего элементов задержки соответственно, входы второго элемента задержки соединены с соответствующими выходами первой группы третьего коммутатора, выходы второй группы которого соединены с соответствующими входами второго мажоритарного элемента, выходы которого соединены с соответству™ шщими входами третьего элемента задержки.

ШЛ

РигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Резервированное запоминающее устройство с коррекцией информации | 1990 |

|

SU1751820A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в высоконадежных вычислительных средствах. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что устройство содержит четвертый и пятый регистры 21,20, второй, третий и четвертый коммутаторы 16-18, второй мажоритарный элемент 24, элемент ИЛИ-НЕ 7, инверторы 32,33, элементы 34-36 задержки, первые и вторые элементы И 30,31 с соответствующими связями. Мажоритарный элемент 24 позволяет осуществлять дополнительную проверку информации, хранящейся в накопителях 10-12. На входы элемента 24 поразрядно поступает информация с выходов накопителей 10-12. В случае ошибки в одном из накопителей 10-12 элемент 24 выдает на выходе информацию, поступившую с накопителей 10-12. 4 ил.

| Электроника, № 24, 1979, с.27, рис.2 | |||

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-04-07—Публикация

1987-09-21—Подача