A,A,,jC,(;,C(iC,P,P

е

(Л

4 Ю

сд

Oi

У

сг

CS

ъ

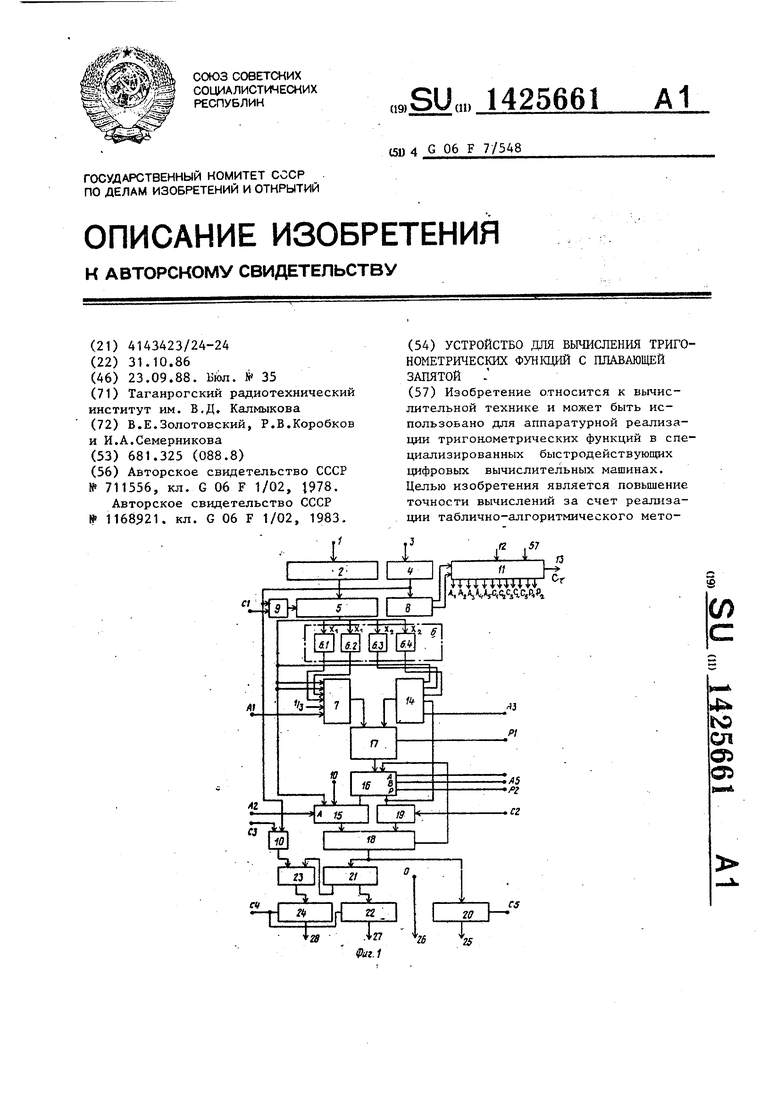

Фаг.1

гб

2S

да вычислений. Устройство содержит вход 1 первого аргумента, входной регистр 2 аргум та, вход 3 второго аргумента, входной регистр 4 порядка сдвигатель 5, блоки памяти значейий функции 6.1,6.2, 6.3, 6.4 группы блоков памяти 6,1. первый коммутатор 7, схему сравнения 8, элементы И 9 первой группы, элементы И 10 второй группы, блок 11 управления, такто вый вход 12, выход 13 готовности.

втррой коммутатор 14, третий коммутатор 15, блок 16 адресуемых регистров, умножитель 17, первый сумматор 18, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 19 группы, первый выходной регистр 20, блок нормализации 21, второй выходной регистр 22, второй сумматор 23, третий выходной регистр 24, первый, второй, третий, четвертый выходы 25, 26, 27, 28 результата соответственно. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

Изобретение относится к вычислительной технике и может быть использовано для аппаратурной реализации тригонометрических функций в специализированных быстродействующих цифровых вычислительных машинах. Целью изобретения является повьпиение точности вычислений за счет реализации таблично-алгоритмического мето

I

Изобретение относился к вычислительной технике и может быть исполь- : зован о для аппаратурной реализации I тригонометрических функций в специа- I лизированных быстродействующих циф- ровых вычислительных машинах. I Целью изобретения является повы- I шение точности вычислений за счет I реализации таблично-алгоритмического метода вычислений.

20

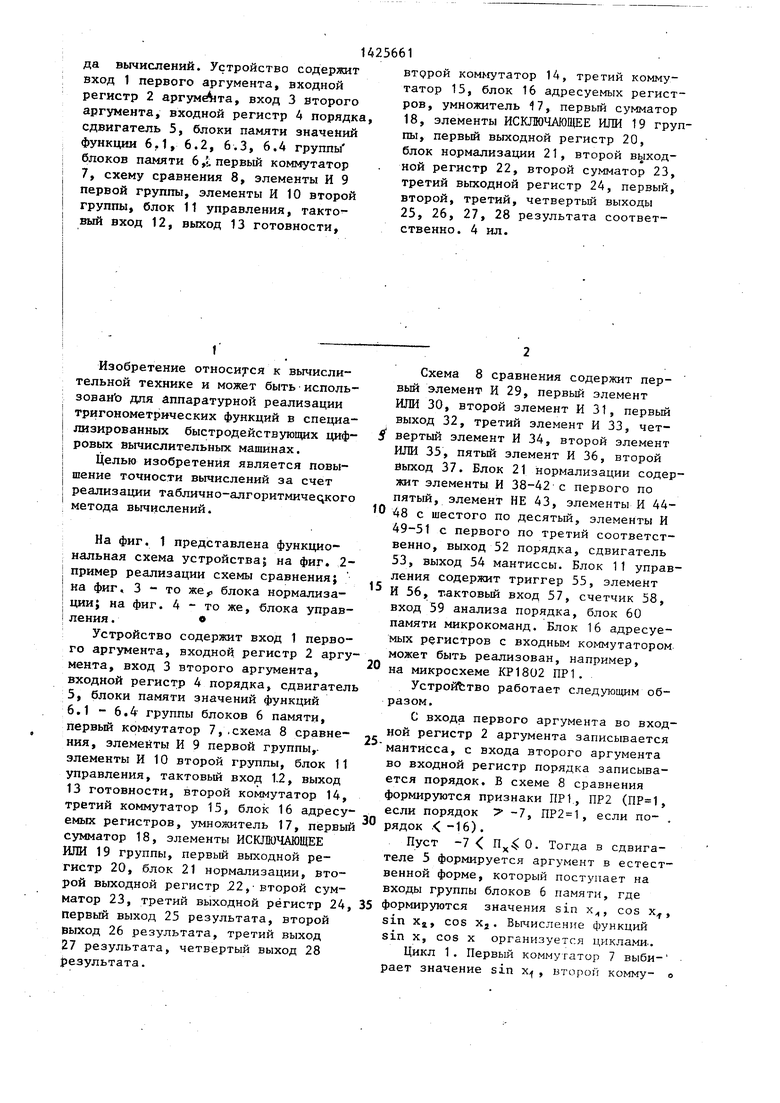

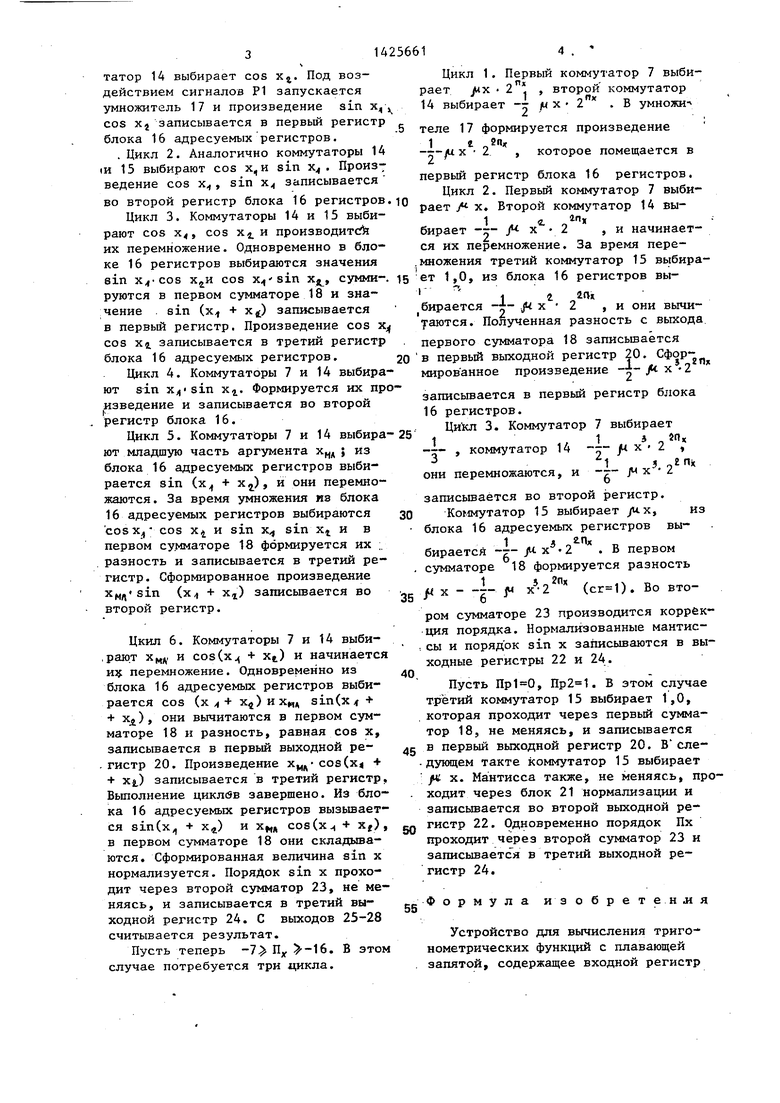

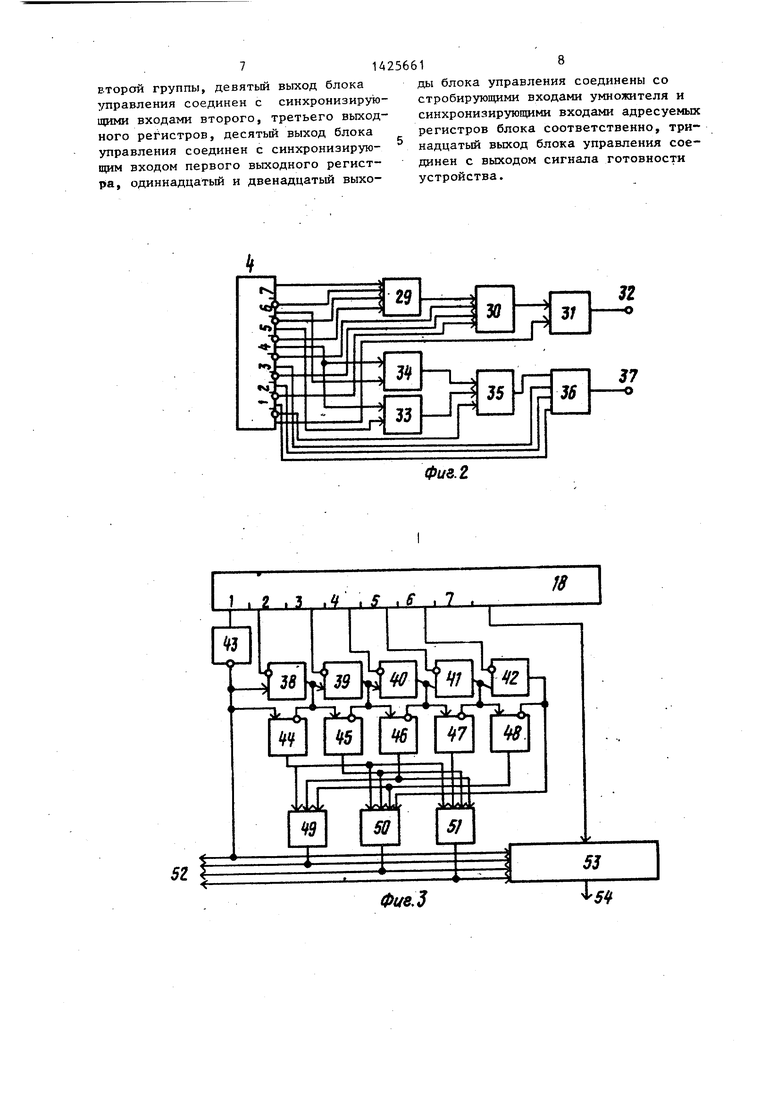

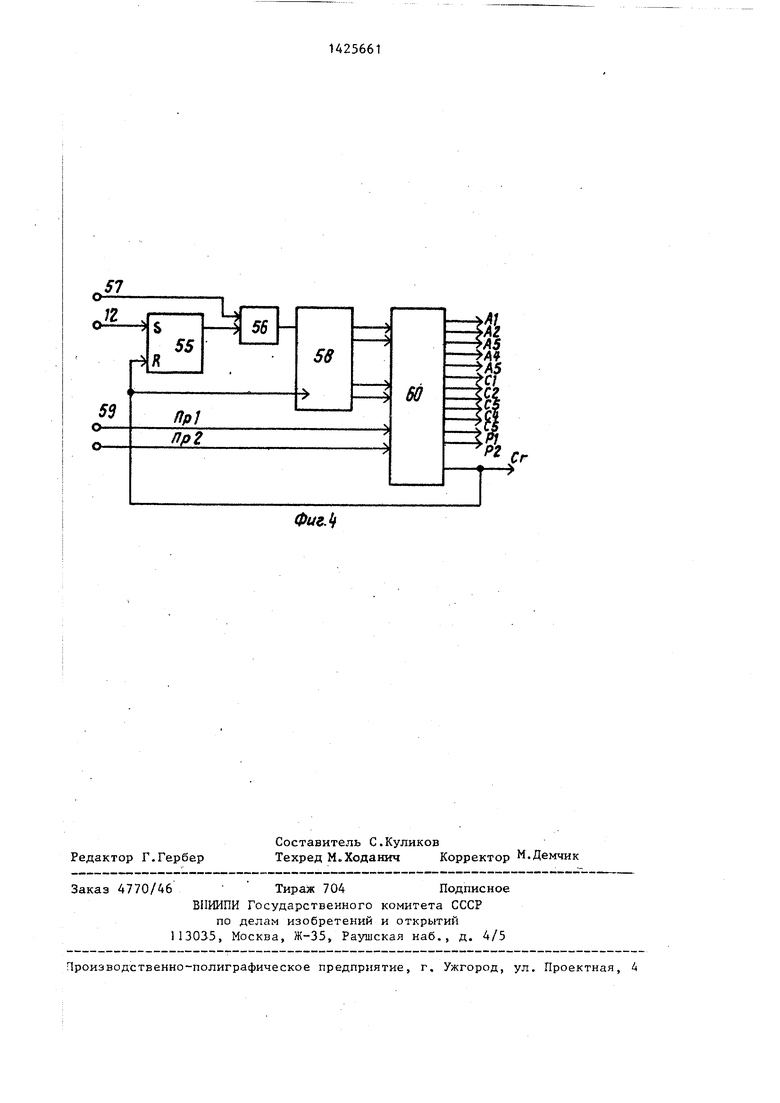

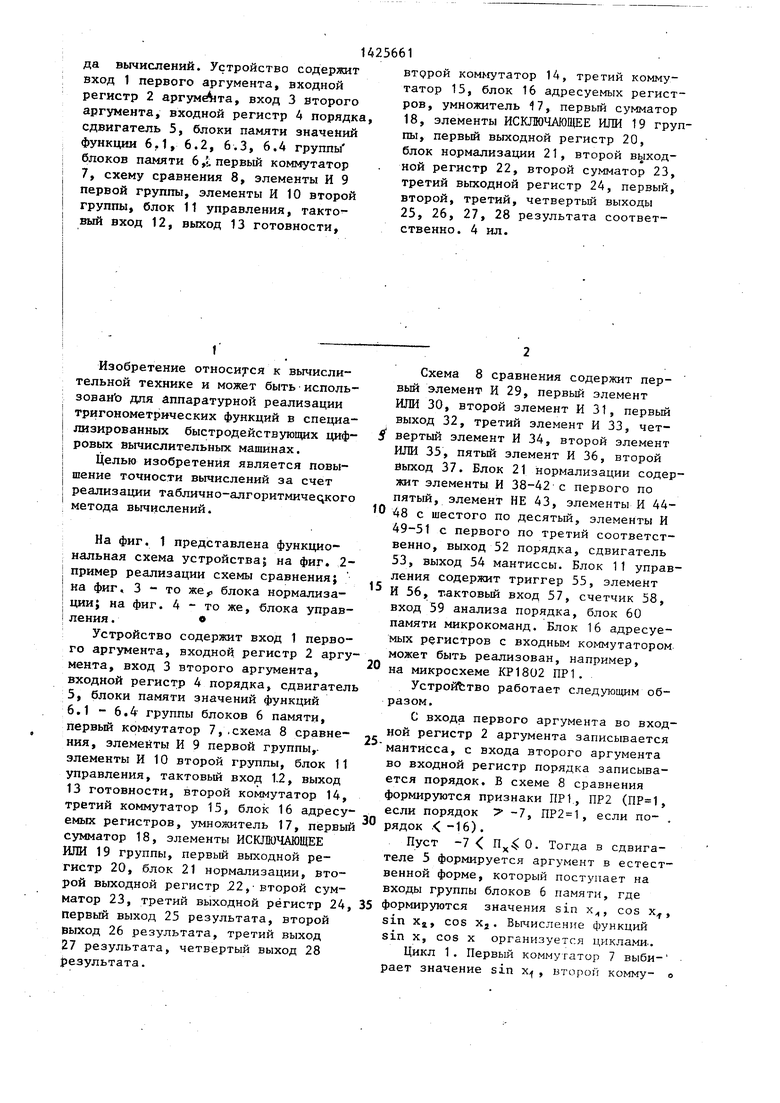

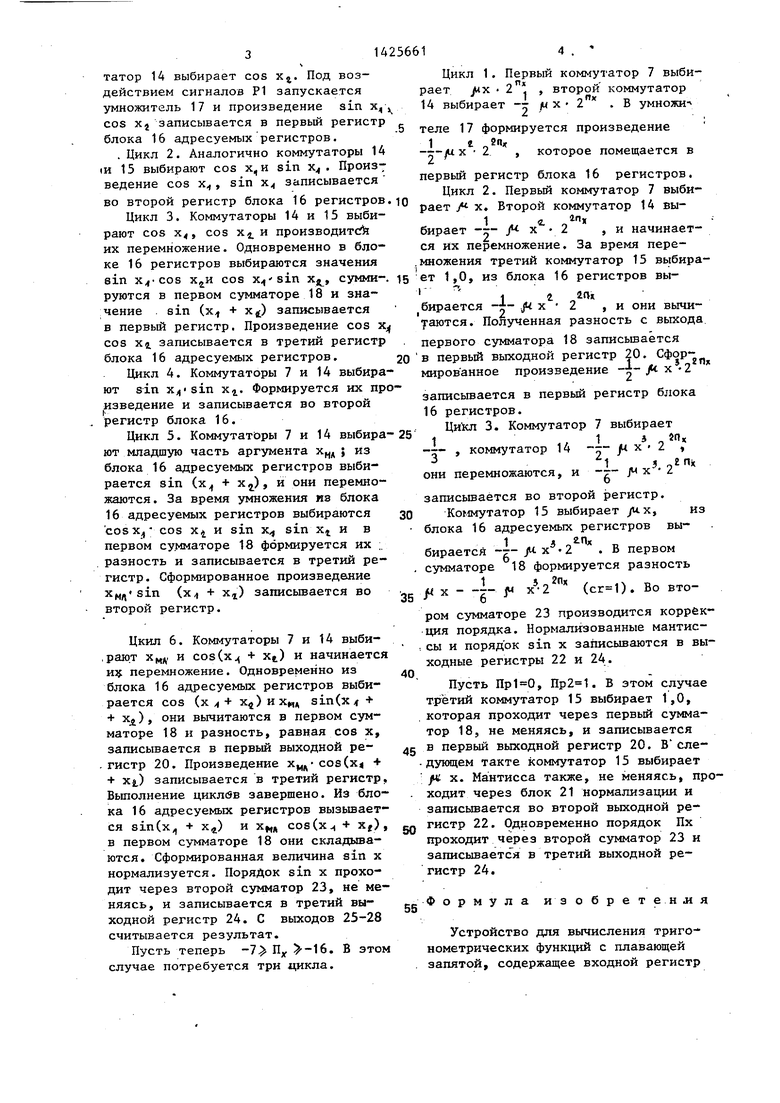

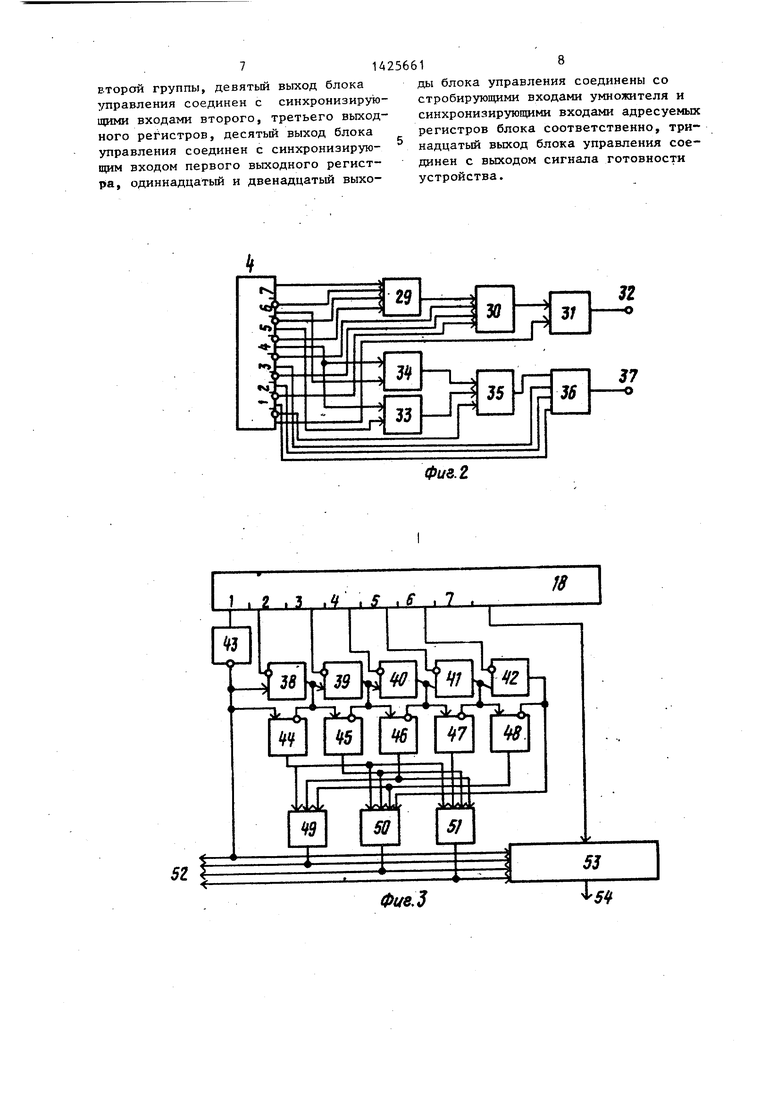

На фиг. 1 представлена функцио нальная схема устройства на фиг. 2пример реализации схемы сравнения;

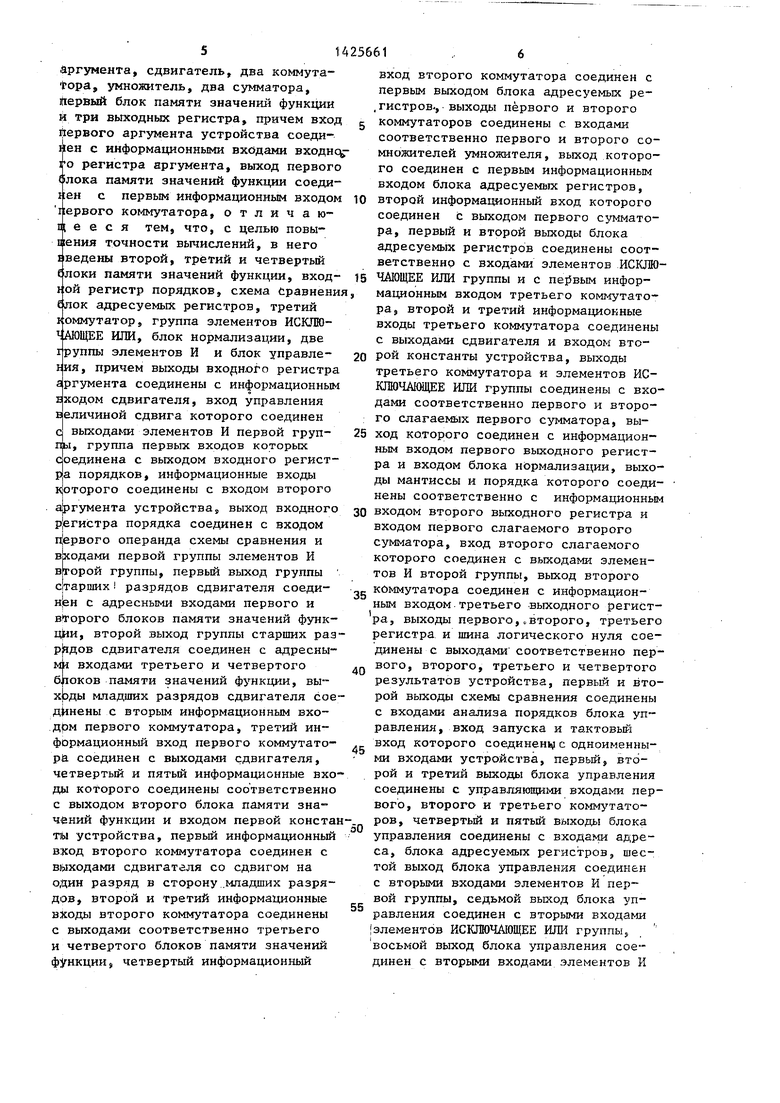

на фиг, 3 - то же блока нормализа1Ц1и; на фиг. 4 - то же, блока управления.

Устройство содержит вход 1 первого аргумента, входной регистр 2 аргумента, вход 3 второго аргумента, входной регистр 4 порядка, сдвигатель 5, блоки памяти значений функций 6,1 - 6.4 группы блоков 6 памяти, первый коммутатор 7,.схема 8 сравне- js ния, элементы И 9 первой группы,- элементы И 10 второй группы, блок 11 управления, тактовый вход 12, выход 13 готовности, второй коммутатор 14, третий коммутатор 15, блок 16 адресуемых регистров, умножитель 17, первый сумматор 18, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 19 группы, первый выходной регистр 20, блок 21 нормализации, второй выходной регистр J22,-второй сумматор 23, третий выходной регистр 24, 35 первый выход 23 результата, второй выход 26 результата, третий выход 27 результата, четвертый выход 28 результата.

30

0

0

s 5

0

Схема 8 сравнения содержит первый элемент И 29, первый элемент ИЛИ 30, второй элемент И 31, первый выход 32, третий элемент И 33, четвертый элемент И 34, второй элемент ШШ 35, пятый элемент И 36, второй Выход 37. Блок 21 нормализации содержит элементы И 38-42 с первого по пятый, элемент НЕ 43, элементы И 44- 48 с шестого по десятый, элементы И 49-51 с первого по третий соответственно, выход 52 порядка, сдвигатель 53, выход 54 мантиссы. Блок 11 управления содержит триггер 55, элемент И 56,, тактовый вход 57, счетчик 58, вход 59 анализа порядка, блок 60 памяти микрокоманд. Блок 16 адресуемых регистров с входным коммутатором может быть реализован, например, на микросхеме КР1802 ПР1.

УстройЬтво работает следующим образом.

С входа первого аргумента во входной регистр 2 аргумента записывается мантисса, с входа второго аргумента во входной регистр порядка записывается порядок. В схеме 8 сравнения формируются признаки ПР1, ПР2 (, если порядок 7 -7, ПР2 1, если по- , рядок . -16).

Пуст -7 П 0. Тогда в сдвига- теле 5 формируется аргумент в естественной форме, который поступает на входы группы блоков 6 памяти, где формируются значения sin х, cos х, sin Xj,, cos Хд. Вычисление функций sin X, cos X организуется циклами..

Цикл 1. Первый коммутатор 7 выби- рает значение sin х, второй комму- о

татор 14 выбирает cos х. Под воздействием сигналов Р1 запускается умножитель 17 и произведение sin х, cos Xj записывается в первый регистр блока 16 адресуемых регистров.

. Цикл 2. Аналогично коммутаторы 14 (И 15 выбирают cos х,и sin х. Произведение cos х, sin х записывается

во второй регистр блока 16 регистров

Цикл 3. Коммутаторы 14 и 15 выбирают cos х, cos Х4 и производите их перемножение. Одновременно в блоке 16 регистров выбираются значения sin cos Xjj, сумми-. руются в первом сумматоре 18 и значение sin (х + х) записывается в первый регистр, Произведение cos х cos Xi записывается в третий регистр блока 16 адресуемых регистров.

Цикл 4. Коммутаторы 7 и 14 выбирают sin X;( sin Xi. Формируется их произведение и записывается во второй регистр блока 16.

Цикл 5. Коммутаторы 7 и 14 выбира- ют младшую часть аргумента х ; из блока 16 адресуемых регистров выбирается sin (х + Xj), и они перемножаются. За время умножения из блока 16 адресуемых регистров выбираются COSX,,- cos х и sin х sin х и в первом сумматоре 18 формируется их ;. разность и записывается в третий регистр. Сформированное произведение (х + Хг) записьгоается во второй регистр.

Цкил 6. Коммутаторы 7 и 14 выби- ,рают х,д, и cos(x + Хе.) и начинается и перемножение. Одновременно из блока 16 адресуемых регистров выбирается cos (х 4 + Х{)ихи| sin(X;f + х), они вычитаются в первом сумматоре 18 и разность, равная сов х, записывается в первый выходной ре- гистр 20. Произведение соаСхл + + xj,) записывается в третий регистр, Выполнение циклбв завершено. Из блока 16 адресуемых регистров вызывается sin(x, + х) и Х| cos(x + Xj) , в первом сумматоре 18 они складываются. Сформированная величина sin х нормализуется. Порядок sin х проходит через второй сумматор 23, не меняясь, и записывается в третий вы- ходной регистр 24. С выходов 25-28 считывается результат.

Пусть теперь -7 П -16. В этом случае потребуется три цикла.

Цикл 1. Первый коммутатор 7 выбирает -2 , второй коммутатор 14 выбирает -- ju х 2 .В умножи-

теле 17 формируется произведение

1 е , -Г-/ЦХ 2 , которое помещается в

первый регистр блока 16 регистров.

Цикл 2. Первый коммутатор 7 выбирает / X, Второй коммутатор 14 выбирает --- J4- у. 2 , и начинается их перемножение. За время пере- .множения третий коммутатор 15 выбирает 1,0, из блока 16 регистров вы 1 1 ап убирается jU х 2 , и они вычищаются. Полученная разность с выхода

первого сумматора 18 записьшается в первый выходной регистр 20. Сформиров анное произведение /t х 2

записывается в первый регистр блока 16 регистров.

--- , коммутатор 14 --- х 2 «

.. . 1 „,..

Г 2

ОНИ перемножаются, и

записьшается во второй регистр.

Коммутатор 15 выбирает /.х, из блока 16 адресуемых регистров выбирается -7- JM. х 2 . В первом сумматоре 18 формируется разность

1 5 гпх Я X - -т- j« х-2

(). Во втором сумматоре 23 производится коррекция порядка. Нормалй зованные мантис- сы и порядок sin X записываются в выходные регистры 22 и 24.

Пусть , . В этом случае третий коммутатор 15 выбирает 1,0, которая проходит через первый сумматор 18, не меняясь, и записывается в первый выходной регистр 20. В сле- дукнцем такте коммутатор 15 выбирает /t X. Ма нтисса также, не меняясь, проходит через блок 21 нормализации и записывается во второй выходной регистр 22. Одновременно порядок Их проходит через второй сумматор 23 и записывается в третий выходной регистр 24.

ормула изобретения

Устройство для вычисления триго- нометрических функций с плавающей запятой, содержащее входной регистр

аргумента, сдвигатель, два коммутатора, умножитель, два сумматора, Первый блок памяти значений функции и три выходных регистра, причем вход йервого аргумента устройства соединен с информационными входами входнс го регистра аргумента, выход первого блока памяти значений функции соединен с первым информационным входом первого коммутатора, отличаю- П1 е е с я тем, что, с целью повы- п:ения точности вычислений, в него I ведены второй, третий и четвертый локи памяти значений функции, входной регистр порядков, схема Сравнени Елок адресуемых регистров, третий коммутатор, группа элементов ИСКЛЮ- :АЮЩЕЕ ИЛИ, блок нормализации, две группы элементов И и блок управления, причем выходы входного регистра аргзгмента соединены с информационным входом сдвигателя, вход управления в|еличиной сдвига которого соединен с выходами элементов И первой группы, группа первых входов которых с оединена с выходом входного регист- порядков, информационные входы KJoToporo соединены с входом второго

а|ргумента устройства, выход входного р|егистра порядка соединен с входом njepBoro операнда схемы сравнения и вЬсодами первой группы элементов И вггорой группы, первый выход группы С|тарших разрядов сдвигателя соеди- с адресными входами первого и второго блоков памяти значений функции, второй выход группы старших раз р|ядов сдвигателя соединен с адресными входами третьего и четвертого блоков памяти значений функции, вы- хЬды младших разрядов сдвигателя соединены с вторым информационным входом первого коммутатора, третий информационный вход первого коммутатора соединен с выходами сдвигателя, четвертый и пятый информационные входы которого соединены соответственно с выходом второго блока памяти значений функции и входом первой конста ты устройства, первый информационный вход второго коммутатора соединен с выходами сдвигателя со сдвигом на один разряд в сторону .младших разрядов, второй и третий информационные входы второго коммутатора соединены с выходами соответственно третьего и четвертого блоков памяти значений функции, четвертый информационный

0

5

вход второго коммутатора соединен с первым выходом блока адресуемых регистров., выходы первого и второго коммутаторов соединены с входами соответственно первого и второго сомножителей умножителя, выход которого соединен с первым информационным входом блока адресуемых регистров, второй информационный вход которого соединен с выходом первого сумматора, первый и второй выходы блока адресуемых регистров соединены соответственно с входами элементов ИСКЛЮ5 ЧАЮЩЕЕ ИЛИ группы и с пе15вым информационным входом третьего коммутатора, второй и третий информационные входы третьего коммутатора соединены с выходами сдвигателя и входом вто0 рой константы устройства, выходы

третьего коммутатора и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с входами соответственно первого и второго слагаемь1х первого сумматора, выход которого соединен с информационным входом первого выходного регистра и входом блока нормализации, выходы мантиссы и порядка которого соединены соответственно с информационным входом второго выходного регистра и входом первого слагаемого второго сумматора, вход второго слагаемого которого соединен с выходами элементов И второй группы, выход второго коммутатора соединен с информационным входом третьего -выходного регистра, выходы первого,.второго, третьего регистра и шина логического нуля соединены с выходами соответственно первого, второго, третьего и четвертого результатов устройства, первьй и второй выходы схемы сравнения соединены с входами анализа порядков блока управления, вход запуска и тактовьй вход которого соединен с одноименными входами устройства, первый, второй и третий выходы блока управления соединены с управ.ггаю1ци1 «и входами первого, второго и третьего коммутаторов, четвертый и пятый выходы блока управления соединены с входа № адреса, блока адресуемых регистров, шестой выход блока управления соединен с вторыми входами элементов И первой группы, седьмой выход блока управления соединен с вторыми входами (элементов ИСКЛЮЧАЮЩЕЕ ИЛИ rpynnbij восьмой выход блока управления соединен с вторыми входами элементов И

0

5

1

0

5

5

второй группы, девятый выход блока ;д1равления соединен с синхронизирую- щиьш входами второго, третьего выходного регистров, десятый выход блока управления соединен с синхронизирующим входом первого выходного регистра, одиннадцатый и двенадцатый выхо1 2.3 . .5 . f . 7 .

52

ды блока управления соединены со стробирующими входами умножителя и синхронизирующими входами адресуемых регистров блока соответственно, три надцатый выход блока управления соединен с выходом сигнала готовности устройства.

и

Фиг. 2

/(

0tf8,3

Фиъ.Ц

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1986-10-31—Подача