входами ключей группы, первым управляющим входом ключа, четвертый выход комбинационного блока управления соединен с информационным входом регистра и адресным входом дополнительного запоминающего блока, группа информационных выходов регистра через группу ключей и информационный выход регистра через ключ соединены с группой информационных входоввыходов дополнительного запоминающего блока и группой информационных входоввыходов операционного блока, вторые управляющие входы ключей группы и второй управляющий вход ключа соединены с пятым выходом комбинационного блока управления, шестой выход которого соединен с разрешающим входом дополнительного запоминающего блока.

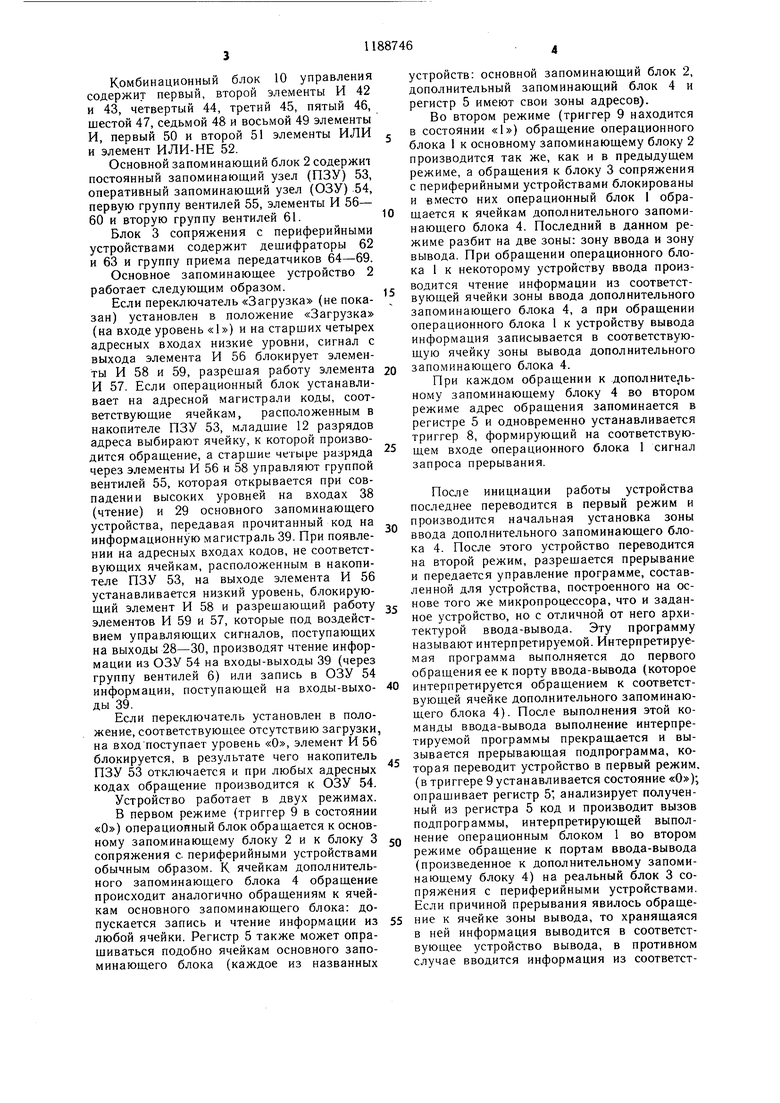

2. Устройство по п. 1, отличающееся тем, что комбинационный блок управления содержит восемь элементов И, два элемента ИЛИ и элемент ИЛИ-НЕ, причем первые входы первого и второго элементов И и шесть входов третьего элемента И образуют группу информационных входов комбинационного блока управления, при этом первый вход второго элемента И соединен с первым входом четвертого элемента И, первый вход пятого элемента И является первым входом комбинационного блока управления, первый вход шестого элемента И соединен с первым входом седьмого элемента И является вторым входом комбинационного блока управления, седьмой вход третьего элемента И

соединен с первым входом восьмого элемента И и является третьим входом комбинационного блока управления, второй вход первого элемента И соединен с вторыми входами второго и четвертого элементов И и является четвертым входом комбинационного блока управления, второй вход седьмого элемента И соединен с вторым входом восьмого элемента И и является пятым входом комбинационного блока управления, выход элемента ИЛИ-НЕ является первым выходом комбинационного блока управления, выход щестого элемента И является вторым выходом комбинационного блока управления, выход восьмого элемента И соединен с первым входом первого элемента ИЛИ и является третьим выходом комбинационного блока управления, выход второго элемента ИЛИ является четвертым выходом комбинационного блока управления, выход пятого элемента И является пятым выходом комбинационного блока управления, выход первого элемента ИЛИ является шестым выходом комбинационного блока управления, ыход четвертого элемента И соединен с вторыми входами пятого и шестого элементов И и первым входом элемента ИЛИ-НЕ, выход второго элемента И соединен с вторыми входами первого элемента ИЛИ и элемента ИЛИ-НЕ, первый и второй входы второго элемента ИЛИ соединены с выходами первого и седьмого элементов И соответственно, выход третьего элемента И соединен с третьими входами второго и четвертого элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство управления полупроводниковой памятью | 1986 |

|

SU1410098A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

1. УСТРОЙСТВО ВВОДА-ВЫВОДА С ИЗМЕНЯЕМОЙ А РХИТЕКТУРОЙ, содержащее операционный блок, основной запоминающий блок и блок сопряжения с периферийными устройствами, причем группа информационных входов-выходов операционного блока соединена с группой информационных входов-выходов основного запоминающего блока и блока сопряжения с периферийными устройствами, группа младших разрядов адресного выхода операционного блока соединена с группой младших разрядов адресного входа основного запоминающего блока и с группой адресных входов блока сопряжения с периферийными устройствами, группа старших разрядов адресного выхода операционного блока соединена с группой старщих разрядов адресного входа основного запоминающего блока, первый управляющий выход операционного блока соединен с входами чтения основного запоминающего блока и блока сопряжения с периферийными устройствами, второй управляющий выход операционного блока соединен с входами записи основного запоминающего блока и блока сопряжения с периферийными устройствами, отличающееся тем, что, с целью повышения гибкости обмена информацией с различными периферийными устройствами, в него введены комбинационный блок управления, дополнительный запоминающий блок, регистр, группа ключей, два элемента И, два триггера и ключ, причем группа информационных входов комбинационного блока управления соединена с группой старших разрядов адресного выхода операционного блока, первый управляющий выход которого соединен с первым входом комбинационного блока управления и входом чтения дополнительного запоминающего блока, вход записи которого соединен с вторым входом комбинационного блока управления и вторым управляющим выходом операционного блока, третий управляющий выход которого соединен с третьим входом комбинационного блока управления и первыми входами первого элемента И и второго элемента И, выход которого соединен с разрешающим входом основного запоминающеi го блока, разрещающий вход.блока сопряжения с периферийными устройствами со(Л единен с выходом первого элемента И, второй вход которого соединен с нулевым выходом первого триггера и четвертым входом комбинационного блока управления, единичный выход первого триггера соединен с пятым входом комбинационного блока управления, первый выход которого соединен с вторым входом второго элемента И, второй выход 00 комбинационного блока управления соединен 00 с нулевым входом второго триггера и синхровходом первого триггера, информацион4: ный вход которого соединен с одним из разрядов информационного выхода группы О5 операционного блока, вход запроса прерывания которого соединен с единичным выходом второго триггера, единичный вход которого соединен с третьим выходом комбинационного блока управления и управляющим входом регистра, группа информационных входов которого соединена с группой разрядов адресного выхода дополнительного запоминающего блока и группой младших разрядов адресного выхода операционного блока, при этом младший разряд группы адресных выходов операционного блока соединен с первыми управляющими

1

Изобретение относится к вычислительной технике и может быть использовано при создании микроэвм и систем на их основе, допускающих функциональную настройку системы ввода-вывода.

Цель изобретения - повышение гибкости обмена информацией с различными периферийными устройствами.

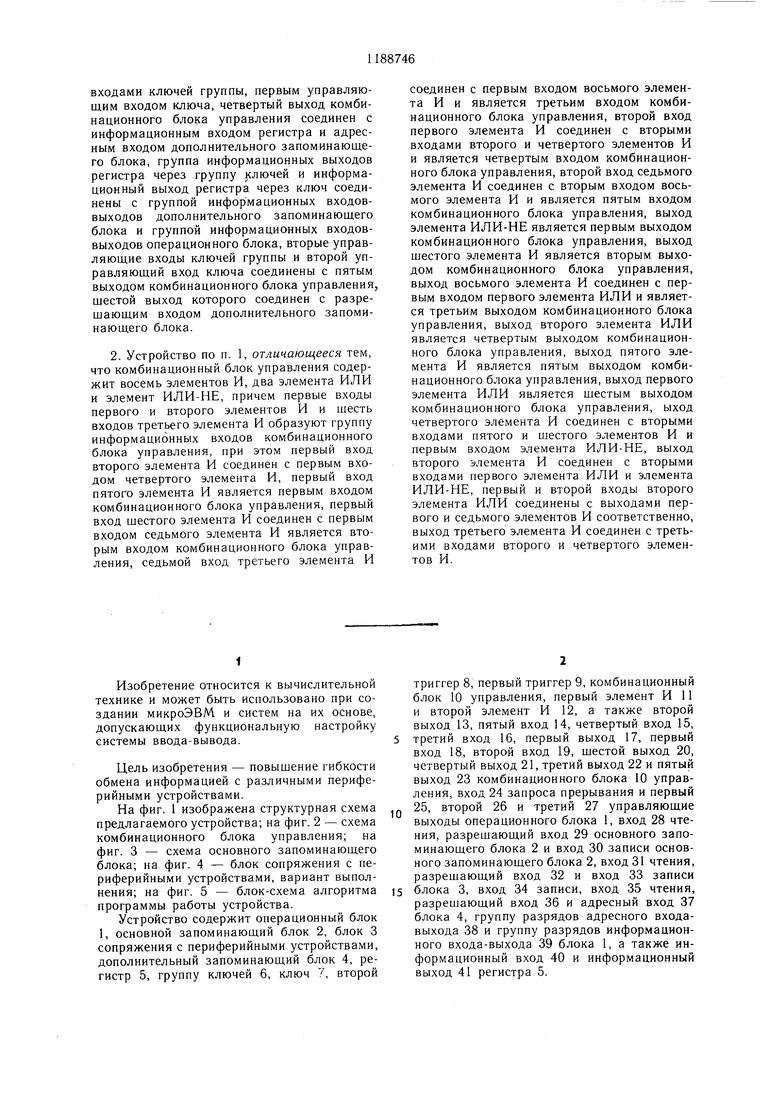

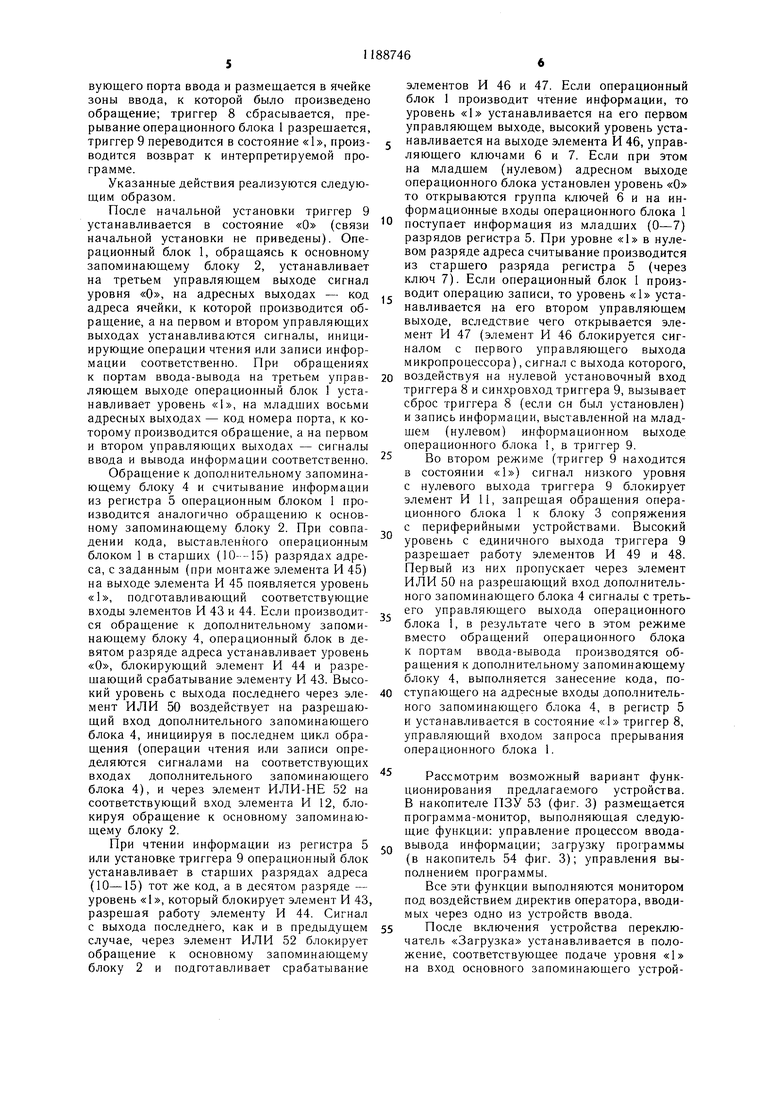

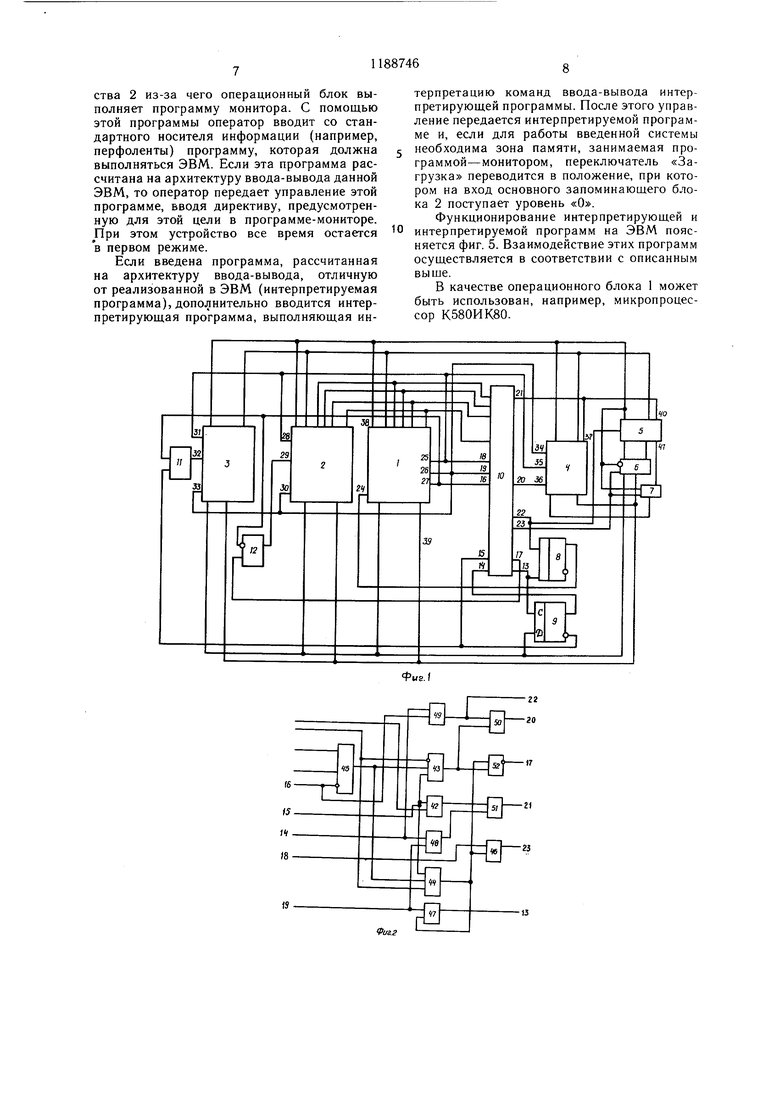

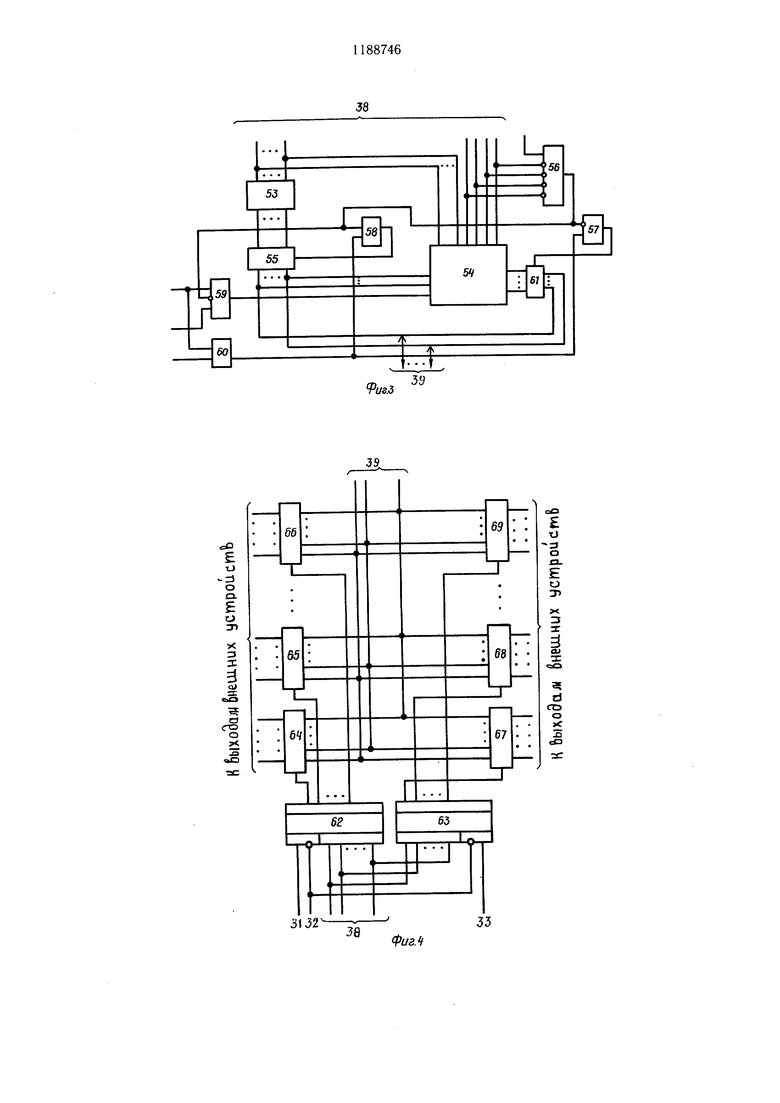

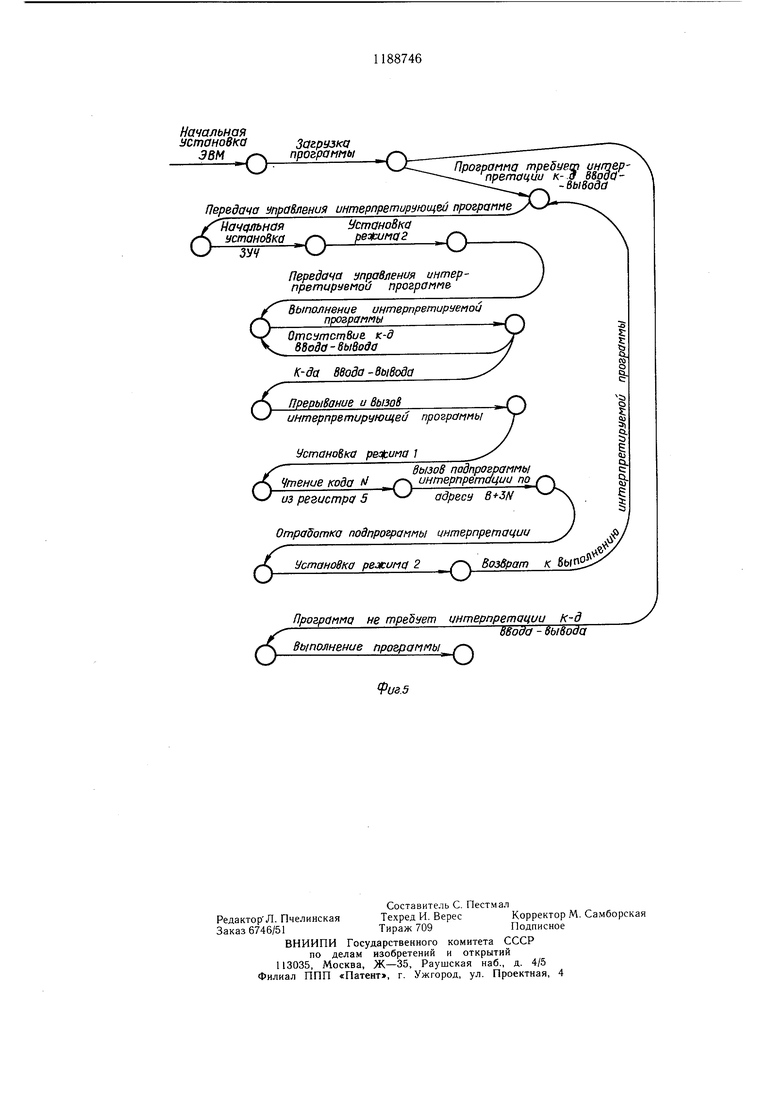

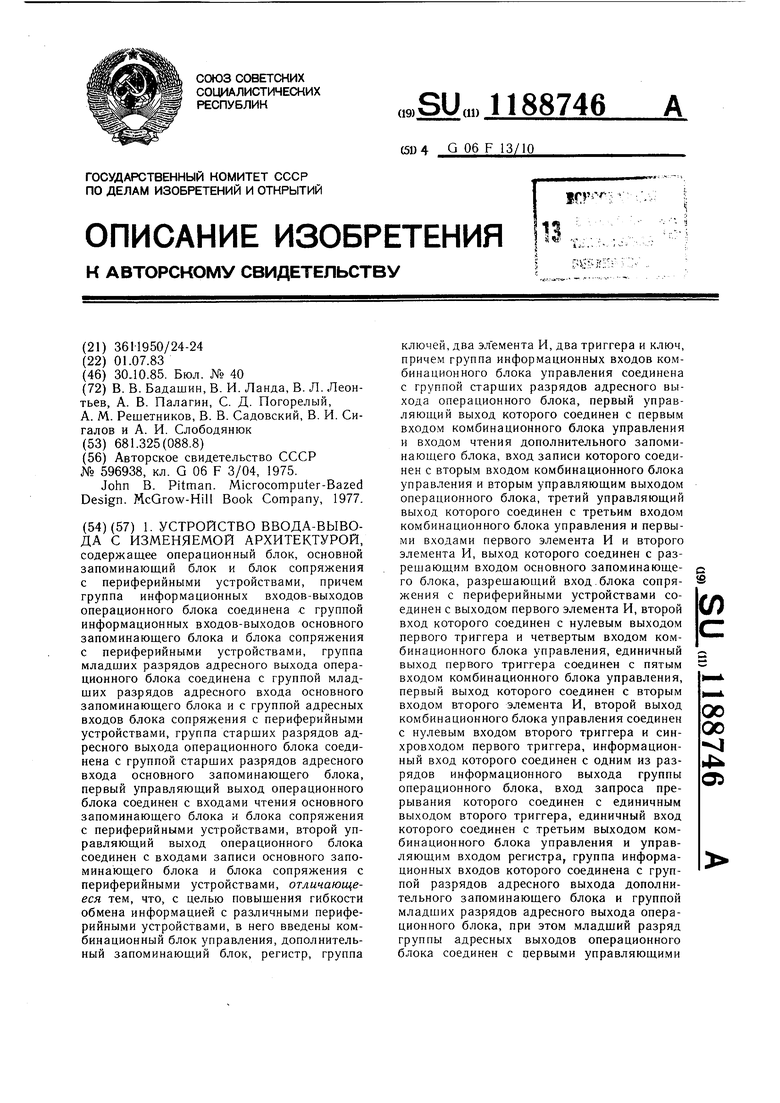

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - схема комбинационного блока управления; на фиг. 3 - схема основного запоминающего блока; на фиг. 4 - блок сопряжения с периферийными устройствами, вариант выполнения; на фиг. 5 - блок-схема алгоритма программы работы устройства.

Устройство содержит операционный блок 1, основной запоминающий блок 2, блок 3 сопряжения с периферийными устройствами, дополнительный запоминающий блок 4, регистр 5, группу ключей 6, ключ 7, второй

триггер 8, первый триггер 9, комбинационный блок 10 управления, первый элемент И 11 и второй элемент И 12, а также второй выход 13, пятый вход 14, четвертый вход 15,

третий вход 16, первый выход 17, первый вход 18, второй вход 19, шестой выход 20, четвертый выход 21, третий выход 22 и пятый выход 23 комбинационного блока 10 управления, вход 24 запроса прерывания и первый

25, второй 26 и третий 27 управляющие выходы операционного блока 1, вход 28 чтения, разрешающий вход 29 основного запоминающего блока 2 и вход 30 записи основного запоминающего блока 2, вход 31 чтения, разрешающий вход 32 и вход 33 записи

блока 3, вход 34 записи, вход 35 чтения, разрешающий вход 36 и адресный вход 37 блока 4, группу разрядов адресного входавыхода 38 и группу разрядов информационного входа-выхода 39 блока 1, а также информационный вход 40 и информационный выход 41 регистра 5.

Комбинационный блок 10 управления содержит первый, второй элементы И 42 и 43, четвертый 44, третий 45, пятый 46, шестой 47, седьмой 48 и восьмой 49 элементы И, первый 50 и второй 51 элементы ИЛИ и элемент ИЛИ-НЕ 52.

Основной запоминающий блок 2 содержит постоянный запоминающий узел (ПЗУ) 53, оперативный запоминающий узел (ОЗУ) -54, первую группу вентилей 55, элементы И 56- 60 и вторую группу вентилей 61.

Блок 3 сопряжения с периферийными

устройствами содержит дешифраторы 62

и 63 и группу приема передатчиков 64-69.

Основное запоминающее устройство 2

работает следующим образом.

Если переключатель «Загрузка (не показан) установлен в положение «Загрузка (на входе уровень «1) и на старших четырех адресных входах низкие уровни, сигнал с выхода элемента И 56 блокирует элементы И 58 и 59, разрешая работу элемента И 57. Если операционный блок устанавливает на адресной магистрали коды, соответствующие ячейкам, расположенным в накопителе ПЗУ 53, младшие 12 разрядов адреса выбирают ячейку, к которой производится обращение, а старшие четыре разряда через элементы И 56 и 58 управляют группой вентилей 55, которая открывается при совпадении высоких уровней на входах 38 (чтение) и 29 основного запоминающего устройства, передавая прочитанный код на информационную магистраль 39. При появлении на адресных входах кодов, не соответствующих ячейкам, расположенным в накопителе ПЗУ 53, на выходе элемента И 56 устанавливается низкий уровень, блокирующий элемент И 58 и разрешающий работу элементов И 59 и 57, которые под воздействием управляющих сигналов, поступающих на выходы 28-30, производят чтение информации из ОЗУ 54 на входы-выходы 39 (через группу вентилей 6) или запись в ОЗУ 54 информации, поступающей на входы-выходы 39.

Если переключатель установлен в положение, соответствующее отсутствию загрузки, на вход поступает уровень «О, элемент И 56 блокируется, в результате чего накопитель ПЗУ 53 отключается и при любых адресных кодах обращение производится к ОЗУ 54. Устройство работает в двух режимах. В первом режиме (триггер 9 в состоянии «О) операционный блок обращается к основному запоминающему блоку 2 и к блоку 3 сопряжения с периферийными устройствами обычным образом. К ячейкам дополнительного запоминающего блока 4 обращение происходит аналогично обращениям к ячейкам основного запоминающего блока: допускается запись и чтение информации из любой ячейки. Регистр 5 также может опрашиваться подобно ячейкам основного запоминающего блока (каждое из названных

устройств: основной запоминающий блок 2, дополнительный запоминающий блок 4 и регистр 5 имеют свои зоны адресов).

Во втором режиме (триггер 9 находится в состоянии «1) обращение операционного блока 1 к основному запоминающему блоку 2 производится так же, как и в предыдущем режиме, а обращения к блоку 3 сопряжения с периферийными устройствами блокированы и вместо них операционный блок 1 обращается к ячейкам дополнительного запоминающего блока 4. Последний в данном режиме разбит на две зоны: зону ввода и зону вывода. При обращении операционного блока 1 к некоторому устройству ввода произ. водится чтение информации из соответствующей ячейки зоны ввода дополнительного запоминающего блока 4, а при обращении операционного блока 1 к устройству вывода информация записывается в соответствующую ячейку зоны вывода дополнительного

0 запоминающего блока 4.

При каждом обращении к дополнительному запоминающему блоку 4 во втором режиме адрес обращения запоминается в регистре 5 и одновременно устанавливается триггер 8, формирующий на соответствующем входе операционного блока 1 сигнал запроса прерывания.

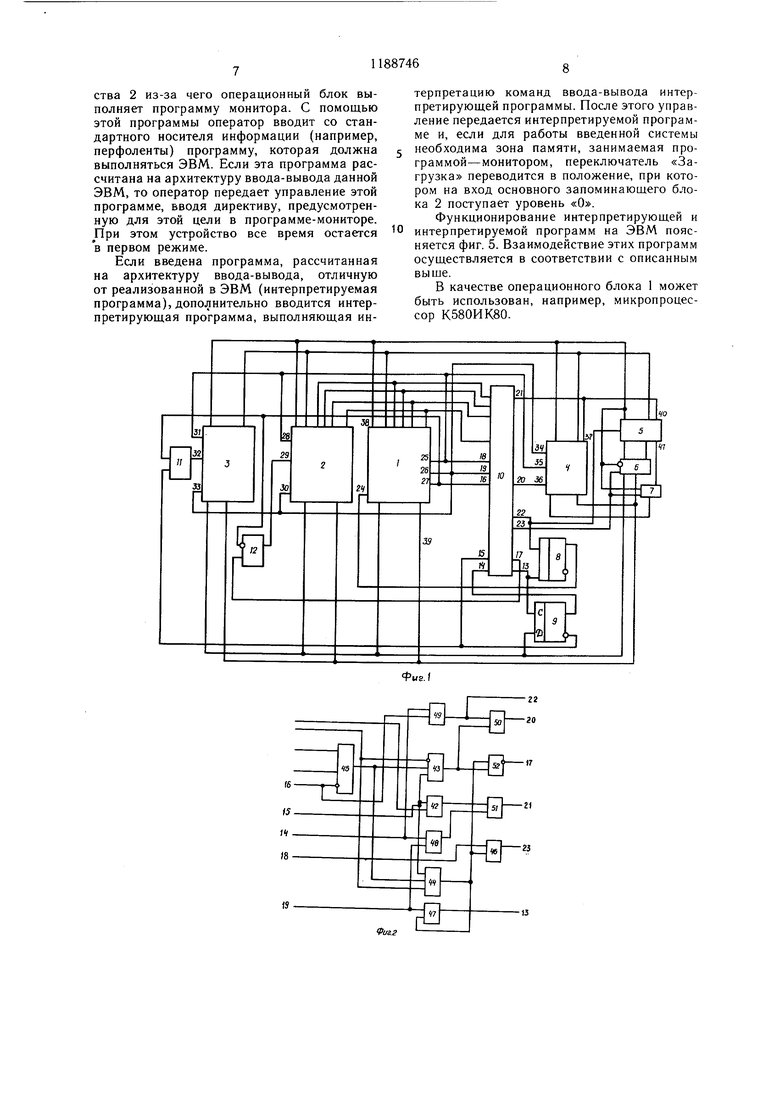

После инициации работы устройства последнее переводится в первый режим и производится начальная установка зоны ввода дополнительного запоминающего блока 4. После этого устройство переводится на второй режим, разрешается прерывание и передается управление программе, составленной для устройства, построенного на ос нове того же микропроцессора, что и заданное устройство, но с отличной от него архитектурой ввода-вывода. Эту программу называют интерпретируемой. Интерпретируемая программа выполняется до первого обращения ее к порту ввода-вывода (которое

0 интерпретируется обращением к соответствующей ячейке дополнительного запоминающего блока 4). После выполнения этой команды ввода-вывода выполнение интерпретируемой программы прекращается и вызывается прерывающая подпрограмма, которая переводит устройство в первый режим, (в триггере 9 устанавливается состояние «О); опрашивает регистр 5; анализирует полученный из регистра 5 код и производит вызов подпрограммы, интерпретирующей выполнение операционным блоком 1 во втором режиме обращение к портам ввода-вывода (произведенное к дополнительному запоминающему блоку 4) на реальный блок 3 сопряжения с периферийными устройствами. Если причиной прерывания явилось обращение к ячейке зоны вывода, то хранящаяся в ней информация выводится в соответствующее устройство вывода, в противном случае вводится информация из соответствующего порта ввода и размещается в ячейке зоны ввода, к которой было произведено обращение; триггер 8 сбрасывается, прерывание операционного блока 1 разрещается, триггер 9 переводится в состояние «1, производится возврат к интерпретируемой программе.

Указанные действия реализуются следующим образом.

После начальной установки триггер 9 устанавливается в состояние «О (связи начальной установки не приведены). Операционный блок 1, обращаясь к основному запоминающему блоку 2, устанавливает на третьем управляющем выходе сигнал уровня «О, на адресных выходах - код адреса ячейки, к которой производится обращение, а на первом и втором управляющих выходах устанавливаются сигналы, инициирующие операции чтения или записи информации соответственно. При обращениях к портам ввода-вывода на третьем управляющем выходе операционный блок 1 устанавливает уровень «1, на младщих восьми адресных выходах - код номера порта, к которому производится обращение, а на первом и втором управляющих выходах - сигналы ввода и вывода информации соответственно.

Обращение к дополнительному запоминающему блоку 4 и считывание информации из регистра 5 операционным блоком 1 производится аналогично обращению к основному запоминающему блоку 2. При совпадении кода, выставленного операционным блоком 1 в старщих (10-15) разрядах адреса, с заданным (при монтаже элемента И 45) на выходе элемента И 45 появляется уровень «1, подготавливающий соответствующие входы элементов И 43 и 44. Если производится обращение к дополнительному запоминающему блоку 4, операционный блок в девятом разряде адреса устанавливает уровень «О, блокирующий элемент И 44 и разрешающий срабатывание элементу И 43. Высокий уровень с выхода последнего через элемент ИЛИ 50 воздействует на разрещающий вход дополнительного запоминающего блока 4, инициируя в последнем цикл обращения (операции чтения или записи определяются сигналами на соответствующих входах дополнительного запоминающего блока 4), и через эле.мент ИЛИ-НЕ 52 на соответствующий вход элемента И 12, блокируя обращение к основному запоминающему блоку 2.

При чтении информации из регистра 5 или установке триггера 9 операционный блок устанавливает в старщих разрядах адреса (10-15) тот же код, а в десятом разряде - уровень «1, который блокирует элемент И 43 разрещая работу элементу И 44. Сигнал с выхода последнего, как и в предыдущем случае, через элемент ИЛИ 52 блокирует обращение к основному запоминающему блоку 2 и подготавливает срабатывание

элементов И 46 и 47. Если операционный блок 1 производит чтение информации, то уровень «1 устанавливается на его первом управляющем выходе, высокий уровень устанавливается на выходе элемента И 46, управляющего ключами 6 и 7. Если при этом на младщем (нулевом) адресном выходе операционного блока установлен уровень «О то открываются группа ключей 6 и на информационные входы операционного блока 1 поступает информация из младщих (0-7) разрядов регистра 5. При уровне «1 в нулевом разряде адреса считывание производится из старщего разряда регистра 5 (через ключ 7). Если операционный блок 1 производит операцию записи, то уровень «1 устанавливается на его втором управляющем выходе, вследствие чего открывается элемент И 47 (элемент И 46 блокируется сигналом с первого управляющего выхода микропроцессора), сигнал с выхода которого, воздействуя на нулевой установочный вход триггера 8 и синхровход триггера 9, вызывает сброс триггера 8 (если он был установлен) и запись информации, выставленной на младше.м (нулевом) информационно.м выходе операционного блока 1, в триггер 9.

Во втором режиме (триггер 9 находится в состоянии «1) сигнал низкого уровня с нулевого выхода триггера 9 блокирует элемент И 11, запрещая обращения операционного блока 1 к блоку 3 сопряжения с периферийными устройствами. Высокий уровень с единичного выхода триггера 9 разрещает работу элементов И 49 и 48. Первый из них пропускает через элемент ИЛИ 50 на разрешающий вход дополнительного запоминающего блока 4 сигналы с третьего управляющего выхода операционного блока 1, в результате чего в этом режиме вместо обращений операционного блока к портам ввода-вывода производятся обращения к дополнительному запоминающему блоку 4, выполняется занесение кода, поступающего на адресные входы дополнительного запоминающего блока 4, в регистр 5 и устанавливается в состояние «1 триггер 8, управляющий входом запроса прерывания операционного блока 1.

Рассмотрим возможный вариант функционирования предлагае.мого устройства. В накопителе ПЗУ 53 (фиг. 3) размещается программа-монитор, выполняющая следующие функции: управление процессом вводавывода информации; загрузку программы (в накопитель 54 фиг. 3); управления выполнением программы.

Все эти функции выполняются монитором под воздействием директив оператора, вводимых через одно из устройств ввода.

Поате включения устройства переключатель «Загрузка устанавливается в положение, соответствующее подаче уровня «1 на вход основного запоминающего устройства 2 из-за чего операционный блок выполняет программу монитора. С помощью этой программы оператор вводит со стандартного носителя информации (например, перфоленты) программу, которая должна выполняться ЭВМ. Если эта программа рассчитана на архитектуру ввода-вывода данной ЭВМ, то оператор передает управление этой программе, вводя директиву, предусмотренную для этой цели в программе-мониторе. При этом устройство все время остается °в первом режиме.

Если введена программа, рассчитанная на архитектуру ввода-вывода, отличную от реализованной в ЭВМ (интерпретируемая программа), дополнительно вводится интерпретирующая программа, выполняющая интерпретацию команд ввода-вывода интерпретирующей программы. После этого управление передается интерпретируемой программе и, если для работы введенной системы

необходима зона памяти, занимаемая программой-монитором, переключатель «Загрузка переводится в положение, при котором на вход основного запоминающего блока 2 поступает уровень «О.

Функционирование интерпретирующей и

интерпретируемой программ на ЭВМ поясняется фиг. 5. Взаимодействие этих программ осуществляется в соответствии с описанным выше.

В качестве операционного блока 1 может быть использован, например, микропроцессор К580ИК80.

3iJ2

33

ФигЛ Начальная установка Загрузка програппы О Передача Управления интерпретирующей програпме НачальнаяУстановка установка г режима 2 / Ч Передача управления интерпретируемой программе Вьтолнение интерпретируемой программы Отсутствие к-д дВода-вывода К-да Ввода-Вывода бПрерывание и ВызоВ интерпретир ющеи программы Устаноека ре4:има 7 Чтение кода А/ / интерпретации п из регистру 5 - офесу Отработка подпрограммы интерпретаци

6Установка режима 2

Программа не требует (jHmepnpemat4uu к-д

выполнение программы / вызов подпрограмм

.

Возврат к fibiggj

-О

ввода - вывода ы о и

| Система для сопряжения терминальных устройств с вычислительной машиной | 1975 |

|

SU596938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| John В | |||

| Pitman | |||

| Microcomputer-Bazed Design | |||

| McGrow-Hil Book Company, 1977. | |||

Авторы

Даты

1985-10-30—Публикация

1983-07-01—Подача