00

фие.1

Изобретение относится к полупро- водниковым запоминающим устройствам (ЗУ) и может быть использовано при создании устройств управления динамическими ОЗУ.

Цель изобретения - упрощение -устройства.

На фиг. 1 представлена функциональная схема предлагаемого устрой- CTBaJ на фиг. 2-4 - примеры реализации формирователя, счетчика адресовi регенерации и блока ввода адреса соответственно; на фиг. 5 и 6 - карта распределения памяти и адресных вхо- дов и выходов блока постоянной памяти,

Устройство содержит блоки ввода адреса 1 и данных 2, формирователь 3, первую и вторую группы генерато- ров 4 и 5 импульсов, первую и вторую группы элементов И 6 и 7, первый 8 и второй 9 элементы Р1ЛИ, счетчик 10 адресов регенерации, триггер 11, шифратор 12, блок 13 постоянной памяти (ПЗУ), регистр 14 и элемент И 15.

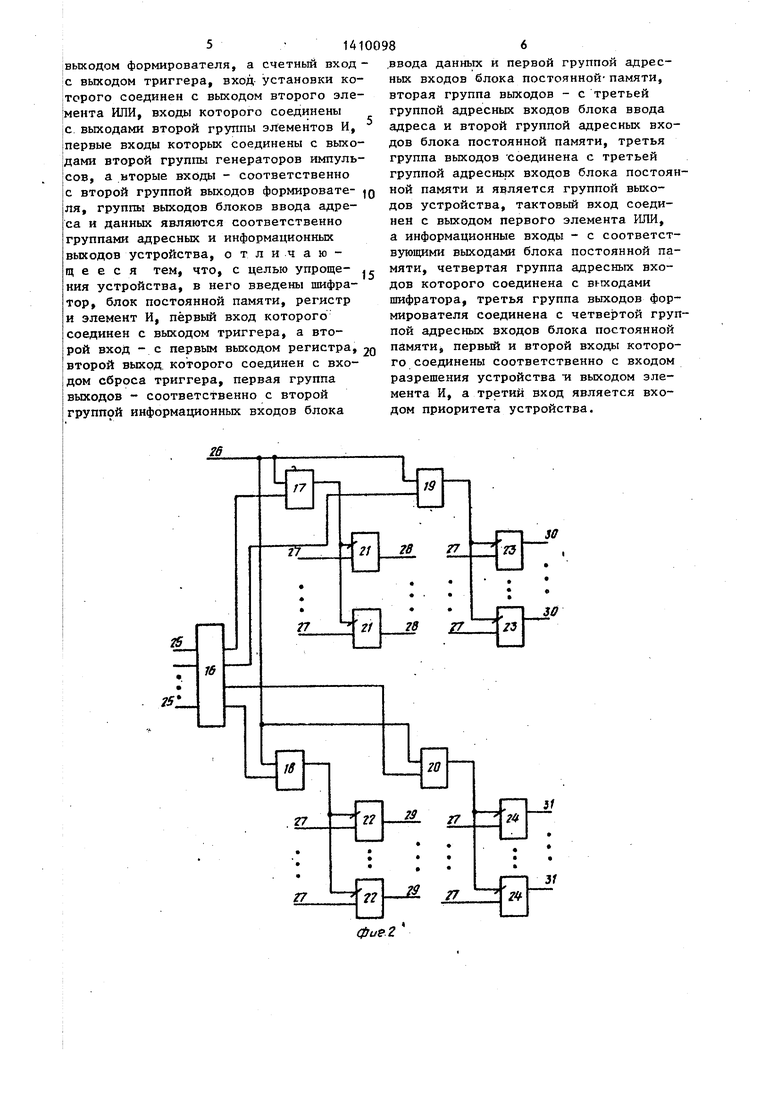

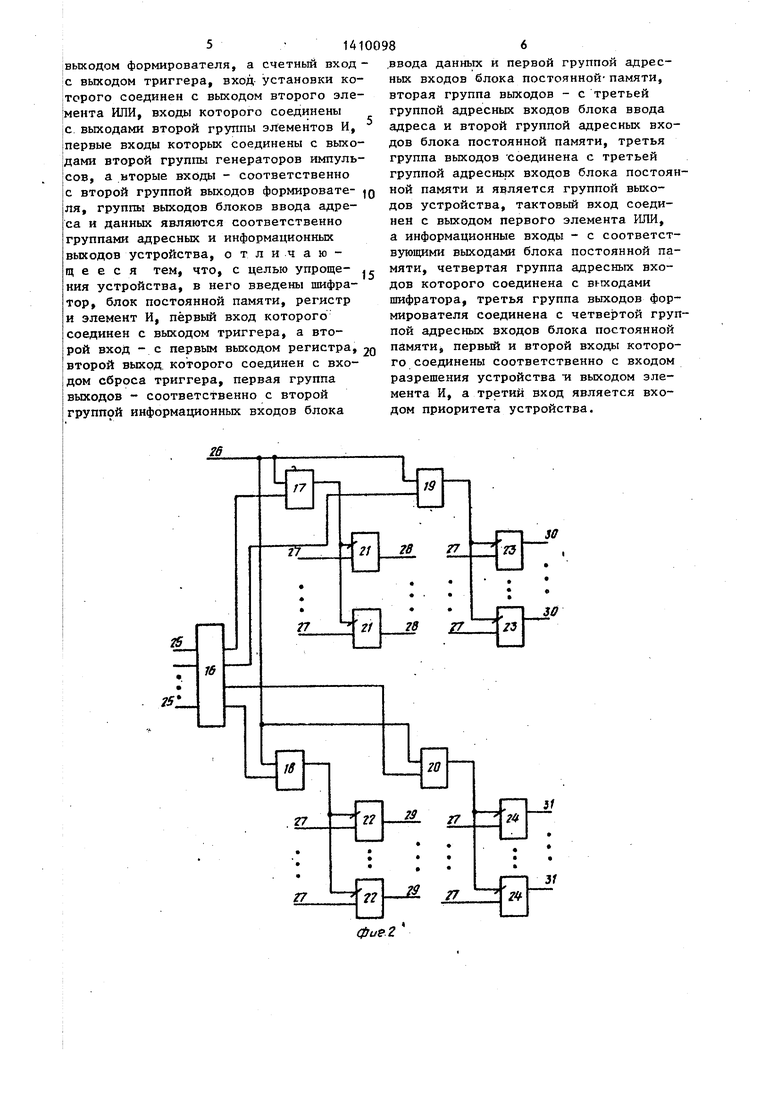

Формирователь 3 содержит селектор 16, элементы И 17 - 20 и D-триггеры 21 - 24, при этом входы 25 селектора 16 являются адресными входами устрой ства, вход 26 - входом разрешения, а входы 27 - информационными входами устройства, выходы 28 D-триггеров 21 подключаются к вторым входам элемента ИЛИ 8, выходы 29 D-триггеров 22 - к четвертой группе адресных входов блока 13 или ПЗУ, выходы 30 D-триггеров 23 - к входам установки счетчика 10 адресов регенерации, выходы 31 jD-триггеров 24 к вторым входам эле Центов И 7. Формирователь 3 осуществ пяет начальную установку устройства b зависимости от применяемого типа (полупроводниковой памяти (ПП).

Счетчик 10 адресов регенерации Кфиг. 3) содержит три двоичных четырехразрядных счетчика 32, элементы И 33 - 36 и элемент ИЛИ 37, вход 38 первого счетчика подключен Ц выходу триггера 11 регенерации, входы 39 счетчика 10 адресов регене- |рации подключены -к выходам 30 форми- )ователя 3, выходы 40 подключены к торой группе входов блока 1 ввода адреса.

В состав блока 1 ввода адреса {{фиг. 4) входят мультиплексоры 41, Имеющие организацию 3x1, где к входам 42 подключены входы устройства.

соответствующие младшей подовине адреса, к входам 43 подключены входы устройства, соответствующие старшей половине адреса, к входам 44 подключены выходы 40 счетчика 10 адресов регенерации, вьдходы 45 являются выходами устройства и подключены к адресным входам ПП. Входы 46 подключены к второй группе выходов регистра 14 и определяют очередность подключения младшей половины адреса, старшей половины адреса или адреса регенерации к адресным входам Ш1.

На фиг. 5 представлена карта распределения памяти блока 13, в качестве которого можно использовать, например, ПЗУ с организацией 2048х х8 бит. Адресные зоны 47, 48 и 49 содержат информацию, управляющую Ш1 раз:шчного типа, адресные зоны 50, 51 и 52 - наборы слов, управляющие режимом записи, адресные зоны 53, 54 и 55 - наборы слов, управляющие режимом чтения, а адресные зоны 56, 57 и 58 - наборы слов, управляющие режимом регенерации.

- На фиг. 6 представлено распределение адресных входов и выходов блока 13. Старшие разряды 59 адресного слова осуществляют выбор области управляющих слов блока 13, предназна- ченных для управления определенным типом ПП, при этом количество адресных входов 59 определяется из формулы

L + l.

где L - количество адресных вхо- ,

дов 59;

р - количество типов управляемой ПП.

Разряды 60 адресного слова осуществляют выбор области управляющих слов ПЗУ 13, соответствующей определенному режиму управления ПП - Запись, Чтение, Регенерация, при этом количество адресных входов 60 определяется по аналогичной формуле.

Младшие разряды 61 адресного слова осуществляют выбор очередного управляющего слова из блока 13, соответствующего определенному такту выполняемого режима управления ПП.

Выходы 62 блока 13 подключаются к второй группе входов регистра 14, который представляет собой регистр с параллельным занесением информации по стробу.

Устройство функционирует следующим образом.

Перед началом работы с ПП производится настройка устройства управления на определенный тип накопителя, для чего в формирователь 3 по сигналам Запись, поступающим на вход разрешения в соответствии с поступающими на группу адресных входов адресами, выбирающими группы триггеров 21 - 24, записывается через группу информационных входов управляющая информация, определяющая соответственно рабочую частоту ПП, тип ПП, максимальный адрес регенерации и частоту регенерации. Сигнал Разрешение чтения, поступающий на первый вход шифратора 12, выбирает в ПЗУ 13 область памяти, соответствующую режиму Чтение того типа ПП, который выбран формирователем 3, и с выхода ПЗУ 13 в регистр 14 первое управляющее слово записывается по тактовому сигналу, поступающему на первый вход регистра 14 от элемента ИЛИ 8. Управляющее слово содержит сигналы управления ПП, сигналы управления блоком 1 ввода адреса и блоком 2 ввода данных и сигналы управления режимом регенерации, причем сигналы управления ПП, блоком 1 ввода и блоком 2 являются одновременно сигналами, поступающими на третьи, четвертые и пятые входы ПЗУ

13и выбирающие из ПЗУ 13 очередное управляющее слово, которое записьша- ется в регистр 14 по следующему тактовому сигналу, поступающему от эле- |мента ИЛИ 8. С пятого выхода регистра

14на второй вход элемента И 15 выдается сигнал, запрещающий прохождение сигнала запроса регенерации с выхода триггера 11. Триггер 11 регенерации устанавливается по первому входу сигналом, проходящим через элементы И 7 и ИЛИ 9 от генератора 5.

Последнее управляющее слово режима Чтение разрешает прохождение сигнала Регенерация с выхода триггера 11 регенерации через элемент И 15 на вход приоритета шифратора 12 в результате чего независимо от управляющих сигналов Запись или Чтение на первом или втором входах шифратора 12 устройство выдает в ПП управляющие сигналы, соответствуняцие режиму регенерации, так как в ПЗУ 13 выбирается область управляющих слов

режима регенерации, С выхода триггера 11 на второй вход счетчика 10 поступает сигнал увеличения адреса

регенерации, на единицу. Адрес регенерации с выходов счетчика 10 поступает на вторую группу входов счетчика 10, который по управляющим сигналам, поступающим на третью группу входов

с вторьк выходов регистра 14, передает этот адрес на адресные входы : ПП. Последнее управляющее слово режима регенерации содержит сигнал сброса триггера 11, поступающий на его

BTOpo i вход с четвертого выхода регистра 14.

При обращении к другому типу ПП производится настройка устройства путем настройки формирователя 3, т.е.

при этом в группы триггеров 21 - 24 записывается управляющая информация, определяющая требуемую рабочую частоту накопителя, соответствующую данному типу ПП, требуемый максимальный адрес регенерации и требуемую частоту регенерации.

Формула изобретения

Устройство управления полупроводниковой памятью, содержащее формирователь, блоки ввода адреса и данных, первую и вторую группы генераторов импульсоэ, первый и второй элементы

ИЛИ, первую и вторую группу элементов И, счетчик адресов регенерации, триггер, причем группа адресных, входов формирователя объединена с первой группой адресных входов блока .

ввода адреса и является группой адресных входов устройства, группа информационных входов формирователя, соответственно объединенных с первой группой информационных входов блока ввода

данных, является группой информацион- |ных входов устройства, вход разрешения формирователя является входом разрешения записи устройства, пер-- вая группа выходов формирователя соединена соответственно с первыми входами Элементов И первой группы, вторые входы которых соединены с срот- ветствующими выходами первой группы генераторов импульсов, а выходы соединены с входами первого элемента 1ШИ, вторая группа адресных входов блока ввода адреса соединена с выходами счетчика адресов регенерации, вход установки которого соединен с первым

|выходом формирователя, а счетный вход - с выходом триггера, вход установки ко- iTcporo соединен с выходом второго эле- |мента ИЛИ, входы которого соединены с выходами второй группы элементов И, первые входы которых соединены с выходами второй группы генераторов импульсов, а вторые входы - соответственно

с второй группой выходов форМИрОВате- JQ

ля, группы выходов блоков ввода адреса и данных являются соответственно группами адресных и информационных выходов устройства, отличающееся тем, что, с целью упроще- . кия устройства, в него введены шифратор, блок постоянной памяти, регистр и элемент И, первый вход которого соединен с выходом триггера, а второй вход - с первым выходом регистра, 2Q второй выход которого соединен с входом сброса триггера, первая группа выходов - соответственно с второй группой информационных входов блока

.ввода данных и первой группой адресных входов блока постоянной- памяти, вторая группа выходов - с третьей группой адресных входов блока ввода адреса и второй группой адресных входов блока постоянной памяти, третья группа выходов соединена с третьей группой адресньпс входов блока постоянной памяти и является группой выходов устройства, тактовый вход соединен с выходом первого элемента ИЛИ, а информационные входы - с соответствующими выходами блока постоянной памяти, четвертая группа адресных входов которого соединена с выходами шифратора, третья группа выходов формирователя соединена с четвертой группой адресных входов блока постоянной памяти, первый и второй входы которого соединены соответственно с входом разрешения устройства и выходом элемента И, а третий вход является входом приоритета устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Имитатор локальной шины микропроцессора | 1987 |

|

SU1644144A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

Изобретение относится к полупроводниковым запоминающим устройствам (ЗУ) и может быть использовано при создании устройств управления динамическими ОЗУ. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет обеспечения возможности автоматической подстройки устройства управления Ш1 с ячейками на МДП-транзисторах с различными временными соотношениями между управляющими сигналами, различным количеством управляющих входов, различными режимами работы, введением в устройство шифратора 12, блока 13 постоянной памяти, регистра 14, элемента И 15. Устройство содержит блоки 1 , 2 ввода адреса и данных соответственно, формирователь 3, генераторы 4 и 5, элементы И 6,7, злемен- ты ИЛИ 8,9, счетчик 10 адресов регенерации, триггер 11, шифратор 12, блок 13, регистр 14. 6 ил. (Л G

JSl

фие2

J

Ъ9 I

0

37

5

фиг.

cpu.6

| Старое Ф.Г., Крайзмер Л.П | |||

| Полупроводниковые ЗУ, Л.: Энергия, 1973, с | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Устройство для управления полупроводниковой памятью | 1977 |

|

SU746515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-04-22—Подача