блок коррекции ошибок, входы первой группы которого соединены с входами первого блока формирователей четности и входами первой группы первого коммутатора, входы которого соединены с выходами блока коррекции ошибок, входы второй группы которого соединены с входами первого блока формирователей четности и входами первой группы первого коммутатора, входы которого соединены с выходами блока коррекции ошибок, входы второй группы которого соединены с выходами второго коммутатора, управляюший вход которого является первым управляюшим входом устройства, а выходы первой и второй групп соединены с выходами соответственно первого блока сравнения и выходами первой группы дешифратора, выходы второй группы которого являются контрольными выходами устройства, а входы соединены с выходами второго блока сравнения, выходы блоков контроля соединены с входами второго блока формирователей четности, выходы первого блока формирователей четности соединены с входами третьего коммутатора и входами первой группы первого блока сравнения, выходы второго блока формирователей четности соединены с входами четвертого коммутатора и входами первой группы второго блока сравнения, входы второй группы которого соединены соответственно с входами и выходами четвертого коммутатора и входами и выходами контрольных разрядов первой группы накопителя, входы и выходы контрольных разрядов второй группы которого соединены с входами второй группы первого блока сравнения и входами и выходами третьего коммутатора, управляющий вход которого соединен с управляющим входом четвертого коммутатора и является вторым управляющим входом устройства.

3.Устройство по п. 1 или 2, отличающееся тем, что в него введен элемент ИЛИ, входы которого соединены с выходами первого блока сравнения, а выход является дополнительным контрольным выходом устройства.

4.Запоминающее устройство с коррекцией ошибок, содержащее накопитель, информационные входы и выходы которого соединены соответственно с входами и выходами первой группы первого коммутатора, входы и выходы второй группы которого являются информационными входами и выходами устройства, управляющие входы первого коммутатора являются управляющими входами первой группы устройства, блок контроля, управляющие входы которого являются управляющими входами второй группы устройства, контрольные входы и выходы блока контроля соединены с контрольными входами и выходами первой группы устройства, а входы блока контроля являются контрольными выходами устройства, отличающееся тем, что, с целью увеличения информационной емкости устройства, в него введены блоки формирователей четности, блок сравнения, коммутаторы, с второго по четвертый, блок коррекции ощибок, входы первой группы которого соединены с входами первого и второго блоков формирователей четности и входами и выходами первого коммутатора, входы которого соединены с выходами блока коррекции ошибок, входы второй группы которого соединены с выходами второго коммутатора, управляющий вход которого является первым управляющим входом устройства, а входы первой и второй групп соединены соответственно с выходами первого блока сравнения и выходами и входами блока контроля, выходы первого блока формирователей четности соединены с входами третьего коммутатора и входами первой группы блока сравнения, входы второй группы которого соединены с входами и выходами третьего коммутатора и контрольными входами и выходами второй группы накопителя, выходы второго коммутатора соединены с входами четвертого коммутатора, входы и выходы которого соединены с входами второй группы второго коммутатора, управляющие входы третьего и четвертого коммутаторов являются соответственно вторым и третьим управляющими входами устройства.

5. Устройство по п. 4, отличающееся тем, что в него введен элемент ИЛИ, входы которого соединены с выходами блока сравнения, а выход является дополнительным контрольным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Устройство коррекции ошибок с контролем | 1983 |

|

SU1156076A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

1. Запоминающее устройство с коррекцией ошибок, содержащее накопитель, информационные входы и выходы которого соединены соответственно с входами и выходами первой группы первого коммутатора, входы и выходы второй группы которого являются информационными входами и выходами устройства, а управляющие входы первого коммутатора являются управляющими входами первой группы устройства, блок контроля, управляющие входы которого являются управляющими входами второй группы устройства, отличающееся тем, что, с целью увеличения информационной емкости устройства, в него введены блоки формирователей четности, коммутаторы, с второго по четвертый, блоки сравнения, блок коррекции ошибок, дешифратор, причем информационные входы и выходы накопителя соединены соответственно с входами первого и второго блоков формирователей четности, входами первой группы блока коррекции ошибок, выходы которого соединены с входами второй группы первого коммутатора, а входы второй группы соединены с выходами второго коммутатора, управляющий вход которого является первым управляющим входом устройства, а входы первой и второй групп соединены соответственно с выходами первого блока сравнения и выходами первой группы дешифратора, выходы второй группы которого являются контрольными выходами устройства, а входы соединены с выходами второго блока сравнения, входы первой и второй групп первого блока сравнения соединены соответственно с в.ходами и выходами третьего коммутатора, входы первой и второй групп второго блока сравнения соединены соответственно с входами и выходами четвертого коммутатора, управляющий вход третьего коммутатора соединен с управляющим входом четвертого коммутатора и является вторым управляющим входом устройства, входы блока контроля соединены с выходами второго блока формирователей четности, а выходы соединены с входами первой группы второго блока сравнения, входы второй € группы которого соединены с контрольными входами и выходами первой группы накопителя, контрольные входы и выходы второй группы которого соединены с входами второй группы первого блока сравнения, входы первой группы которого соединены с выходами первого блока формирователей четности. 2. Запоминающее устройство с коррекцией ошибок, содержащее накопитель, инфор00 мационные входы и выходы которого оо соединены соответственно с входами и выходами первой группы первого коммутаточ ра, входы и выходы второй группы которого являются информационными входами и выходами устройства, управляющие входы первого коммутатора являются управляющими входами первой группы устройства, группу блоков контроля, управляющие входы которых объединены и являются управляющими входами второй группы устройства, входы блоков контроля соединены с входами первой группы первого коммутатора, отличающееся тем, что, с целью увеличения инфор.мационной емкости устройства, в него введены блоки формирователей четности, блоки сравнения, дешифратор, коммутаторы, с второго по четвертый, и

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в системах, которые требуют использования высоконадежных схем памяти.

Целью изобретения является увеличение информационной емкости устройства.

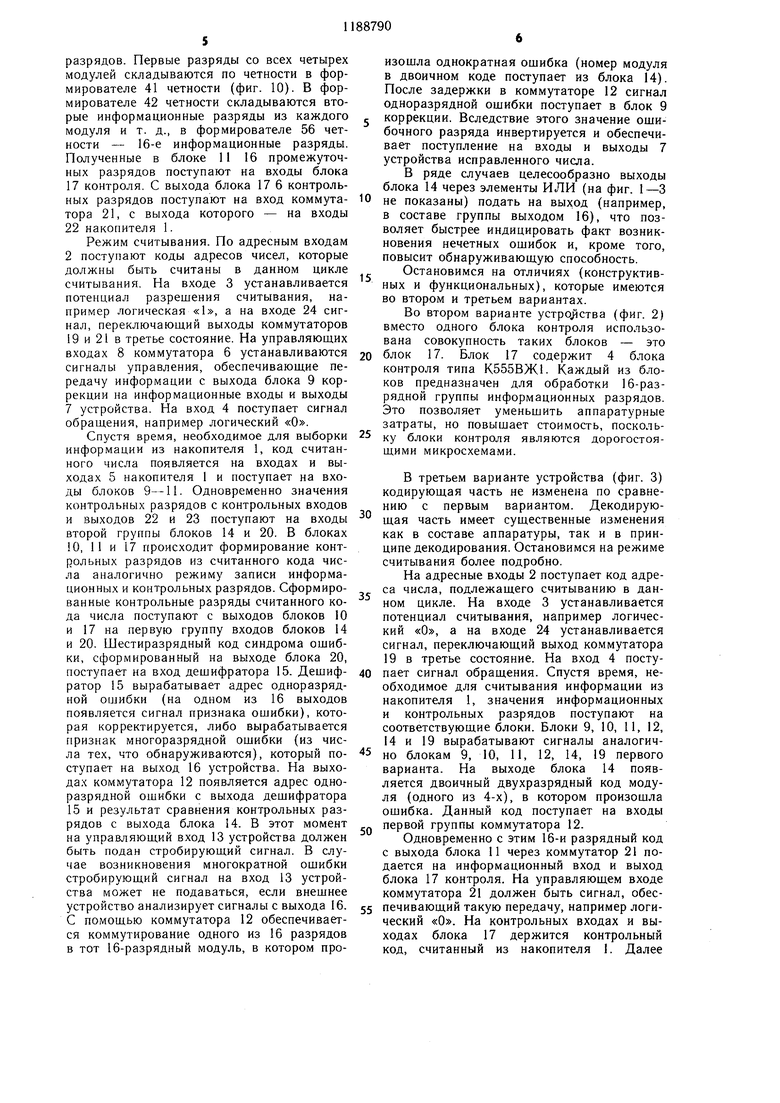

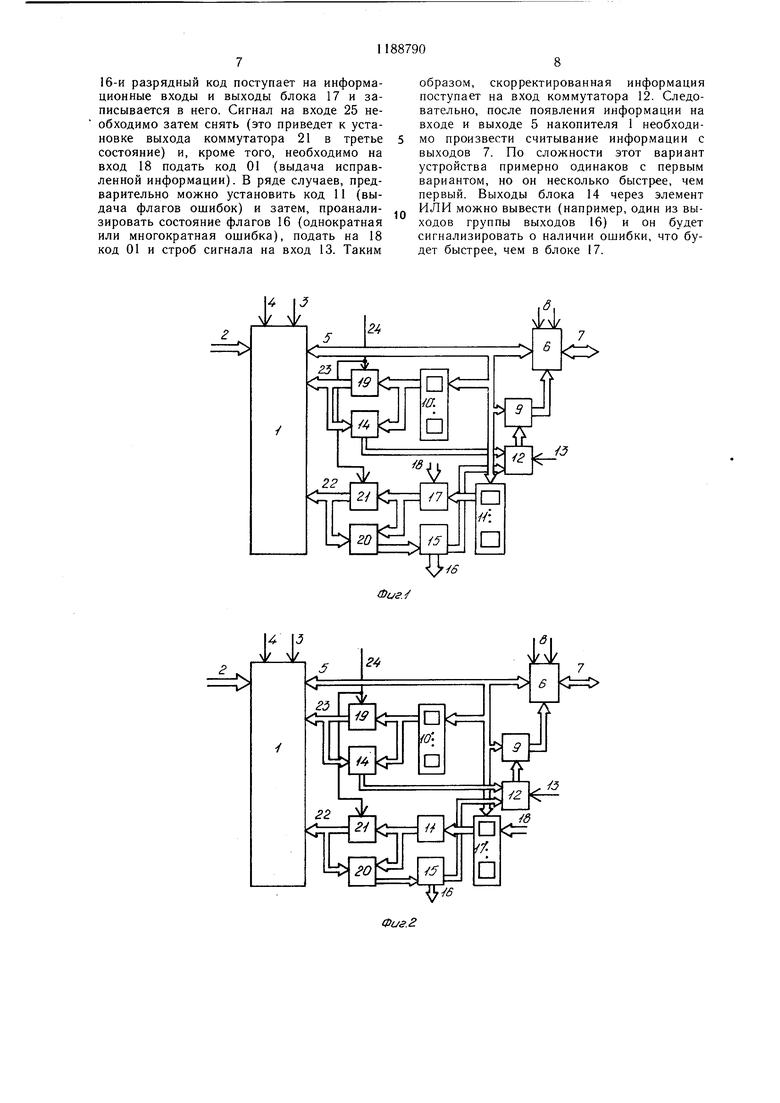

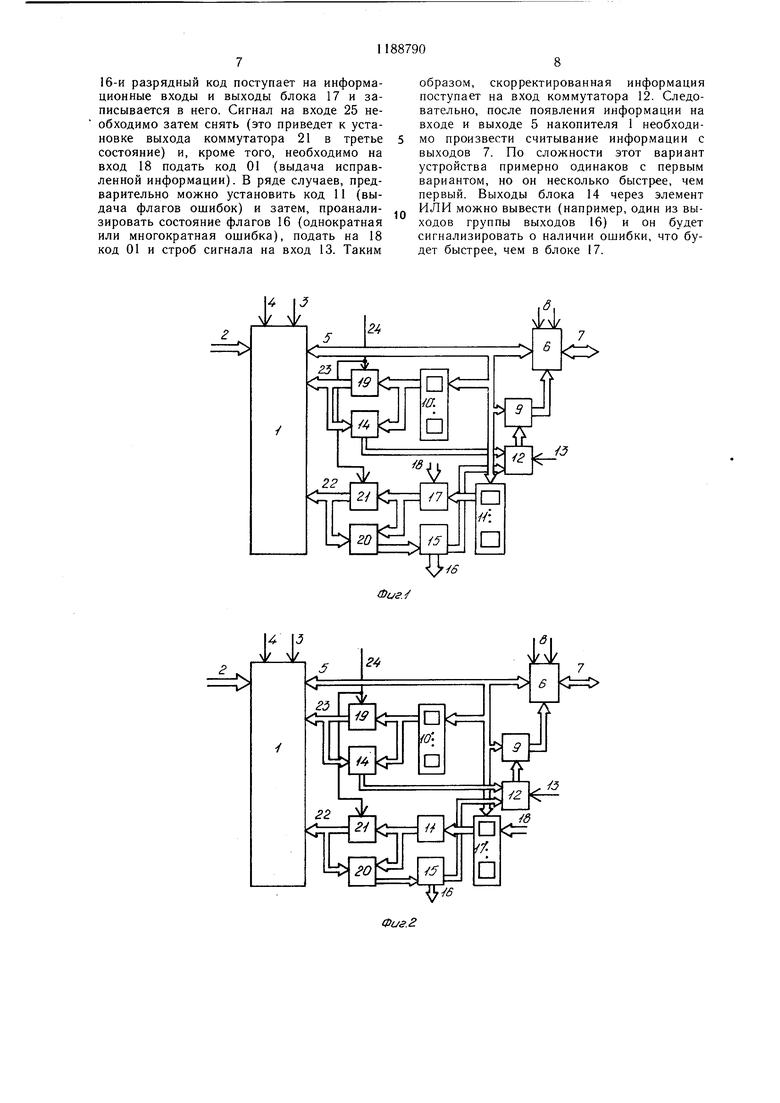

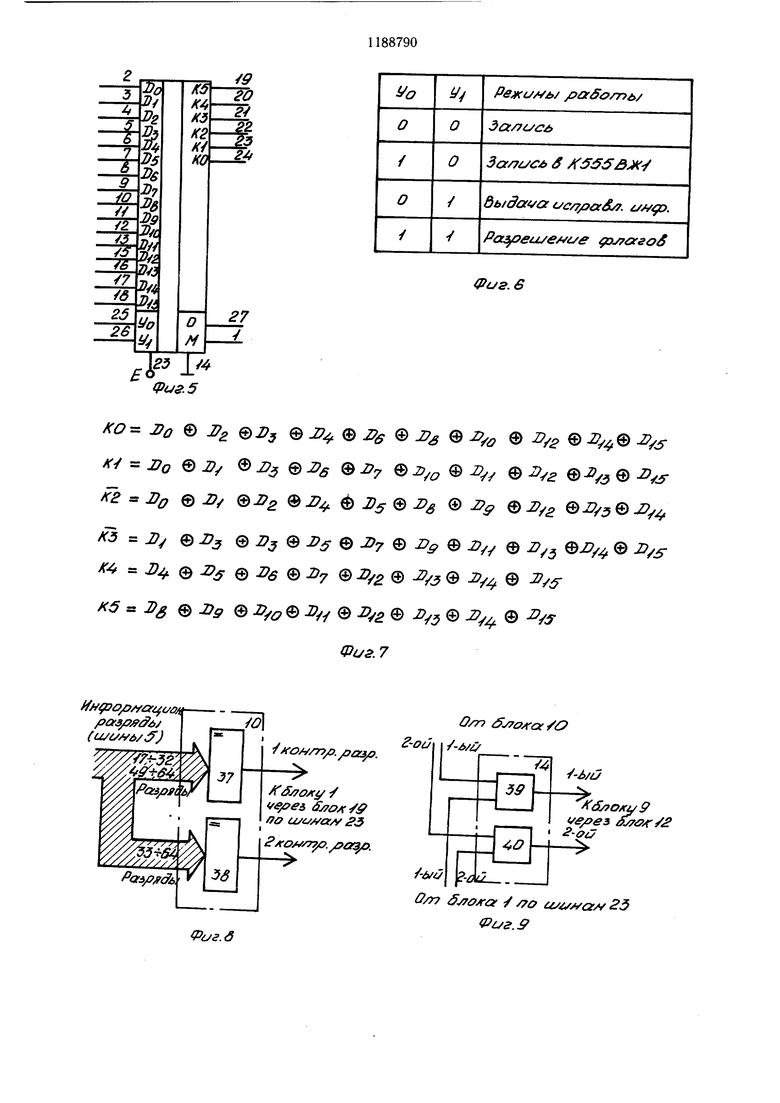

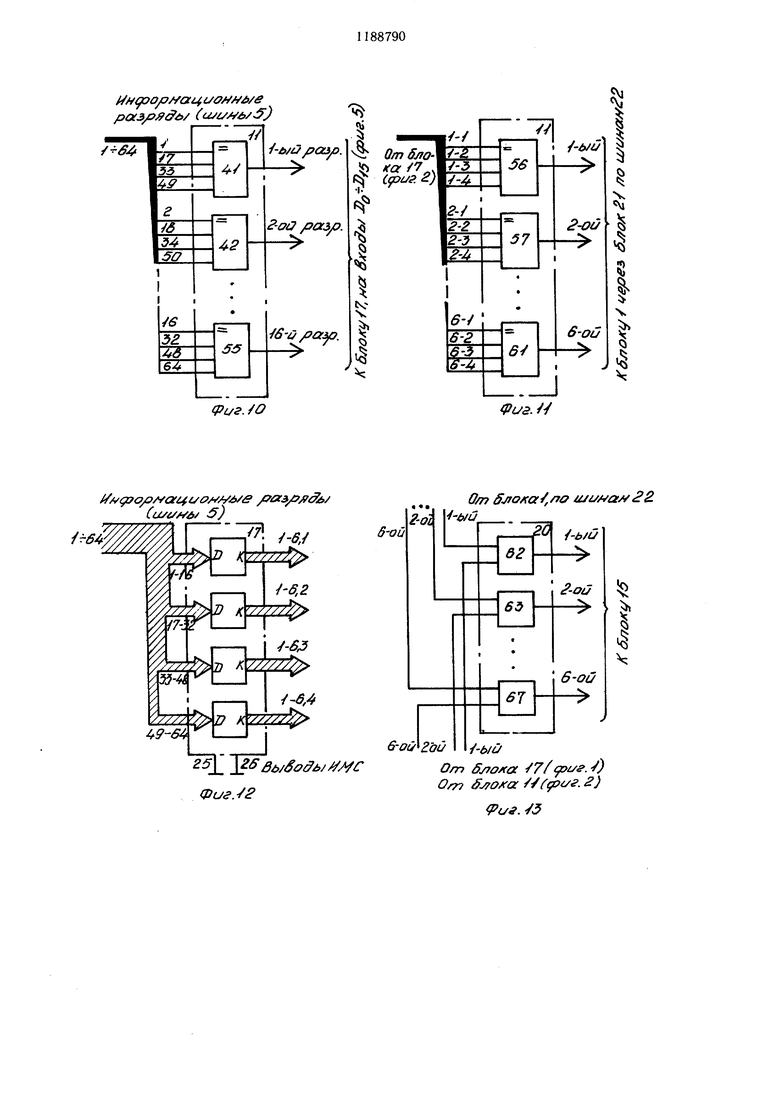

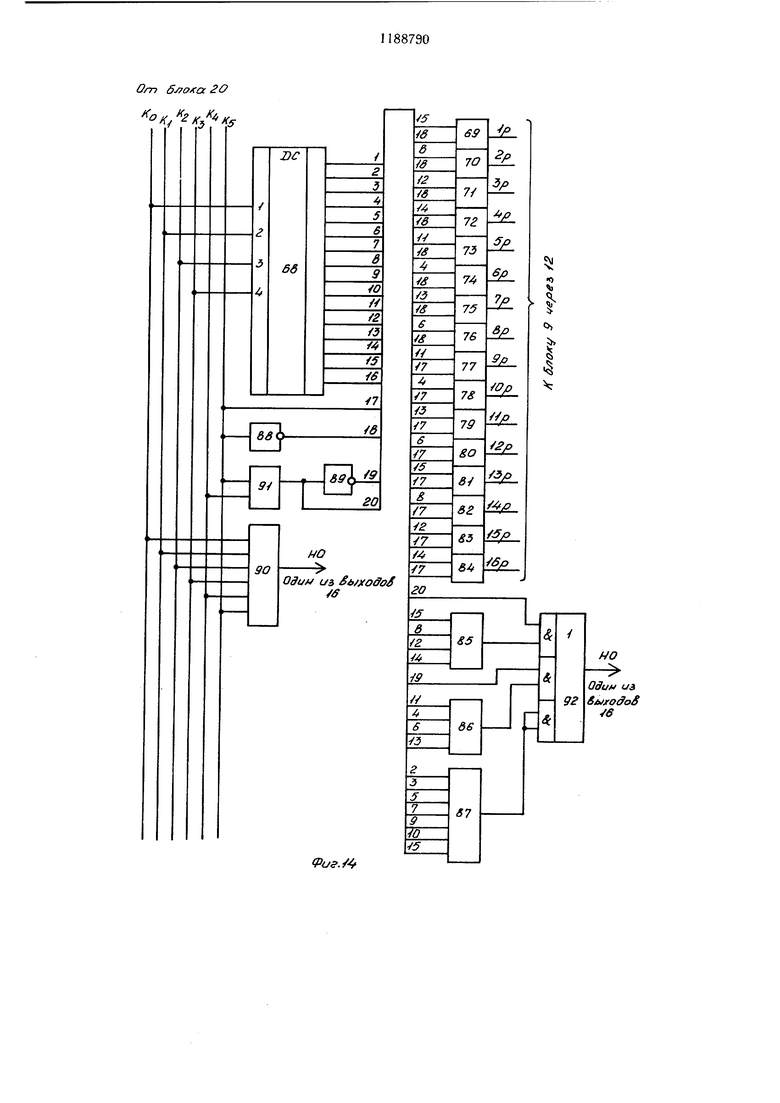

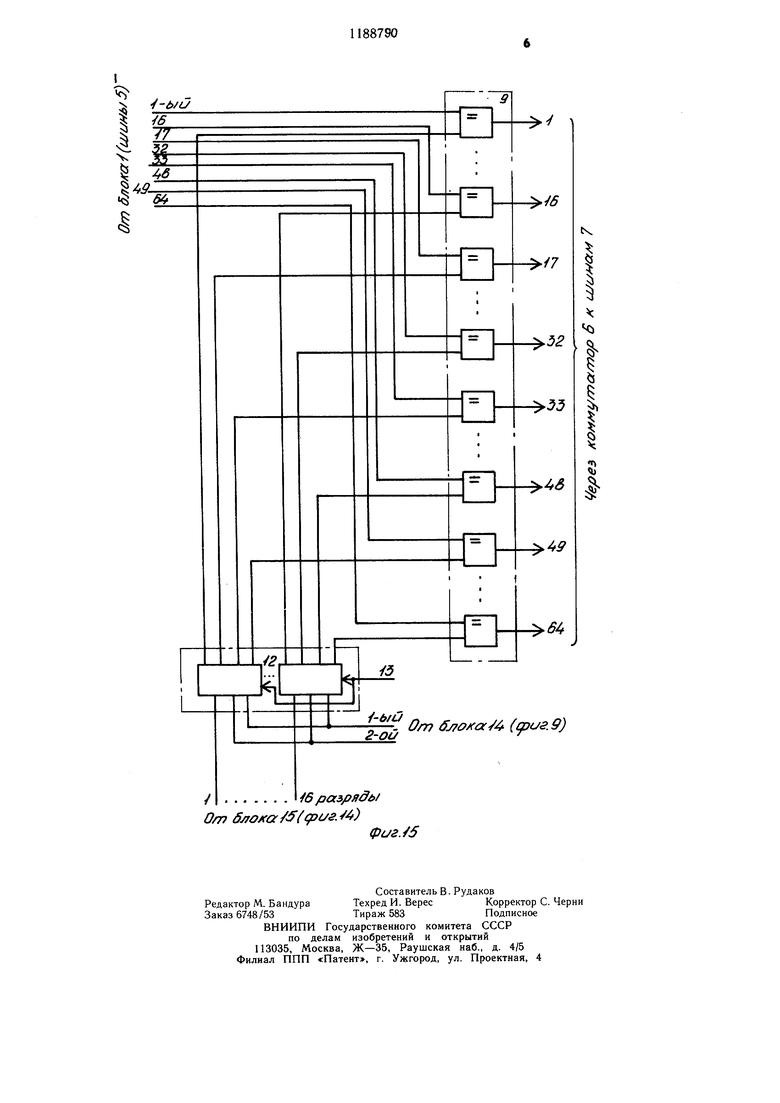

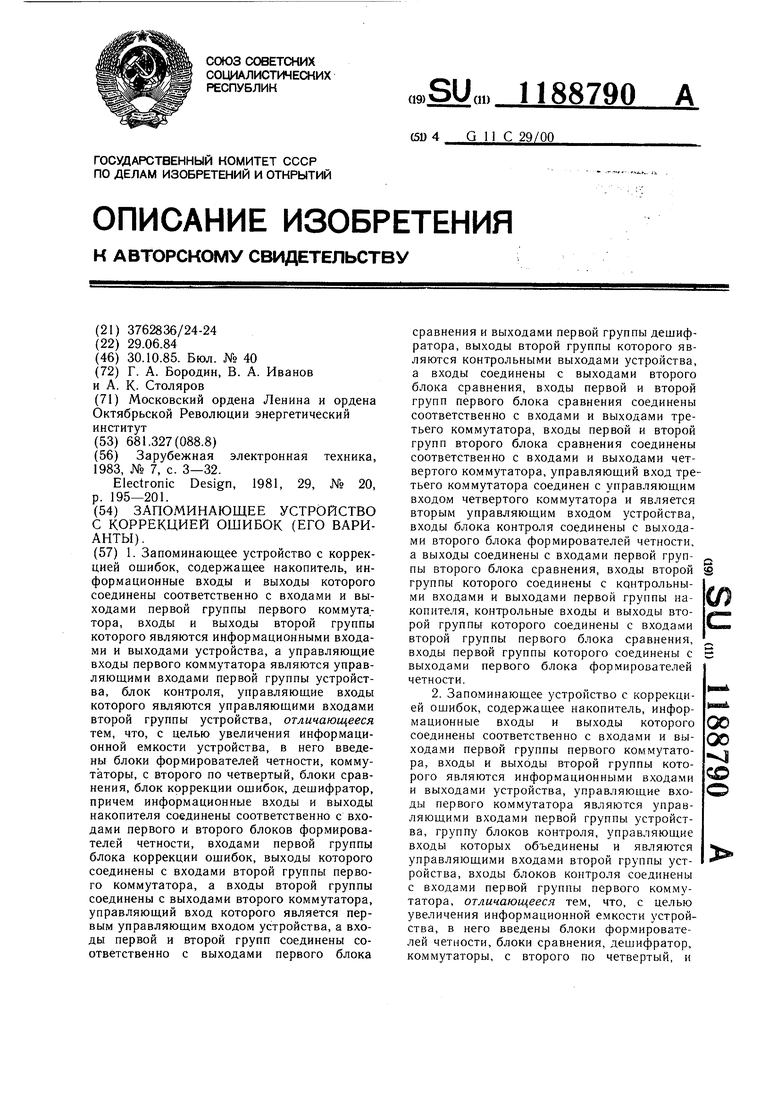

На фиг. 1-3 представлены структурные схемы первого (фиг. 1), второго (фиг. 2) и третьего (фиг. 3) вариантов запоминающего устройства; на фиг. 4 - структурная схема блока контроля на основе БИС коррекции типа К555ВЖ1; на фиг. 5 - условное графическое представление указанной БИС; на фиг. 6 - таблица режимов ее работы; на фиг. 7 - выражения для подсчета контрольных разрядов; на фиг. 8-15 структурные схемы первого блока формирователей четности (фиг. 8), первого блока сравнения (фиг. 9), второго блока формирователей четности для первого и третьего вариантов (фиг. 10) и для второго варианта (фиг. 11 и 12) устройства, второго блока сравнения (фиг. 13), дешифратора (фиг. 14), блока коррекции и коммутатора (фиг. 15).

Запоминающее устройство с коррекцией ошибок по первому варианту (фиг. 1) содержит накопитель 1, в котором выделены информационные модули по 16 разрядов и один контрольный модуль. Накопитель 1 имеет адресные входы 2, вход 3 управления режимом запись/считывание, вход 4 управления обращением. Информационные входы и выходы 5 накопителя 1 соединены с входами и выходами первой группы первого коммутатора 6, входы и выходы второй группы которого являются информационными входами и выходами 7 устройства, управляющие входы первого коммутатора 6 являются управляющими входами 8 первой группы устройства, входы первого коммутатора 6 соединены с выходами блока 9 коррекции ошибок, входы первой группы которого соединены с входами первого 10 и второго 11 блоков формирователей четности, входы второй группы блока 9 коррекций ошибок соединены с выходами второго коммутатора 12, управляющий вход которого является первым управляющим входом 13 устройства, входы первой и второй группы коммутатора 12 соединены соответственно с выходами первого блока 14 сравнения и выходами первой группы дешифратора 15, выходы второй группы которого являются контрольными выходами 16 устройства, выходы второго блока 11 формирователей четности соединены с входами блока 17 контроля, управляющие входы которого являются управляющими входами 18 второй группы устройства, выходы первого блока 10 формирователей четности соединены с входами первой группы блока 14 и входами третьего коммутатора 19, выходы блока 17 контроля соединены с входами первой группы второго блока 20 сравнения и входами четвертого коммутатора 21 входы и выходы которого соединены с входами второй группы блока 20 и контрольными входами и выходами 22 первой группы накопителя 1, контрольные входы и выходы 23 второй группы которого соединены с входами второй группы блока 14 и входами и выходами коммутатора 19, управляющий вход

которого соединен с управляющим входом коммутатора 21 и является вторым управляющи.м входом 24 устройства.

В качестве блоков 17 контроля можно использовать БИС коррекции типа К555ВЖ1.

В состав блока 17 контроля (фиг. 4) входят блоки задания обмена информационными 25 и контрольными 26 разрядами, блок 27 управления, корректирующий блок 28, генератор 29 контрольных разрядов, дешифратор 30 адреса ошибки, генератор 31 синдрома ошибки, формирователь 32 флагов, входы и выходы информационных 33 и контрольных разрядов 34, управляющие входы 35 и контрольные вы.ходы 36.

5 Блоки 10, 14, 11, 20 (фиг. 8-13) выполнены на формирователях 37-67 четности. Дешифратор 15 (фиг. 14) содержит соответственно дешифратор 68, элемент И 69-84, элементы ИЛИ 85-87, элементы НЕ 88-90, элемент НЕРАВНОЗНАЧНОСТЬ 91, эле0 мент 2И-ЗИЛИ 92.

Блок 9 коррекции и коммутатор 12 (фиг. 15) содержат соответственно 64 формирователя четности и 16 стробируемых мультиплексоров. В качестве коммутаторов 19

д и 21 может быть использована микросхема типа К531КП11, коммутатора 6 - 589АП16.

Б.юк 17, показанный на фиг. 3, работает как в режиме генерации контрольных разрядов, так и в режиме обнаружения и исправления ошибок.

Устройство работает следующим образом. Режим записи информационных н контрольных разрядов. По адресным входам 2 поступают коды адресов чисел, которые

должны быть записаны в очередном цикле записи. По входу 3 устанавливается режим записи, например логический «О, н сигнал управления на входе 24. Информационные разряды поступают на и выходы 7 первого коммутатора 6, на унразляюцлпе

входы 8 которого подаются сигналы управления, обеспечивающие передачу информации с входов и выходов 7 на информационные входы п выходы 5 накопителя 1. По входу 4 поступает сигнал обращения, например логический «О. Информационные

5 разряды (их 64), поступающие на информационные входы и выходы 5, кроме этого поступают на входы первого 0 и второго 11 блоков формирователей четности. Б.юк 0 вырабатывает значения двух контрольных

0 разрядов. Первый контрольный разря, - это четность значений разрядов 17-32 и 49-64. Второй контрольный разряд - это четность значений разрядов 33-64. С выхода блока 10 значения двух контрольных разрядов поступают на вход коммутатора 19, с выхода которого - на входы 23 накопителя 1. В это время в блоке 11 происходит выработка 16 промежуточных значений из 64 информационных

разрядов. Первые разряды со всех четырех модулей складываются по четности в формирователе 41 четности (фиг. 10). В формирователе 42 четности складываются вторые информационные разряды из каждого модуля и т. д., в формирователе 56 четности - 16-е информационные разряды. Полученные в блоке 11 16 промежуточных разрядов поступают на входы блока 17 контроля. С выхода блока 17 6 контрольных разрядов поступают на вход коммутатора 21, с выхода которого - на входы 22 накопителя 1.

Режим считывания. По адресным входам 2 поступают коды адресов чисел, которые должны быть считаны в данном цикле считывания. На входе 3 устанавливается потенциал разрешения считывания, например логическая «1, а на входе 24 сигнал, переключающий выходы коммутаторов 19 и 21 в третье состояние. На управляющих входах 8 коммутатора 6 устанавливаются сигналы управления, обеспечивающие передачу информации с выхода блока 9 коррекции на информационные входы и выходы 7 устройства. На вход 4 поступает сигнал обращения, например логический «О.

Спустя время, необходимое для выборки информации из накопителя 1, код считанного числа появляется на входах и выходах 5 накопителя 1 и поступает на входы блоков 9-11. Одновременно значения контрольных разрядов с контрольных входов и выходов 22 и 23 поступают на входы второй группы блоков 14 и 20. В блоках 0, 11 и 17 происходит формирование контрольных разрядов из считанного кода числа аналогично режиму записи информационных и контрольных разрядов. Сформированные контрольные разряды считанного кода числа поступают с выходов блоков 10 и 17 на первую группу входов блоков 14 и 20. Шестиразрядный код синдрома ощибки, сформированный на выходе блока 20, поступает на вход дешифратора 15. Дешифратор 15 вырабатывает адрес одноразрядной ощибки (на одном из 16 выходов появляется сигнал признака ощибки), которая корректируется, либо вырабатывается признак многоразрядной ощибки (из числа тех, что обнаруживаются), который поступает на выход 16 устройства. На выходах коммутатора 12 появляется адрес одноразрядной ошибки с выхода дещифратора 15 и результат сравнения контрольных разрядов с выхода блока 14. В этот момент на управляющий вход 13 устройства должен быть подан стробирующий сигнал. В случае возникновения многократной ошибки стробирующий сигнал на вход 13 устройства может не подаваться, если внешнее устройство анализирует сигналы с выхода 16. С помощью коммутатора 12 обеспечивается коммутирование одного из 16 разрядов в тот 16-разрядный модуль, в котором произошла однократная ошибка (номер модуля в двоичном коде поступает из блока 14). После задержки в коммутаторе 12 сигнал одноразрядной ошибки поступает в блок 9 коррекции. Вследствие этого значение ошибочного разряда инвертируется и обеспечивает поступление на входы и выходы 7 устройства исправленного числа.

В ряде случаев целесообразно выходы блока 14 через элементы ИЛИ (на фиг. 1-3 не показаны) подать на выход (например, в составе группы выходом 16), что позволяет быстрее индицировать факт возникновения нечетных ощибок и, кроме того, повысит обнаруживающую способность.

Остановимся на отличиях (конструктивных и функциональных), которые имеются во втором и третьем вариантах.

Во втором варианте устрр ства (фиг. 2) вместо одного блока контроля использована совокупность таких блоков - это блок 17. Блок 17 содержит 4 блока контроля типа К555ВЖ1. Каждый из блоков предназначен для обработки 16-разрядной группы информационных разрядов. Это позволяет уменьщить аппаратурные затраты, но повышает стоимость, поскольку блоки контроля являются дорогостоящими микросхемами.

В третьем варианте устройства (фиг. 3) кодирующая часть не изменена по сравнению с первым вариантом. Декодирующая часть имеет существенные изменения как в составе аппаратуры, так и в принципе декодирования. Остановимся на режиме считывания более подробно.

На адресные входы 2 поступает код адреса числа, подлежащего считыванию в данном цикле. На входе 3 устанавливается потенциал считывания, например логический «О, а на входе 24 устанавливается сигнал, переключающий выход коммутатора 19 в третье состояние. На вход 4 поступает сигнал обращения. Спустя время, необходимое для считывания информации из накопителя 1, значения информационных и контрольных разрядов поступают на соответствующие блоки. Блоки 9, 10, 11, 12, 14 и 19 вырабатывают сигналы аналогично блокам 9, 10, 11, 12, 14, 19 первого варианта. На выходе блока 14 появляется двоичный двухразрядный код модуля (одного из 4-х), в котором произошла ошибка. Данный код поступает на входы первой группы коммутатора 12.

Одновременно с этим 16-и разрядный код с выхода блока 11 через коммутатор 21 подается на информационный вход и выход блока 17 контроля. На управляющем входе коммутатора 21 должен быть сигнал, обеспечивающий такую передачу, например логический «О. На контрольных входах и выходах блока 17 держится контрольный код, считанный из накопителя 1. Далее

16-и разрядный код поступает на информационные входы и выходы блока 17 и записывается в него. Сигнал на входе 25 необходимо затем снять (это приведет к установке выхода коммутатора 21 в третье состояние) и, кроме того, необходимо на вход 18 подать код 01 (выдача исправленной информации). В ряде случаев, предварительно можно установить код 11 (выдача флагов ошибок) и затем, проанализировать состояние флагов 16 (однократная или многократная ошибка), подать на 18 код 01 и строб сигнала на вход 13. Таким

Г1

3

образом, скорректированная информация поступает на вход коммутатора 12. Следовательно, после появления информации на входе и выходе 5 накопителя 1 необходимо произвести считывание информации с выходов 7. По сложности этот вариант устройства примерно одинаков с первым вариантом, но он несколько быстрее, чем первый. Выходы блока 14 через элемент ИЛИ можно вывести (например, один из выходов группы выходов 16) и он будет сигнализировать о наличии ошибки, что будет быстрее, чем в блоке 17.

1 и

П

1 U Us

иг.д

с КО- J}Q ® 2 @Dy © J7 Л/ J7o ® / ® 2} 1Г г @ ® -27 KS 2) ® © 27j © -Z f( ® © 2}Q © 7 /г а 3) © -Z © ® -ZV/

(Раг.б

Фиг. 6

Pfja.9 ® 2}g ® J} @ 2 ® 2} ® J} ©277 ® -Z © // © 2./5, ® yj, в) -2. V ®ЛЭ® / 5 © -2 ® .g ® J7, V ® ® ® -2// ф /.j © -27 / © / V « . © У © © © -2 г/. 7

(риг. /О

/в у с /уаг/ длЛ й/г ( )

Z/T

ipus. //

От .

SQU

От /7/$г./ OfTi СуУ(/г. 2)

Pus. /J

От 6У70ха 2О

| Зарубежная электронная техника, 1983, № 7, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Electronic Design, 1981, 29, № 20, p | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

Авторы

Даты

1985-10-30—Публикация

1984-06-29—Подача