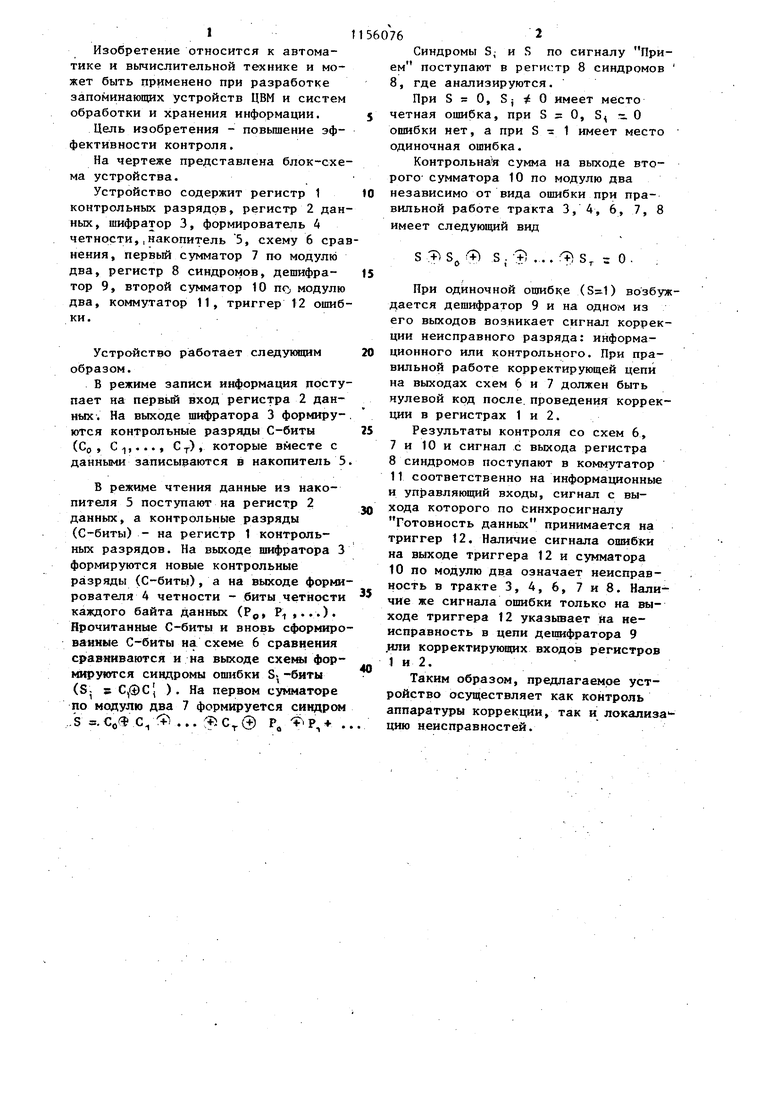

1 Изобретение относится к автоматике и вычислительной технике и может быть применено при разработке запоминающих устройств ЦВМ и систем обработки и хранения информации. Цель изобретения - повьпиение эффективности контроля. На чертеже представлена блок-схе ма устройства. Устройство содержит регистр 1 контрольных разрядов, регистр 2 дан ных, шифратор 3, формирователь 4 четности,.накопитель 5, схему 6 сра нения, первый сумматор 7 по модулю два, регистр 8 синдромов, дешифратор 9, второй сумматор 10 пс, модулю два, коммутатор 11, триггер 12 ошиб ки. Устройство работает следующим образом. В режиме записи информация посту пает на первый вход регистра 2 данных. На выходе шифратора 3 формируются контрольные разряды С-биты (GO , с 1,. .., с Т-) . которые вместе с данными записываются в накопитель 5 В режиме чтения данные из накопителя 5 поступают на регистр 2 данных, а контрольные разряды (С-биты) - на регистр 1 контрольных разрядов. На выходе шифратора 3 формируются новые контрольные разряды (С-биты), а на выходе форми рователя 4 четности - биты четности каждого байта данных (Рр, Р ,...). Прочитанные С-биты и вновь сформиро ванные С-биты на схеме 6 сравнения ср авниваются и на выходе схеьш формируются синдромы ошибки S- -биты (S- 5 С,®С ). На первом сумматоре по модулю два 7 формируется синдром .15 . С, t ... :+) Р„ ,- 762Синдромы S, и S по сигналу Прием поступают в регистр 8 синдромов 8, где анализируются. При S О, Sj О имеет место четная ошибка, при 5 0, S . О ошибки нет, а при S - 1 имеет место одиночная ошибка. Контрольна сумма на выходе второго сумматора 10 по модулю два независимо от вида ошибки при правильной работе тракта 3, 4, 6, 7, 8 имеет следуюш;ий вид S .DS +) S; Э ... :t S :: о При одиночной ошибке () возбуждается дешифратор 9 и на одном из его выходов возникает сигнал коррекции неисправного разряда: информационного или контрольного. При правильной работе корректирующей цепи на выходах схем 6 и 7 должен быть нулевой код после, проведения коррекции в регистрах 1 и 2. Результаты контроля со схем 6, 7и 10 и сигнал ,с выхода регистра 8синдромов поступают в коммутатор 11 соответственно на информационные и уп|эавляющий входы, сигнал с выхода которого по синхросигналу Готовность данных принимается на триггер 12. Наличие сигнала ошибки на выходе триггера 12 и сумматора 10 по модулю два означает неисправность в тракте 3, 4, 6, 7 и 8. Наличие же сигнала ошибки только на выходе триггера 12 указывает на неисправность в цепи дешифратора 9 .или корректирующих входов регистров 1 и 2. Таким образом, предлагаемое устройство осуществляет как контроль аппаратуры коррекции, так и локализацию неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1661840A1 |

| Запоминающее устройство с контролем | 1989 |

|

SU1624535A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С КОНТРОЛЕМ,, содержащее регистр контрольных разрядов, регистр данных, шифратор, формирователь четности, схему сравнения, первый сумматор по модулю два, накопитель, дешифратор, причем первый информационный вход регистра данных является информационным входом устройства, а выход является информационHbw выходом устройства и соединен с входами шифратора, формирователя четности и первым входом накопителя, выход которого соединен с вторым и первым информационными входами регистра данных и первым информационным входом регистра контрольных разрядов, выход которого соединен с первьм входом схемы сравнения, вторые входы которой соединены с выходом шифратора и вторым входом наквтителя, первьк) и второй входы первого сумматора по модулю два соединены соответственно с выходами регистра контрольных разрядов и формирователя четности, выход дешифратора соединен с вторым информационным входом регистра контрольных разрядов и третьим информационHbw входом регистра данных, отличающееся тем, что, с целью повышения эффективности контроля, устройство дополнительно содержит регистр синдромов, второй сумматор по модулю два, коммутатор и триггер ошибки, причем синхровход регистра синдромов является синхро§ входом устройства, а первый и второй информационные входы соединены соответственно с выходами схемы сравнения и первого сумматора по модулю два, подключенными также к группе информационных входов коммутатора, . управляющий вход которого соединен с выходом разряда одиночной ошибки регистра синдромов, а информа ционный вход - с выходом второго Од сумматора по модулю два, входы коо торого соединены с группой выходов регистра синдромов, соединенной О) также с входами дешифратора, выход коммутатора соединен с информационным входом триггера ошибки, синхровход которого соединен с входом Готовность данных устройства, выход триггера ошибки является выходом ошибки устройства.

| Электроника, 1980, № 1, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Устройство для контроля блоков коррекции ошибок в памяти | 1980 |

|

SU951407A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-05-15—Публикация

1983-03-05—Подача