го дешифратора являются одними из управлякяр1х выходов устройства, выходы первого и второго блоков формирователей четности соединены соответственно с входами ь вькодами первых групп накопителя.

2. Устройство по П.1, отличающееся тем, что выходы

1161990

первого и второго блоков формирователей четности соединены с входами второй группы соответственно первого и второго блоков формирователей контрольных разрядов по нечетному модулю, а одни из выходов второго преобразователя кодов является другим управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Запоминающее устройство с коррекцией ошибок (его варианты) | 1984 |

|

SU1188790A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК, содержащее первый и второй блоки формирователей контрольных разрядов по нечетному модулю, первый и второй блоки формирователей четности, регистр числа, первый и второй блоки сравнения, мультиплексор, первьш и второй преобразователи кодов и накопитель, входы первой группы которого сЬединены с входами первой группы первого блока формирователей контрольных разрядов по нечетному модулю и являются числовыми входами устройства, выходы первого блока формирователей контрольных разрядов по нечетному модулю и выходы первого блока формирователей четности соединены соответственно с входами второй и третьей групп накопителя, выходы первой группы которого соединены с входами первой группы второго блока формирователей контрольных разрядов по нечетному модулю и информационными входами первой группы регистра числа, выходы которого являются числовыми выходами устройства, входы первой группы мультиплексора соединены с вькодами первого блока сравнения, а входы второй группы с выходами второго преобразователя кодов, входы первой группы которого соединены с выходами второго блока сравнения, входы первой группы которого соединены с выходами второго блока формирователей контрольных разрядов по нечетному модулю, а входы второй группы - с выходами второй группы накопителя, выходы третьей грзттпы которого соединены с входами первой группы первого блока сравнения, входы второй группы которого соединены с выходами второго блока формирователей четности, отли.ающееся тем, что, с целью повышения точности (Л контроля и надежности устройства, с: в него введены первый и второй элементы ИЛИ, первый и второй дешифраторы, коммутатор, входы первой группы которого соединены с входами .первого преобразователя кодов и выходами первого блока сравнения,выходы коммутатора соединены с входами второй группы второго преобразос S вателя кодов, а входы второй группы .коммутатора соединены с выходами первого депшфратора и выходами перQD вого элемента ИЛИ, выходы которого соединены с синхровходом регистра числа, информационные входы второй группы которого соединены с выхода О . ми мультиплексора, г.ходы второго элемента ИЛИ соединены с выходами второго блока сравнения, а выход соединен с управляющими выходами первого и второго дешифраторов, входы которых соединены с выходо - первого преобразователя кодов, выходы пторо

Изобретение относится к вычислительной технике а именно к устройствам с коррекцией ошибок, содержащим многоразрядные блоки памяти, средства для исправления многократных ошибок и может быть использовано для повьшения надежности хранения информации при небольшом количестве избыточных разрядов.

Известно устройство с коррекцией ошибок, которое содержит накопитель и средства контроля на основе коДа Хэмминга lj .

В данном устройстве возможно исправление однократных ошибок и обна ружение некоторых ошибок другой краности. Недостаток этого устройства невозможность обнаружения всех ошибок отказавшего блока памяти и исправление наиболее вероятных из них

Наиболее близким техническим решением к изобретению является запоминающее устройство с автономным контролем, содержащее накопитель, состоящий из блоков памяти и соединенный с первым формирователем контрольных разрядов, постоянным накопителем и формирователем четности и вторыми формирователем контрольных разрядов и постоянным накопителем, сумматор-вычитатель, подключенный к одним из входов третьего, постоянного накопителя, соединенного с блоком сравнения и регистрирующей схемой 2 .

Недостаток этого устройства невозможность исправления ошибок при отказе блока памяти, что не позволяет повысить надежность устройства .

Целью изобретения является повышение точности контроля путем исправления наиболее вероятных ошибок при одновременном повышении надежности работы устройства. .

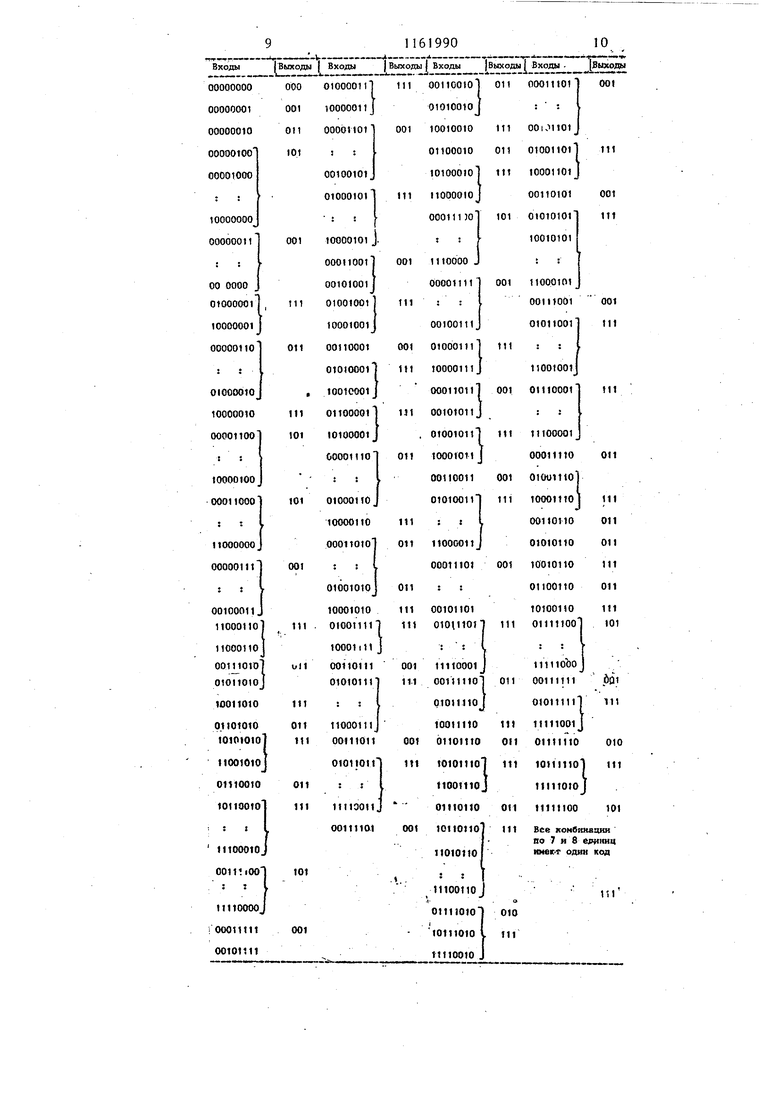

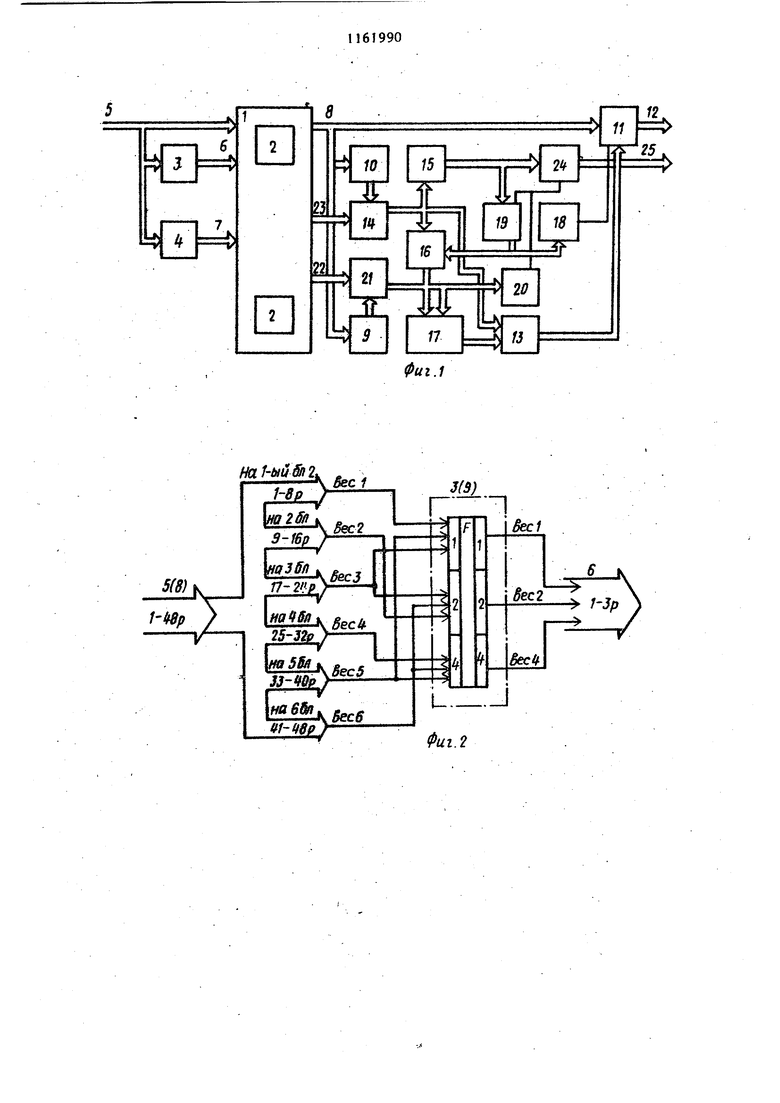

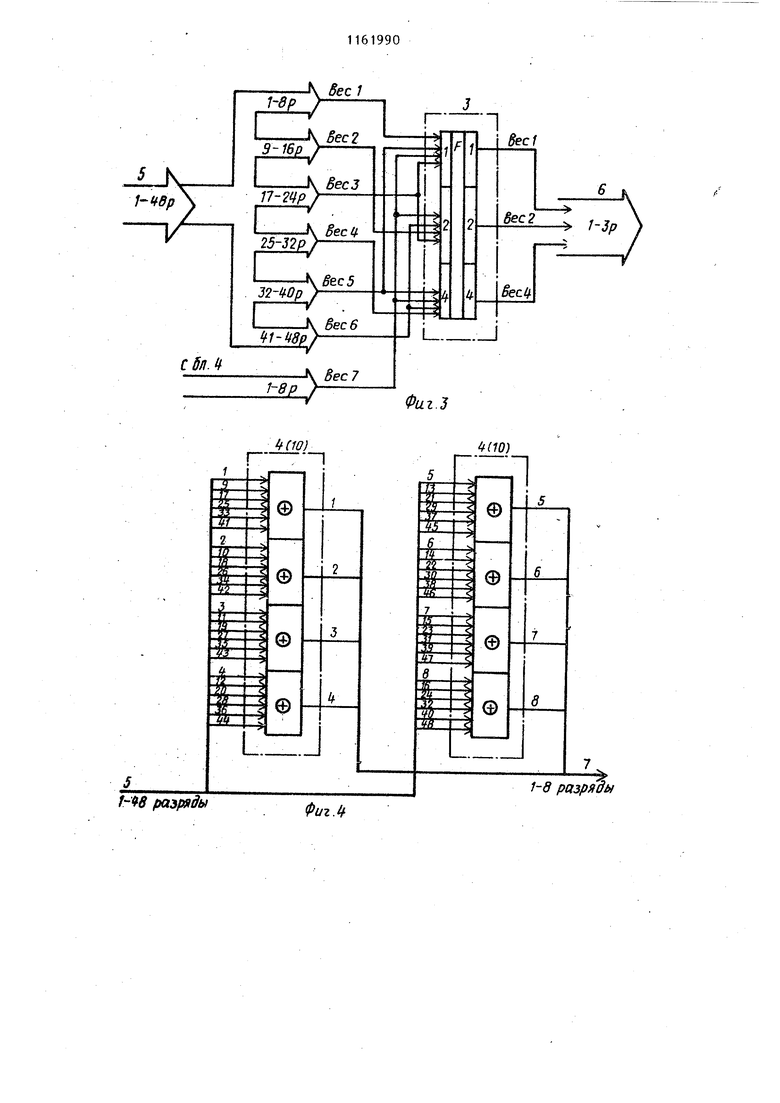

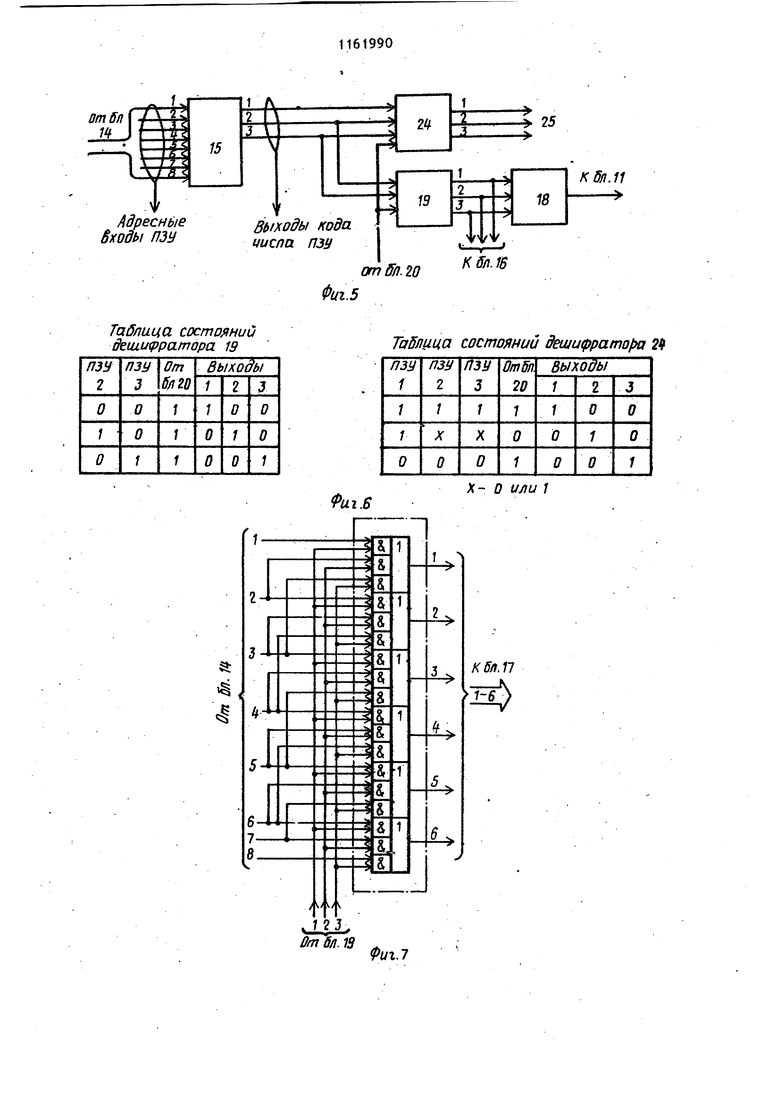

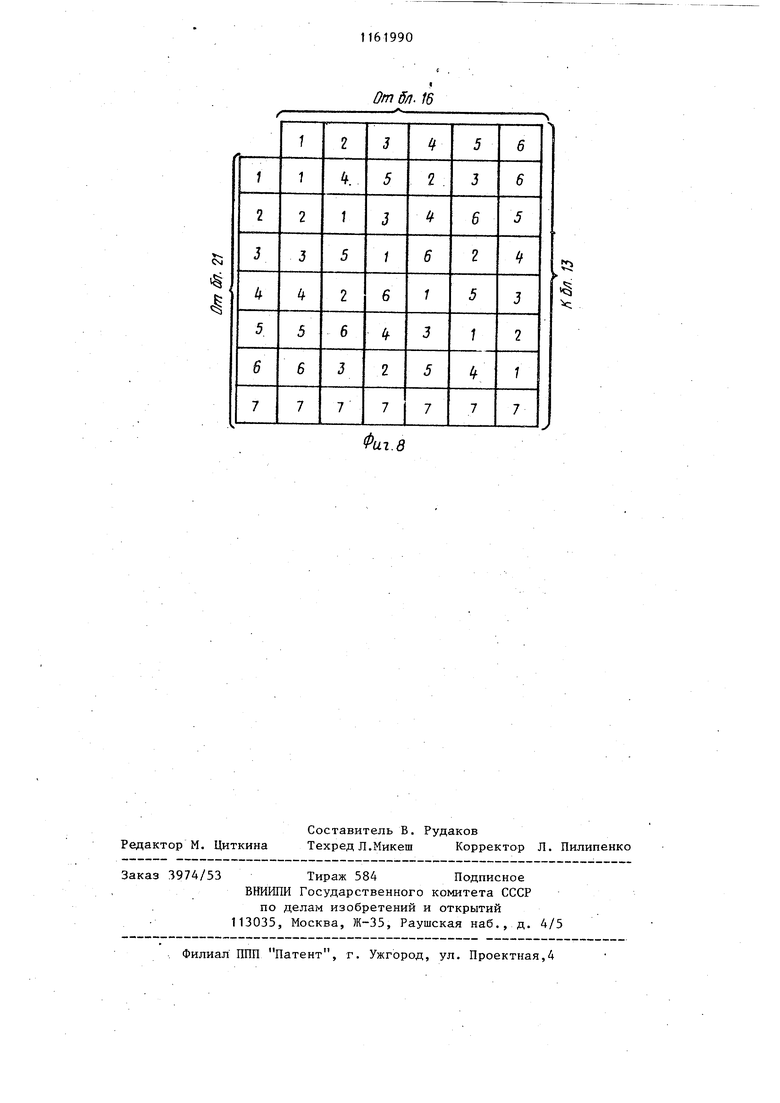

Поставленная цель .достигается тем, что в запоминающее устройство с коррекцией ошибок, coдepжaи ee первый и второй блоки формирователей контрольных разрядов по нечетному модулю, первый и второй блоки формирования четности, регистр числа, первый и второй блоки сравнения, мультиплексор, первый и второй пре- образователи кодов и накопитель,вхоы первой группы которого соединены с входами первой группы первого блока формирователей.контрольных разрядов по нечетному модулю и являются числовыми входами устройства, выходы первого блока формирователей контрольных разрядов по нечетному модулю и выходы первого блока формирователей четности соединены соответственно с входами второй и третьей групп накопителя, выходы первой группы которого соединены с входами первой группы второго блока формирователей контрольных разрядов по нечетному модулю и информационными входами первой группы регистра числа, выходы которого являются числовыми выходами устройства, входы первой группы мультиплексора соединены с выходами первого блока сравнения, а входы второй группы - с выходами второго преобразователя кодов, входы первой группы которого соединены с выходами второго блока сравнения, входы первой группы которого соединены с выходами второго блока формирователей контрольных разрядов по нечетному модулю, а входы второй группы соединены - с выходами второй группы накопителя, выходы третьей групп которого соединены с входами первой группы первого блока сравнения,входы второй группы которого соединены с выходами второго блока формирова телей четности, введены первьш и второй элементы РШИ, первый и втор дешифраторы, коммутатор, входы перв группы которого соединены с входами первого преобразователя кодов и вы ходами первого блока срявнения, вых ды коммутатора соединены с входами второй группы второго преобразова.теля кодов, а входы второй группы коммутатора соединены с выходами первого дешифратора и выходами первого элемента ИЛИ, выходы которого соединёнь с синхровходом регистра числа, информационные входы второй группы которого соединены с выходами мультиплексора, входы второго элемента ИЛИ соединены с выходами второго блока сравнения, а выход со динен с управляющими выходами первого и второго дешифраторов,входы которых соединены с выходом первого преобразователя кодов, выходы второ го дешифратора являются одними из управляющих выходов устройства, выходы первого и второго блоков формирователей четности соединены соответственно с входами и выходами . первых групп накопителя, I. Кроме того, выходы первого и второго блоков формирователей чет. ности соединены с входами второй группы соответственно первого и вто рого блоков формирователей контрольных разрядов по «ечетному модулю, а один из выходов второго пре образователя кодов является другим управляющим выходом устройства. На фиг.1 изображена принципиальная схема устройства; на фиг.2 блок формирователей контрольных разрядов по нечетному модулю (для шести 8-разрядньк блоков памяти)Jна фиг.З - связи первого блока формирователей контрольных разрядов по нечетному модулю и первого блока формирователей четности; на фиг.4 блок формирователей четности; на фиг.З - первый преобразователь кодов, элемент ИЛИ, первый и второй дешифраторы; на фиг.6 - таблицы состояний дешифраторов; на фиг.7 структурная схема коммутатора; на фиг.8 - таблица истинности второго преобразователя. Устройство содержит (см.фиг.1) накопитель 1, состоящий из многоразрядных блоков 2 памяти, входы первой группы накопителя 1 соединены с входами первого блока 3 формирователей контрольных разрядов по нечетному модулю и входами первого блока 4 формирователей четности и являются числовыми входами 5 устройства, выходы первого блока 3 формирователей контрольных разрядов по нечетному модулю и выходы первого блока 4 формирователей четности соединены соответственно с входами 6 и 7 второй и третьей групп накопителя 1, выходы первой группы 8 которого соединены с второго блока 9 формирователей контрольных разрядов по нечетному модулю, второго блока 10 формирователей четности и входами первой группы регистра 11 ч(исла, выходы которого являются числовыми выходами 12 устройства, а входы второй группы соединены с выходами, мультиплексора 13, входы первой группы которого соединены с выходами первого блока 14 сравнения, входами первого преобразователя 15 кодов, входами первой группы коммутатора 16, входы второй группы мультиплексора 13 соединены с выходами второго преобразователя 17, входы первого элемента ИЛИ 18 соединены с выходами первого дешифратора 19 и входами второй группы коммутатора 16, выходы которого соединены с входами второй группы второго преобразователя 17 кодов, входы первой группы которого соединены с входами второго элемента ИЛИ 20 и выходами второго блока 21 сравнения, входы первой группы которого соединены с выходами второго блока 9 формирователей контрольных разрядов по нечетному модулю, а входы второй группы соединены с выходами второй группы 22 накопителя 1,. выходы 23 третьей группы которого соединены с входа ми первой группы первого блока 14 сравнения, входы вто1)ой грзппы которой соединены с выходами второго блока 10 формирователей четности, выход первого элемента ИЛИ 18 соединен с синхровходом регистра 11 числа, выход второго

элемента ШШ 20 соединен с управлякяцим входом первого 19 и второго 24 дешифраторовt входы которых соединены с выходом первого преобразователя 15 кодов, выходы второго дешифратора 24 являются одними из управляющих выходов 25 устройства.

В другом варианте этого устройства выход блока4 может быть соединен с второй группой входов блока 3, выход блока 10 может быть соединен с второй группой входов блока 9, а выход -преобразователя 17 имеет дотюлнительный выход, который является другим управляющим выходом устройства (на фиг.1 не показано).

Устройство работает следующим образом.

В очередном цикле записи на входы 5 первой группы накопителя 1 поступают коды чисел, подлежащие записи, например, 48 разрядов. Тогда разряды с 1-го по 8-й записываются в первый блок 2 памяти, разряДы 9-16 - во второй и так далее. Одновременно в блоках 4 и 3 происходит выработка двух групп контрольных разрядов. В блоке 3 получается вычет числа по модулю 7 это 3 контрольных разряда, а в блоке 4 получается 8 контрольных разрядов - признаков четнцсти для одноименных разрядов с различных блоков 2. Принцип получения контрольных разрядов поясняется на фиг.2 и 4. Полученные две группы контрольных разрядов записываются в избыточные разряды накопителя 1 по входам 6 и 7.

Б режиме считывания информационные разряды поступают при разрешающем потенциале с блока 18 (О) для записи в регистр 11 числа, а также в блоки 9 и 10, где аналогично блокам 3 и 4 происходит выработка двух групп контрольных разрядов, которые затем поступают на одни из входов соответствующих блоков 14 и 21. Одновременно на другие входы этих же блоков поступают значения избыточных разрядов, считанных из накопителя 1. Если в результате сравнения на выходах блоков 14 и 21 будут нули, то это означает, что ошибки в устройстве нет и другие блоки не сработают.

Если в устройстве произошел отказ, то на выходах блоков 14 и 21 одновременно или порознь возникают коды несравнения.В блоке 14 коды нёсравнения определяют разряды, в которых произошла ошибка, а в блоке 21 образуется двоичный код изменения вычета числа по модулю 7. Код несравнения с выходов блока 14 поступает в преобразователь 15,таблица истинности которого приведена в таблице. Из преобразователя 15 считывается по соответствующему адресу код, который определяет состояние устройства: имеется исправляемая ошибка (количество разрядов между отказавшим первым разрядом и отказавпшм последним разрядом не превосходит, например, 6 позиций), имеется неисправляемая ошибка (количество разрядов между первья и последним отказавшими разрядами более 6). Считанный код поступает в дешифраторы 19 и 24, на которые одновременно поступает сигнал об ошибке с выхода элемента ИЛИ 20. Конкретная реализация связей между этими блоками представлена на фиг.5.В зависимости от состояния устройства на управляющем выходе устройства будут те или иные коды. Так, если 1 на выходе 25, то это означает, что есть неисправляемая ошибка; если 1 на выходе 25 ,то это означает, что ошибка в контрольных разрядах, соответствующих признакам четности, если 1 на выходе 25) то это означает, что произоила ошибка в контрольных разрядах, хранящих вычет числа.

Дешифратор 19 управляет работой коммутатора 16, что позволяет подавать на вход преобразователя 16 шесть разрядов вместо восьми.что уменьшает объем памяти преобразователя 17. Преобразователь 17 работает согласно таблице истинности (фиг.8). Как видно из этой таблицы, имеется однозначное соответствие между количеством ошибок в памяти и номером отказавшего блока 2 памяти, что позволяет реализовать коррекцию ошибок разрядностью от 1 до 6 бит. Ошибки кратностью 7 и 8 бит только обнаруживаются. В мультиплексоре 13 осуществляется подключение именно отказавших разрядов, поступающих с блока 14 в те разряды кода

числа, которые соответствуют отказавшему блоку 2 памяти (номер этого блока в унитарном коде - 6 шин поступает из блока 17).. Поскольку с блока 18 в данном случае поступает 1, то разрешается запись (исправление) разрядов в регистр 11 по входам второй группы. При необходимости выход блока 18 можно также сделать управлякнцим выходом устройства .

В случае модификации предложенного устройства элементы, реализую; щие вторую строку таблицы истинности дешифратора 24, можно исключить. Один из выходов блока 17, а

161990В

именно 7-й, будет выполнять его функции, т.е. может быть-достигнуто аппаратное упрощение за счет усложнения связей.

5 Технико-экономическое преимущество устройства заключается в том, что обеспечена возможность исправления наиболее вероятных ошибок при отказе одного блока памяти. Количество контрольных разрядов увеличено на 22,2%i. Количество информационных разрядов может быть увеличено с 49 до 56, или на 13,5%. В . то же время процент исправляемых

15 ошибок доходит до 90. Следовательно. повьш1ена точность контроля.

Таблица состояний ffeiuugjpamopa 19

иг.6

-Шfffn 6л. 13

от Ул. 20

Таблица состояний deuiutppamolxi 29

х- о или 1

КБЛ.П

Риг.7

См

§

От 6л- W

ч

Риг. 8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3573728, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1985-06-15—Публикация

1982-12-20—Подача