%

СП 1C

to

зд

31

(каждой точке) программы ставится в соответствие некоторое го-разрядное число. При этом в блоке постоянной памяти размещаются одноразрядные коды, которые дополняют контрольные числа до (т+1)-разрядных, содержащих четное количество единиц. В процессе реализации программы сумматор осуществляет суммирование всех слов т программы с ранее накопленными в регистре контрольными суммами. В результате этого в каждой точке программы вычисляется m-разрядный двоич45223 4

ный код текущей суммы. Указанный код и дополнительный разряд поступают на схему четности. Если условие четности не соблюдается, то схема четности генерирует сигнал ошибки, который в момент окончания операции чтения очередного слова программы передается на выход устройства. Использование IQ устройства требует введения в контролируемую программу специальных программных блоков, уравнивающих контрольные суммы различных ветвей программы. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1988 |

|

SU1649551A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1481775A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля кода программ | 1988 |

|

SU1564632A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

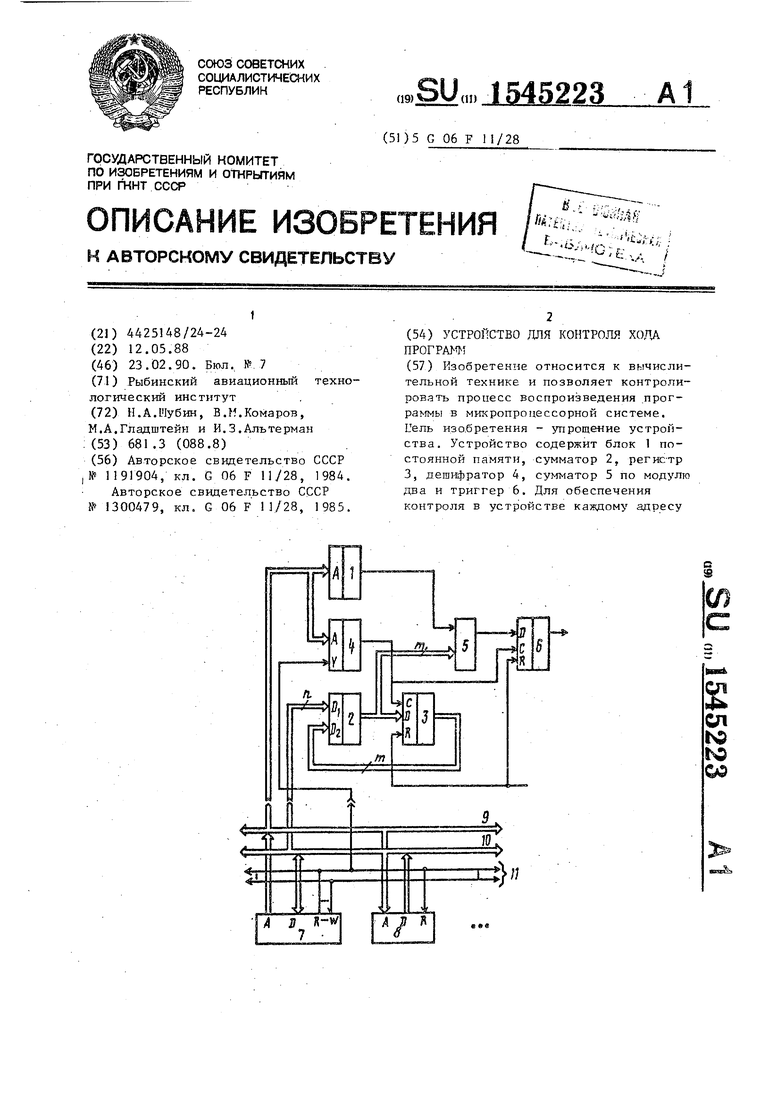

Изобретение относится к вычислительной технике и позволяет контролировать процесс воспроизведения программы в микропроцессорной системе. Цель изобретения - упрощение устройства. Устройство содержит блок 1 постоянной памяти, сумматор 2, регистр 3, дешифратор 4, сумматор 5 по модулю два и триггер 6. Для обеспечения контроля в устройстве каждому адресу (каждой точке) программы ставится в соответствие некоторое M-разрядное число. При этом в блоке постоянной памяти размещаются одноразрядные коды, которые дополняют контрольные числа до (M+1)-разрядных, содержащих четное количество единиц. В процессе реализации программы сумматор осуществляет суммирование всех слов программы с ранее накопленными в регистре контрольными суммами. В результате этого в каждой точке программы вычисляется M-разрядный двоичный код текущей суммы. Указанный код и дополнительный разряд поступает на схему четности. Если условие четности не соблюдается, то схема четности генерирует сигнал ошибки, который в момент окончания операции чтения очередного слова программы передается на выход устройства. Использование устройства требует введения в контролируемую программу специальных программных блоков, уравнивающих контрольные суммы различных ветвей программы. 1 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем, не чувствительных к сбоям программы.

Целью изобретения является упрощение устройства.

На чертеже изображена схема предлагаемого устройства.

Устройство для контроля хода программ содержит блок 1 постоянной памяти, сумматор 2, регистр 3 и дешифратор 4, кодовый вход которого подключен к входу блока 1 постоянной памяти и является адресным входом устройства, вход выборки является управляющим входом устройства, а выход подключен к вхрду синхронизации регистра 3, вход сброса которого является входом сброса устройства, а вход данных подключен к выходу сумматора 2, вход первого операнда которого подключен к n-разрядному информационному входу устройства, а вход второго операнда - к выходу регистра 3, а также (та+1)- раз рядный сумматор 5 по модулю два и триггер 6, выход которого является выходом устройства, вход синхронизации подключен к выходу дешифратора 4, вход сброса - к входу сброса регистра 3, а информационный вход - к выходу (т+1)-разрядного сумматора 5 по модулю два, первый вход которого подключен к выходу блока 1 постоянной памяти, а остальные - к выходу сумматора 2. Причем блок 1 постоянной памяти выполнен одноразрядным, а сумматор 2 и регистр 3 - m-разрядиымп, ; де . Неиспользуемые старшие разряды

0

5

0

5

0

5

0

5

входа первого операнда сумматора 2 подключены к линии логического О.

Для реализации своих функций устройство подключается к контролируемой микропроцессорной системе, стандартно содержащей микропроцессор 7 и память 8 команд, соединенные между собой по- ср1аД -1 вом шин адреса 9, данных 10 и управления 11. При этом адресный вход устройства соединяется с шиной 9 адреса системы, n-разрядный информационный вход - с шиной 10 данных, а управляющий вход - с линией Чтение шины 11 управления.

Устройство работает следующим образом .

Пусть необходимо контролировать ход программы микропроцессорной системы. Программа представляет собой совокупность команд и хранится в памяти 8 команд. В качестве последней рбычно используют постоянное запоминающее устройство. Каждая команда за- |нимает от одной до нескольких соседних ячеек памяти и информационно характеризуется массивом п-разрядных слов (байтов).

Процесс воспроизведения программы заключается в последовательном (шаг за шагом) извлечении микропроцессором 7 из памяти 8 команд слов программы, декодировании и реализации предписанных операций. При этом на каждом шаге программы извлечение очередного слова сопровождается тем,что на шине 9 адреса системы устанавливается адрес указанного слова. Затем на шине II управления генерируется сигнал Чтение, по которому адресуесистемы и принимается микропроцессором 7 на декодирование.

Для обеспечения контроля в предлагаемом устройстве каждому адресу (каждой точке) программы становится в соответствие некоторое контрольное га-разрядное число. Указанное число фактически является суммой всех слов программы, которые в процессе корректных вычислений извлекаются из памяти 8 команд системы к моменту прохождения программы через соответствую10

некотором шзге программы. В процессе реализации указанного шага на адресный вход устройства и, следовательно, на вход блока 1 постоянной памяти подается адрес, по которому в микропроцессорной системе из памяти 8 команд извлекается очередное слово программы. Это обеспечивает появление на выходе блока 1 постоянной памяти одноразрядного контрольного кода, соответствующего данной точке программы. Затем микропроцессор 7 генерирует

щую точку. При этом в блоке 1 посто- 15 на шине И управления, сигнал Чтение,

янной памяти еще до начала вычислений размешаются однозарядные коды, которые дополняют контрольные числа до (т+1)-разрядных кодов, содержащих четное количество единиц.

В процессе реализации программы сумматор 2 осуществляет суммирование всех п-разрядных слов программы с га-разрядными суммами из регистра 3. В результате этого в каждой точке программы вычисляется га-разрядный двоичный код текущей суммы. Указанный код с учетом дополнительного разряда, значение которого извлекается из блока 1 постоянной памяти по текущему адресу программы, дополняется до (т+1)-разрядного и проверяется на четность. Если количество единиц в полученном коде нечетно, то Ликсиру- ется ошибка.

В процессе корректных вычислений текущие суммы всегда дополняются до четных кодов, т.е. соблюдается условие четности иошибка не Ликсируется.

который активирует память 8 команд. В результате этого из памяти 8 команд на шину 10 данных передается текущее n-разрядное слово программы. Данное

20 слово через информационный вход устройства поступает на вход первого операнда сумматора 2 и складывается с m-разрядным числом с выхода регистра 3, которое представляет собой сум25 му всех ранее поступивших в устройство слав программы и явллгтея предыдущей контрольной суммой.

В результате сложения текущего слова программы и предыдутпей суммы

30 на выходе сумматора 2 Нормируется текущая контрольная сумма, т-рлзрядшш код текущей суммы и одноразрядный контрольный код с выхода f-лока 1 постоянной памяти образуют (тп-Н ) -разрядный код, который поступает в сумматор 5. Если указанный код содержит четное количество единиц (такая ситуация возникает, например, когда те- кушая сумма корректна), сумматор 5

35

При нарушении хода программы возника-до Ф°РмиРУет нулевой сигнал, который ет несоответствие между суммами и до- свидетельствует о том, что на данном полнительными разрядами. Причем ука- шаге программы ошибка не обнаружена. занное несоответствие зарождается в Однако указанный сигнал достовё- момент сбоя и затем сохраняется в те- рен только в момент окончания в контчение длительного времени. Это объяс-д5 Р°лиРУемои системе операции чтения

текущего слова программы из памяти 8 команд. Это связано с наличием естественных задержек и переходных процессов в памяти 8 команд, сумматоре

няется тем, что при добавлении к однажды полученной некорректной сумме корректного кода (слова программы) результат все равно остается некорректным. Таким образом, в устройстве генерируется поток некорректных сумм. При этом несмотря на то, что часть из этих сумм с учетом дополнительного разряда может удовлетворять условно четности, в конце концов наступает момент, когда указанное ус- яовие не выполняется, т.е. фиксируется ошибка и на выходе устройства появляется соответствующий сигнал.

некотором шзге программы. В процессе реализации указанного шага на адресный вход устройства и, следовательно, на вход блока 1 постоянной памяти подается адрес, по которому в микропроцессорной системе из памяти 8 команд извлекается очередное слово программы. Это обеспечивает появление на выходе блока 1 постоянной памяти одноразрядного контрольного кода, соответствующего данной точке программы. Затем микропроцессор 7 генерирует

на шине И управления, сигнал Чтение,

который активирует память 8 команд. В результате этого из памяти 8 команд на шину 10 данных передается текущее n-разрядное слово программы. Данное

слово через информационный вход устройства поступает на вход первого операнда сумматора 2 и складывается с m-разрядным числом с выхода регистра 3, которое представляет собой сумму всех ранее поступивших в устройство слав программы и явллгтея предыдущей контрольной суммой.

В результате сложения текущего слова программы и предыдутпей суммы

на выходе сумматора 2 Нормируется текущая контрольная сумма, т-рлзрядшш код текущей суммы и одноразрядный контрольный код с выхода f-лока 1 постоянной памяти образуют (тп-Н ) -разрядный код, который поступает в сумматор 5. Если указанный код содержит четное количество единиц (такая ситуация возникает, например, когда те- кушая сумма корректна), сумматор 5

Р°лиРУемои системе операции чтения

текущего слова программы из памяти 8 команд. Это связано с наличием естественных задержек и переходных процессов в памяти 8 команд, сумматоре

2 и сумматоре 5. Кроме того, при выполнении микропроцессором 7 операций, не связанных с извлечением текущего слова программы из памяти 8 команд, на шинах адреса 9 и данных 10 снстемы устанавливаются произвольные коды, которые могут приводить к ложному срабатыванию сумматора 5.

Для получения достоверного результата с выхода сумматора 5 устройстпо

ыявляет Факт обращения микропроцесора 7 к памяти 8 команд. Указанная ункция реализуется дешифратором 4, оторый срабатывает при появлении на г ине 9 системы адреса памяти 8 ко--. анд, а на шине 11 управления - сигала Чтение, импульс с выхода деифратора 4 поступает на вход синхонизации триггера 6. По заднему Q ронту указанного импульса, свидеельствующего об окончании текущей перации чтения памяти 8 команд,тригер 6 фиксирует информацию с выхода умматора 5. Поскольку в этот -I- $ омент времени на выходе суматора 5 находится достоверная инормация (переходные процессы в си.- теме и устройстве закончились.) , то в триггере 6 и, соответственно, на вы 20 ходе устройства фиксируется резу.гь- тат контроля текущей суммы.

Одновременно по заднему фронту импульса с выхода дешифратора 4 в регистр 3 с выхода сумматора 2 заносит- 25 ся текущая сумма, которая сохраняется до следующего иага программы (становится предыдущей) . На следукнцем шаге программы устройства выполняются аналогичные действия н т.д. В ре- 30 зультате этого при правильной реализации программы текущие суммы в совокупности с дополнительными разрядами всегда удовлетворяют условию четности. Это постоянно фиксируется тригге- 35 тькг ром 6, и на выходе устройства не появляется сигнал ошибки.

Нарушение нормального хода программы может быть вызвано, например, сбоем счетчика команд в микропропес- 40 соре 7 или отказом адресных линий в шине 9 адреса. Это приводит к искажению информации на шине 9 адреса и нарушению последовательности выбора слов программы (ложный переход). Кро- 45 ме -того, возможны отказы ячеек памяти 8 команд и отказы линий связи в шине 10 данных. Это приводит к чтению некорректных слов программы из памяти 8 команд системы (ложный код коман- 50 ды). Устройство обеспечивает выявление подобных нарушений нормального хода программы с высокой степенью достоверности .

Действительно, пусть в некоторый 55 момент времени произошел ложный переход прогртммы. В результате этого на адгегный вход устройств- ;i.-r i ет неверный адрес, м ког. ч , иблокся о

вход вующ кома на в куще ния 8 ко полн

I допо блюд рует

быти

равн данн ной что нг. прог F4

полн jj/,

, м веро чере

ложн ка н

след не о расс ций 2-я прог ка н то 3 прог но о туац жени опре

Анал полу

Отсю чест

блока 1 постоянной памяти извлекается одноразрядный код.

Одновременно на информационный вход устройства подается соответствующее слово программы из памяти 8 команд, что приводит к формированию на выходе сумматора 2 некоторой текущей суммы. Тогда на момент окончания в системе операции чтения памяти 8 команд может иметь место следующая полная группа событий:

I) текущая сумма не соответствует дополнительному разряду, т.е. не соблюдается условие четности и фиксируется ошибка; вероятность такого со тькг

бытия Р 0,5;

2)текущая сумма случайно оказалась равной той, которая соответствует данной точке программы при корректной реализации вычислений; очевидно, что такой сбой не будет обнаружен ни нг. текущем, ни на следующих шагах программы; вероятность этого события F4 i/2m;

3)текущая сумма соответствует дополнительному разряду; сбой не обна- jj/, икается на данном шаге программы,

, может быть обнаружен на следующих; вероятность этого события обозначим через РЭ.

Таким образом, на первом после ложного перехода шаге программы ошибка не будет обнаружена с вероятнос тькг

Рп

р

ГЭ 2т

+ Р:

МЧ 42. 1Э 2т V Рассмотрим работу устройства на следующем шаге программы, если ошибка не обнаружена на предыдущем, т.е. рассмотрим развитие 2-й и 3-й ситуаций. Очевидно, что если имела место 2-я ситуация, то на следующем шаге программы она сохраняется, т.е. ошибка не обнаруживается. Если имела место 3-я ситуация, то на новом шаге программы с равной вероятностью можно ожидать появление 1-й либо 3-й ситуации. Тогда вероятность необнаружения ошибки за два шага программы определится как

Р -- + О 5 Р 2Ч 2№ u,3tV

Аналопгчно для i-го шага программы получим

2m +

0,5

Р

- 2 J L Ъ очевидно, что с ростом колитагов программы величину Р:

быстро падает и устремляется к величине

Р

н

) Т1 )

характеризующей вероятность необнаружения ошибки устройством в целом.

Аналогичным образом устройство работает при обнаружении некорректных кодов программы. При этом 2-я ситуа- ция никогда не имеет места (иначе поступающее слово программы является корректным). Поэтому вероятность обнаружения искажения одиночного слова программы в устройстве равно единице.

Таким образом, в устройстве обнаруживаются практически все некорректные переходы (исключая лшгь случай совпадения текущей суммы с корректной) и искажения КОДОР программы.

В случае обнаружен1---. ошибки нт, выходе сумматора 5 образуется единичный сиг-нал. В результате этого г мг- мент окончания операции чтения памяти 8 команд системы триггер 6 пере- ходит в едишгчное состоя ие и рует на выходе устройства сигнал ошибки. Указанный сигнал может быть использован в контролируемой системе для запуска, например, по прерыванию программы устранения ошибки. В процессе обработки прерывания микропроцессор 7 системы обеспечивает подачу на вход сброса устройства сигнала начальной установки. Указанный сигнал поступает на регистр 3 и триггер ft и производит обнуление (очистку) „ контрольной суммы, и результата контроля. После того, K.IK сигчал начальной установки снимается, устройство вновь готово к работе. Аналогичным образом происходит очистка устройства в процессе начального запуска (сброса) контролируемой системы.

Использование предлагаемого

устройства налагает некоторые ограничения на программирование микропроцессорной системы. Чез учета этих ограничений в устройстве обеспе- чивается контроль лишь линейных уча- стков программы. Линейный участок программы при широко распространенном структурном подходе к программированию называется базовой структурой Следование. Однако этой структуры недостаточно, чтобы представить даже самые простые практические программы. Логическая структура сколь угодно сложной программы может быть

выражена комбинацией трех базовых структур: к указанной структуре Следование добавляется структура Развилка и иикл (Лиг. 2) . При этом последняя может иметь две разновидности. Очевидно, что внутри базовых структур Развилка и Пикл осуществляется ветвление вьгчислительного процесса с последующим объединением ветвей.

Объединение ветвей программы осуществляется обращением по одному и тому же адресу после прохода ветвей программы. Суммы кодов команд (слов программы), находящихся в различных ветвях, в обшем случае не совпадают. В результате этого при объединении ветвей программы без принятия дополнительных мер устройство фиксирует ошибку программы, хотя таковой нет. Для исключения этого явления необходимо искусственно выравнивать текущие суммы слов программы перед каждым объединением ветвей. Что легко обеспечиваете я путем размещения перед каллой точкой объединения ветвей дополнительных управляющих команд (уравнивающих блоков), HP имеющих функционального значения с точки зрения процесса решения задачи, реализуемой микропроцессорной системой.

Значение уравнивающих чисел может быть различным в различных ветвях прог раммы. В простейшем случае уравнивание сумм мочет осуществляться до нулевого значения. При этом вход в каждую точку слияния ветвей программы происходит с нулевым значением контрольной гуммы, т.е. нулевым состоянием регистра 3. Наиболее просто обнуление сумм может быть реализовано путем подачи на вход сброса устройства соответствующего сигнала в момент исполнения программой уравнивающего блока. При подключении устройства к системе, построенной на базе микропроцессора КР580, такое директивное уравнение реализуется программным блоком, состоящим из двух команд: Запрещение прерывания1. и Разрешение прерывания(1П, EI) . В процессе исполнения этих команд на выходе мик- ропропессора появляется 1гмпульс, который поступает на вход сброса vстрой с тва и осуществляет обнуление суммы.

Однако использование директирчп- го уравнивания снижает достоверность

контроля устройства. Это связано с тем, что часть ложных переходов программы не будет обнаружена, поскольку в результате такого уравнивания возникающие после сбоя некорректные суммы могут принимать нулевые (корректные) значения еще до момента фиксации ошибки на выходе устройства.

Для устранения указанного недостатка необходимо применять естественное уравнивание путем суммирования кодов команд уравнивающих блоков (вход сброса устройства не возбуждается) .

В качестве контрольных сумм точек слияния ветвей программы в этом случае рационально принимать не нулеы , а такие суммы, которые получаются естественном прохождении программой одной из сходящихся ветвей. Это дает возможность исключить из указанных ветвей уравнивающие блоки. Описанный способ уравнивания контрольных сумм различных ветвей программы может быть использован и при вызове подпрограмм. Для этого достаточно обнулять контрольные суммы непосредственно перед вызовом подпрограмм и уравнивать до нулевого значения контрольные суммы самих подпрограмм. При этом уравнивающие блоки программируются вручную или автоматически с помощью транслятора.

0

5

0

5

Формула изобретения

Устройство для контроля хода программ, содержащее блок постоянной памяти, регистр, сумматор и дешифратор, причем адресный вход устройства соединен с адресным входом блока постоянной памяти, информационный вход устройства соединен с входом первого операнда сумматора, выход которого соединен с информационным входом регистра, выход которого соединен с входом второго операнда сумматора, вход начальной установки устройства соединен с нулевым входом регистра, отличающеес я тем, что, с целью упрощения устройства, в него введены (тп + 1)-разрядный сумматор по модулю два (где m-разрядность контролируемого кода) и триггер, причем адресный вход устройства соединен с информационным входом дешифратора, вход выборки которого является управляющим входом устройства, выход дешифратора соединен с входом записи регистра и тактовым входом триггера, выход которого является выходом ошибки устрой- f , тп-разрядный выход сумматора соединен соответственно с первыми m-входами сумматора по модулю два, выход блока постоянной памяти соединен с (т-Н)-м входом сумматора по модулю два, выход которого соединен с информационным входом триггера, вход начальной установки устройства соединен с нулевым входом триггера.

| Цифровой генератор периодических сигналов | 1984 |

|

SU1191904A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1300479, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1988-05-12—Подача