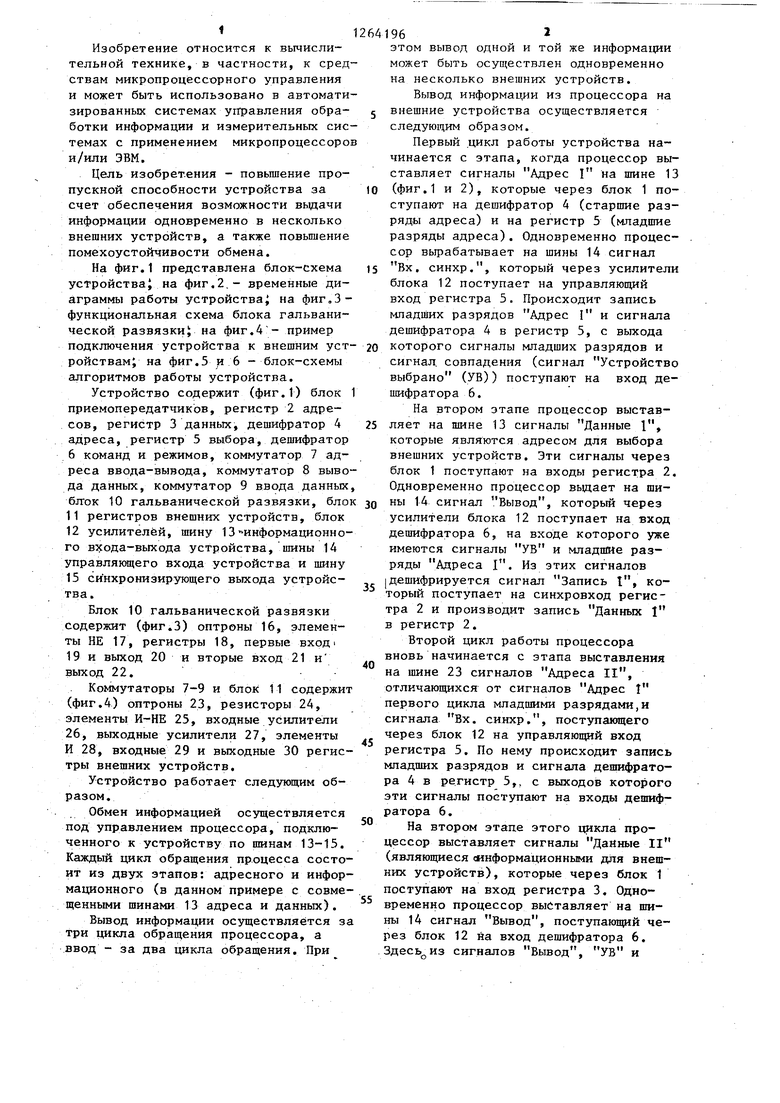

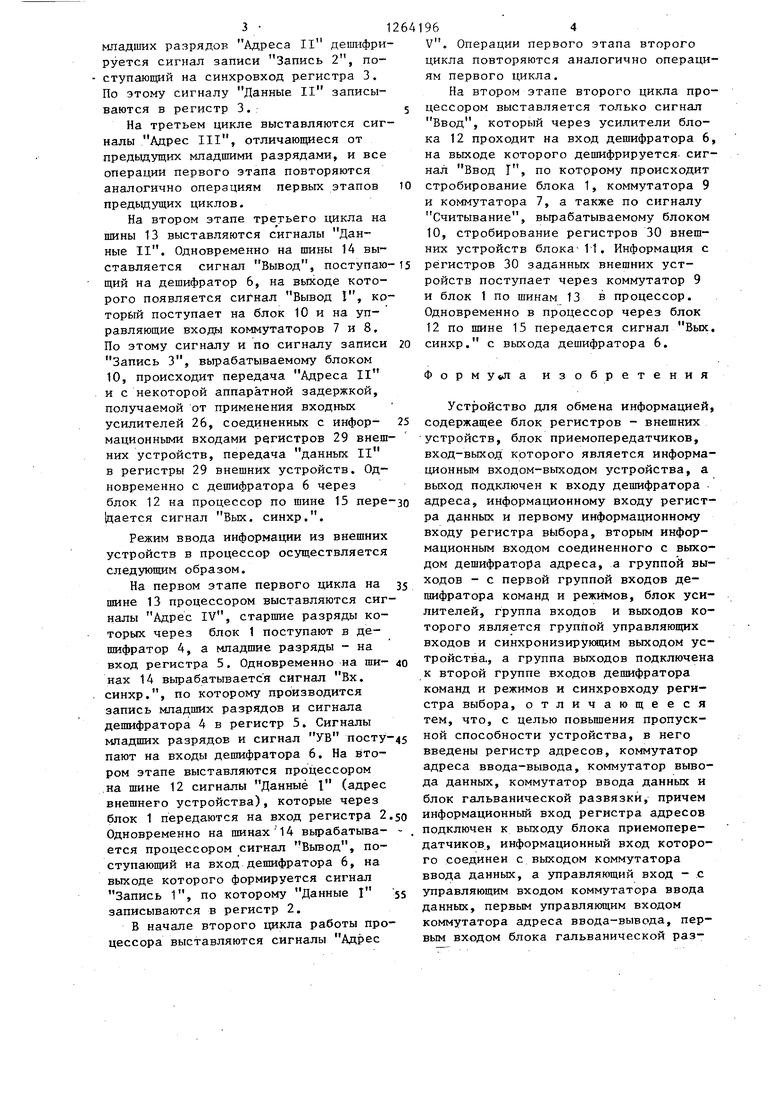

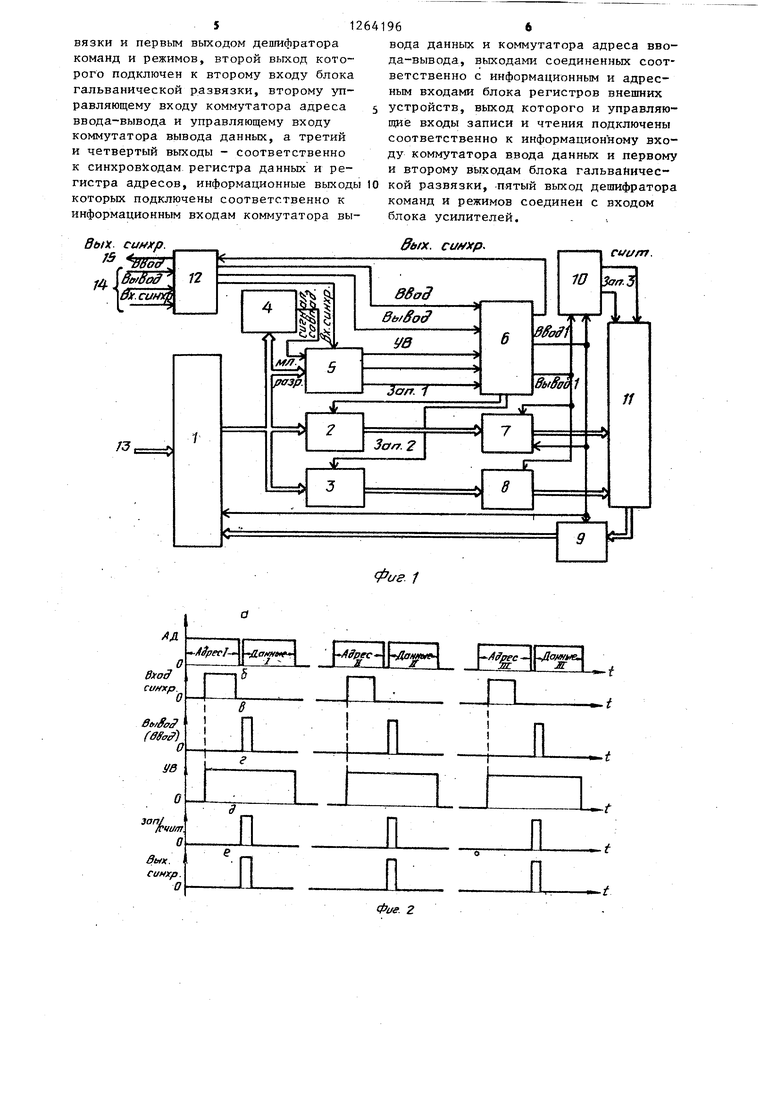

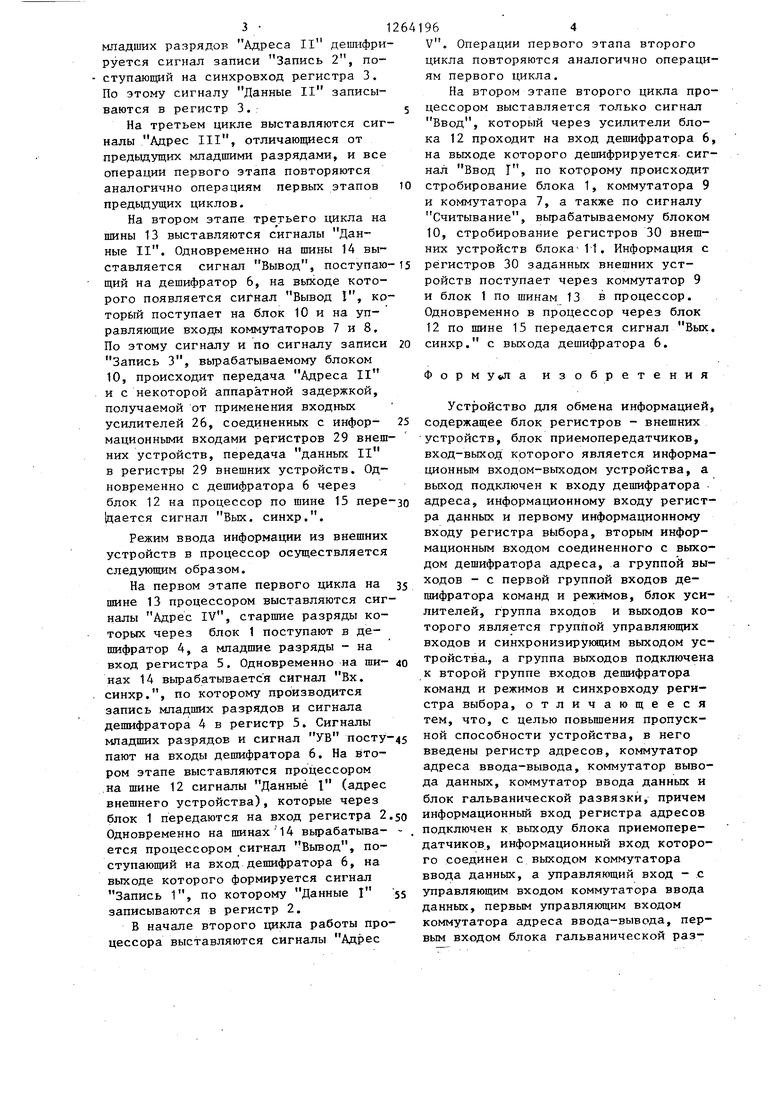

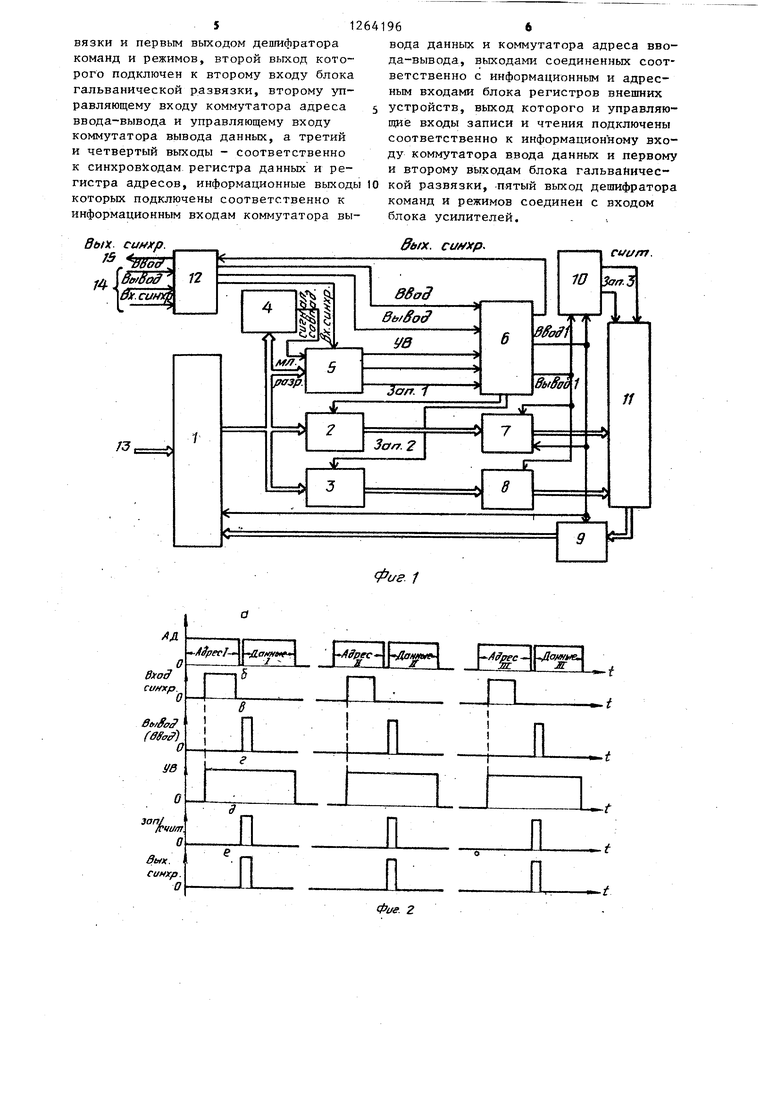

Изобретение относится к вычислительной технике, в частности, к сред ствам микропроцессорного управления и может быть использовано в автомати зированных системах управления обработки информации и измерительных сис темах с применением микропроцессоро и/или ЭВМ. Цель изобретения - повышение пропускной способности устройства за счет обеспечения возможности вьщачи информации одновременно в несколько внешних устройств, а также повышение помехоустойчивости обмена. На фиг.1 представлена блок-схема устройстваJ на фиг.2.- временные диаграммы работы устройства на фиг,3функциональная схема блока гальванической развязкиi на фиг.4 - пример подключения устройства к внешним уст ройствам; на фиг.5 и 6 - блок-схемы алгоритмов работы устройства. Устройство содержит (фиг.1) блок приемопередатчиков, регистр 2 адресов, регистр 3 данных, дешифратор 4 адреса, регистр 5 выбора, дешифратор 6 команд и режимов, коммутатор 7 адреса ввода-вывода, коммутатор 8 выво да данных, коммутатор 9 ввода данных блок 10 гальванической развязки, бло 11регистров внешних устройств, блок 12усилителей, шину 13 информационного входа-выхода устройства, шины 14 управлякнцего входа устройства и шину 15 синхронизирующего выхода устройства. Блок 10 гальванической развязки содержит (фиг.З) оптроны 16, элементы НЕ 17, регистры 18, первые входi 19 и выход 20 и вторые вход 21 и выход 22. Коммутаторы 7-9 и блок 11 содержи (фиг.4) оптроны 23, резисторы 24, элементы И-НЕ 25, входные усилители 26, выходные усилители 27, элементы И 28, входные 29 и выходные 30 регис тры внешних устройств. Устройство работает следующим образом. Обмен информацией осуществляется под управлением процессора, подключенного к устройству по шинам 13-15. Каждый цикл обращения пр.оцесса состо ит из двух этапов: адресного и инфор мационного (в данном примере с совме щенными шинами 13 адреса и данных). Вывод информации осуществляется з три цикла обращения процессора, а ввод - за два цикла обращения. При 96 этом вывод одной и той же информации может быть осуществлен одновременно на несколько внешних устройств. Вывод информации из процессора на внешние устройства осуществляется следующим образом. Первый цикл работы устройства начинается с этапа, когда процессор выставляет сигналы Адрес I на шине 13 (фиг.1 и 2), которые через блок 1 поступают на дешифратор 4 (старшие разряды адреса) и на регистр 5 (м.падшие разряды адреса). Одновременно процессор вырабатывает на шины 14 сигнал Вх. синхр., который через усилители блока 12 поступает на управляющий вход регистра 5. Происходит запись младших разрядов Адрес Г и сигнала дешифратора 4 в регистр 5, с выхода которого сигналы младших разрядов и сигнал, совпадения (сигнал Устройство выбрано (УВ)) поступают на вход дешифратора 6. На втором этапе процессор выставляет на шине 13 сигналы Данные 1, которые являются адресом для выбора внешних устройств. Эти сигналы через блок 1 поступают на входы регистра 2. Одновременно процессор вьщает на шины 14 сигнал Вывод, который через усилители блока 12 поступает на вход дешифратора 6, на входе которого уже имеются сигналы УВ и младпме разряды Адреса 1, Из этих сигналов Дешифрируется сигнал Запись I, который поступает на синхровход регистра 2 и производит запись Данных 1 в регистр 2. Второй цикл работы процессора вновь начинается с этапа выставления на шине 23 сигналов Адреса II, отличающихся от сигналов Адрес I первого цикла младшими разрядами,и сигнала Бх. синхр., поступающего через блок 12 на управляющий вход регистра 5. По нему происходит запись младших разрядов и сигнала дешифратора 4 в регистр 5,, с выходов которого эти сигналы поступают на входы дешифратора 6. На втором этапе этого процессор выставляет сигналы Дайные II (являющиеся «информационными для внешних устройств), которые через блок 1 поступают на вход регистра 3. Одновременно процессор выставляет на шины 14 сигнал Вывод, поступающий через блок 12 на вход дешифратора 6. Здесь из сигналов Вывод, УВ и

3

младших разрядов Адреса II дешифрируется сигнал записи Запись 2, поступающий на синхровход регистра 3. По этому сигналу Данные II записываются в регистр 3.

На третьем цикле выставляются сигналы Адрес III, отличающиеся от предьщущих младшими разрядами, и все операции первого этапа повторяются аналогично операциям первых этапов предыдущих циклов.

На втором этапе третьего цикла на шины 13 выставляются сигналы Данные II. Одновременно на шины 14 выставляется сигнал Вывод, поступаю щий на дешифратор 6, на выходе которого появляется сигнал Вывод I, который поступает на блок 10 и на управляющие входы коммутаторов 7 и 8. По этому сигналу и по сигналу записи Запись 3, вырабатываемому блоком 10, происходит передача Адреса II и с некоторой аппаратной задержкой, получаемой от применения входных усилителей 26, соединенных с информациокными входами регистров 29 внешних устройств, передача данных II в регистры 29 внешних устройств. Одновременно с дешифратора 6 через блок 12 на процессор по шине 15 пере дается сигнал Вых. синхр..

Режим ввода информации из внешних устройств в процессор осуществляется следующим образом.

На первом этапе первого цикла на шине 13 процессором выставляются сигналы Адрес IV, старшие разряды которых через блок 1 поступают в дешифратор 4, а младшие разряды - на вход регистра 5. Одновременно на шинах 14 вырабатывается сигнал Вх. синхр., по которому производится запись мпадших разрядов и сигнала дешифратора 4 в регистр 5. Сигналы мпадших разрядов и сигнал УВ поступают на входы дешифратора 6, На втором этапе выставляются процессором .на шине 12 сигналы Данные 1 (адрес внешнего устройства), которые через блок 1 передаются на вход регистра 2 Одновременно на шинах14 вьфабатывается процессором сигнал Вьшод, поступающий на вход дешифратора 6, на выходе которого формируется сигнал Запись 1, по которому Данные 1 записываются в регистр 2.

В начале второго цикла работы процессора выставляются сигналы Адрес

1964

V. Операции первого этапа второго цикла повторяются аналогично операциям первого цикла.

На втором этапе второго цикла процессором выставляется только сигнал Ввод, который через усилители блока 12 проходит на вход дешифратора 6 на выходе которого дешифрируется- сигнал Ввод I, по которому происходит стробирование блока 1, коммутатора 9 и коммутатора 7, а также по сигналу Считывание, вырабатываемому блоком 10, стробирование регистров 30 внешних устройств блока 11. Информация с регистров 30 заданных внешних устройств поступает через коммутатор 9 и блок 1 по шинам 13 в процессор. Одновременно в процессор через блок 12 по шине 15 передается сигнал Вых синхр. с выхода дешифратора 6.

Форм а изобретения

Устройство для обмена информацией содержащее блок регистров - внешних устройств, блок приемопередатчиков, вход-выход которого является информационным входом-выходом устройства, а выход подключен к входу дешифратора адреса, информационному входу регистра данных и первому информационному входу регистра выбора, вторым информационным входом соединенного с выходом дешифратора адреса, а группой выходов - с первой группой входов дешифратора команд и режимов, блок усилителей, группа входов и выходов которого является группой управляющих входов и синхронизирукяцим выходом устройства, а группа выходов подключена к второй группе входов дешифратора команд и режимов и синхровходу регистра выбора, отличающееся тем, что, с целью повьштения пропускной способности устройства, в него введены регистр адресов, коммутатор адреса ввода-вывода, коммутатор вывода данных, коммутатор ввода данных и блок гальванической развязки, причем информационный вход регистра адресов подключен к выходу блока приемопередатчиков., информационный вход которого соединен с выходом коммутатора ввода данных, а управляющий вход - с управляющим входом коммутатора ввода данных, первым управляющим входом коммутатора адреса ввода-вывода, первым входом блока гальванической развязки и первым выходом дешифратора команд и режимов, второй выход которого подключен к второму входу блока гальванической развязки, второму управляющему входу коммутатора адреса ввода-вывода и управляющему входу коммутатора вывода данных, а третий и четвертый выходы - соответственно к синхров}содам регистра данных и регистра адресов, информационные выходы 10 кой

которых подключены соответственно к информационным входам коммутатора выBbi)i. cuffxp. ,Bo(f 1

команд и режимов соединен с входом блока усилителей.

Фиг. 1 966 вода данных и коммутатора адреса ввода-вывода, выходами соединенных соответственно с информационным и адресным входами блока регистров внешних устройств, выход которого и управляющие входы записи и чтения подключены соответственно к информационному входу коммутатора ввода данных и первому и второму выходам блока гальвайичесразвязки, пятый выход дешифратора fftitX. CUf/Xp. си и т.

Ус/rfflaucmfo ofmtef/a

t/f OpMCHfUfU

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1987 |

|

SU1481781A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для межмашинного обмена | 1986 |

|

SU1312589A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для обмена информацией между микро ЭВМ и периферийными устройствами | 1983 |

|

SU1195351A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

Изобретение относится к вьгаислительной технике и мсжет быть применено и вычислительных системах для обмена даннь&ш между микропроцессором (микроэвм) и внешними устройствами. Целью изобретения является повышение пропускной способности устройства и помехоустойчивости обмена. Поставленная цель достигается тем, что в устройство, содержащее блок приемопередатчиков, блок усилителей, дешифратор адреса, дешифратор команд и режимов, блок регистров внешних устройств, регистр выбора и регистр данных, введены регистр адресов, коммутаторы адреса ввода-вывода, ввода и вывода данных и блок гальванической развязки. 6 Ш1. (П С

| Устройство для ввода-вывода | 1978 |

|

SU737937A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переплетный станок | 1928 |

|

SU11739A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-03-04—Подача