«

Изобретение относится к вычислительной технике, а именно к устройствам для получения управляемой в ншроких пределах задержки импульсов при сохранении их параметров.

Цель изобретения - расширение функциональных возможностей путем . сохранения длительностей входных импульсов и пауз и за счет обеспечения работы в условиях отсутствия синхронизации входных импульсов тактовыми импульсами устройства, а также сокращение объема оборудования

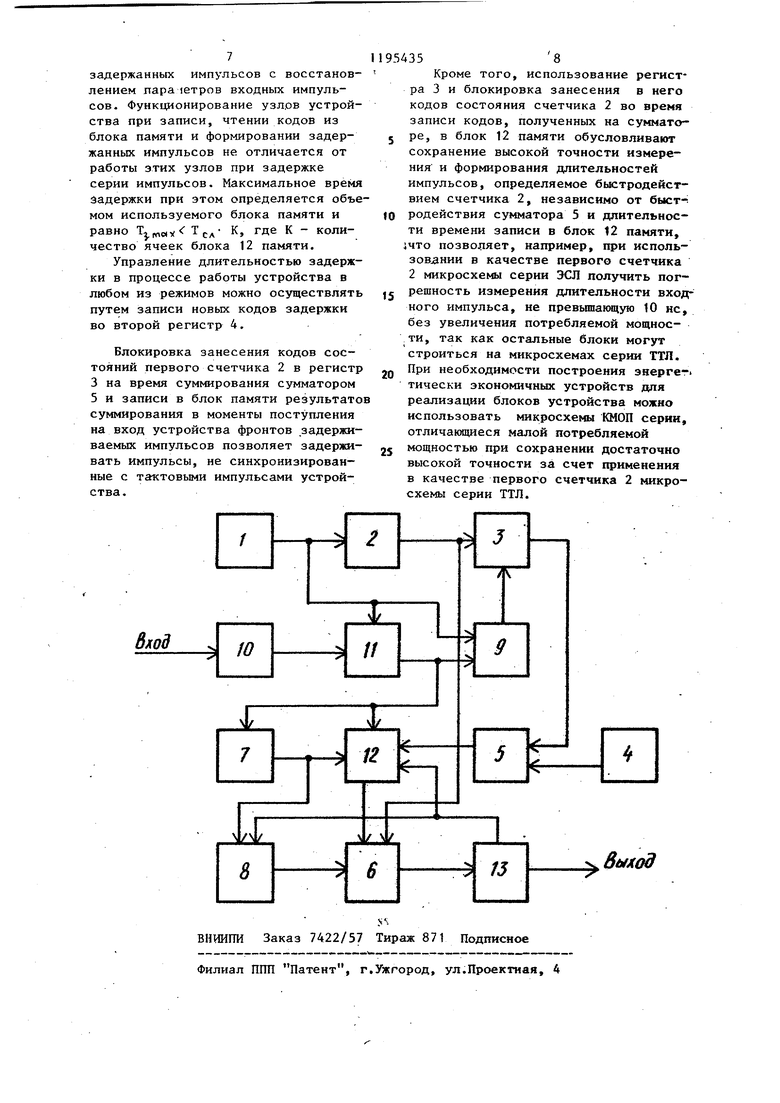

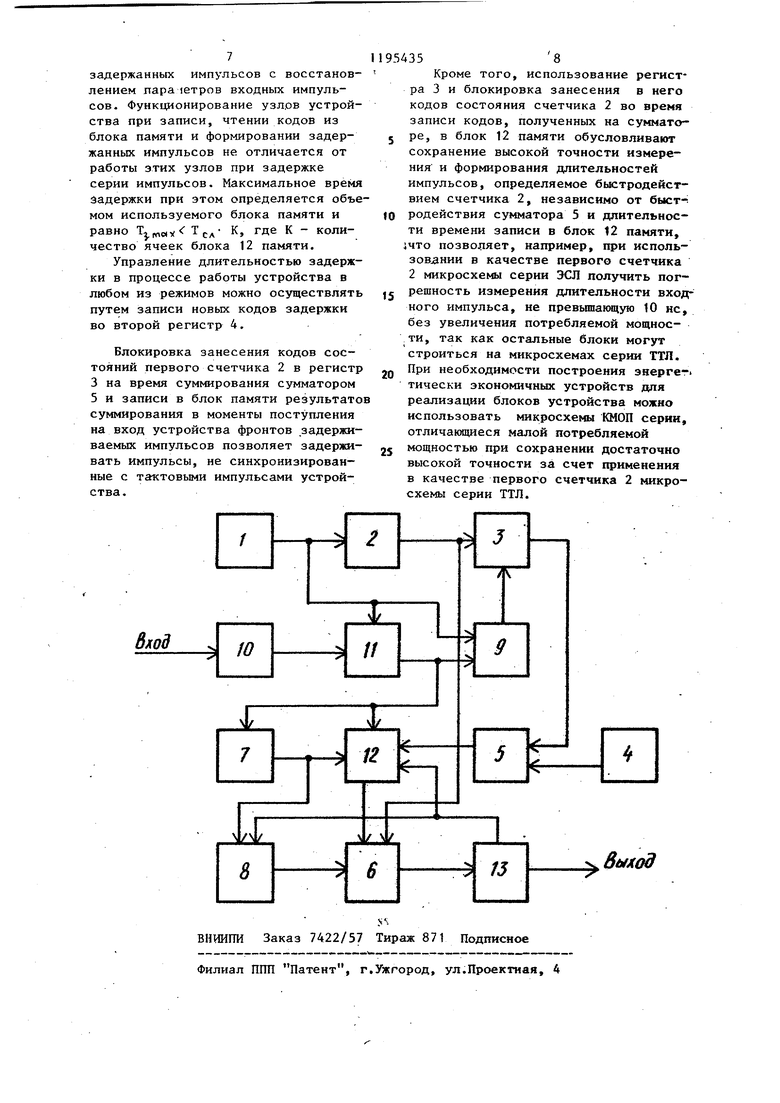

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит генератор 1 импульсов, первый счетчик 2, первый 3 и второй 4 регистры, сумматор 5, первый элемент 6 сравнения, второй счетчик 7, второй элемент 8 сравнения, элемент И 9, формирователь 10 импульсов, триггер 11, блок 12 памяти и третий счетчик 13. Выход генетратора 1 импульсов, соединен с входом первого счетчика 2, первым входом триггера 11 и первым входом элемента И 9. Выход первого счетчика 2 соединен с входом первого регистра 3 и первым входом первого элемента 6 сравнения. Второй вход первого регистра 3 подключен к выходу элемента И 9, выход - к первому входу сумматора 5, второй вход которого соединен с выходом второго регистра 4,а выход - с вторым входом блока 12 памяти. Вход устройства подключен к входу формирователя 10 импульсов, выход которого соединен с вторым входом триггера 11. Выход триггера

11соединен с первьм входом блока

12памяти, входом второго счетчика

7 и вторым входом элемента И 9. Первый вход второго элемента 8 сравнения подключен к выходу второго счетчика 7 и третьему входу блока 12 памяти, второй вход - к первому выходу второго счетчика 13 и четвертому входу блока 12 памяти, выход к третьему входу первого элемента 6 сравнения, второй вход которого соединен с выходом блока 12 памяти, а выход - с входом третьего счетчика 13, второй выход которого является выходом устройства.

Генератор 1 импульсов формирует последовательность тактовых импульсов и может быть построен на микросхеме 155АГ1.

954352

Первый 2, второй 7 и третий 13 счетчики по каждому из импульсов, поступающих на их входы, увеличивают, свое состояние на единицу и могут

5 строится на микросхемах 155 ИЕ7.

Первый вход первого регистра 3 информационный, второй - вход синхронизации занесения, выходы первого 3 и второго 4 регистров - инШ формационные. В качестве регистров 3 и 4 можно использовать микросхе-. мы 155 ТМВ.

Сумматор 5 комбинационного типа, его входы и выход - информационные.

15 В качестве сумматора 5 можно использовать микросхему 155 ИМЗ.

Первый элемент 6 сравнения формирует на своем выходе импульс при равенстве кодов на его первом и

20 втором входах и при наличии сигнала разрешения сравнения на его третьем входе. Второй элемент В сравнения формирует на своем выходе сигнал разрешения сравнения для

25 первой схемы 8 сравнения, если удовлетворяется условие А чт где А. и Ац.р - коды, поступакщие соответственно на его первый и второй входы (коды адресов записи и

30 чтения блока 12 памяти). Для построения элементов сравиения можно использовать микросхему 531СА1, при этом выходной сигнал равенства второго элемента 8 сравнения необходимо проинвертировать.

Формирователь 10 импульсов по переднему и заднему фронтам входного импульса формирует короткие импульсы, длительность которых определя. ется суммой времени суммирования в сумматоре 5 и времени записи и в блок 12 памяти. В качестве формирователя 10 можно использовать два элемента микросхемы 155АГЗ, из которых один формирует импульс по переднему фронту входного импульса, второй - по заднему, выходы обоих формирователей объединены через элемент ИЛИ (например, 155ЛЛ1).

В качестве элемента И 9 можно использовать микросхему 155.ПАЗ.

Триггер 11 - D типа, например, 155ТМ2. Его первый вход - вход синхронизации, второй - вход D, а выход - инверсный.

Первый вход блока 12 памяти вход разрешения записи, второй информационный, третий - вход адреса записи, четвертый - вход адреса чтения, выход - информационный, В качестве блока 12 памяти можно использовать микросхему 1802ИР1.

В исходном состоянии содержимые второго 7 и третьего 13 счетчиков равны, в младшем разряде каждого из них имеется код О,а во второй регистр 4 заносится начальный код задержки. Первый счетчик 2 цикли;чески изменяет свое состояние по последовательности тактовых импуль.сов, поступающих на его вход с выхода генератора 1 импульсов. В регистр 3 переписываются состояния первого счетчика 2. На сумматоре 5 происходит непрерывное суммирование текуп х состояний первого счетчика 2, поступаю1 х с выхода первого регистра 3, с кодом задержки, хранящемся во втором регистре 4.

При работе устройства возможен ря ситуаций. В первом случае на вход устройства поступает серия случайных (в общем случае) импульсов. Предположим, что в некоторьм момент оба адресных счетчика 8 и 13 находились в i-M состоянии. Тогда в блок памяти по i-му адресу записьтается код су1. относительного времени прихода входного импульса, фиксированного в регистре 3, с кодом задержки, хранш«лм в регистре 4. Происходит это следуюп им образом. При поступлении на вход устройства первого задерживаемого импульса по его переднему фронту на выходе формирователя 10 импульсов формируется импульс, поступающий на вход D-триггера 11, и следующим тактовым импульсом этот триггер устанавливается в единичное состояние на время, необходимое для записи в блок 12 памяти кода, полученного в сумматоре 5 в результате суммирования кода задержки Tj,, с относительным временем поступления входного импульса Т.

Во время нахождения триггера 11 в единичном состоянии нулевым уровне с его инверсного выхода происходит запрещение занесения последующих состояний счетчика 2 в первый регистр 3, а также разрешается зйпись в блок 12 памяти по i-му адресу, поступающему с выхода второго счетчи ка 2, кода Т + Т, где Т - код относительного времени поступления на вход устройства задерживаемого

импульса, зафиксированный в первом регистре 3; Та, - код задержки, хранящийся во втором регистре 4. По окончании длительности импульса, сформированного формирователем 10 импульсов, триггер 11 устанавливается очередным тактовь«м импульсом в исходное состояние, второй счетчик

7увеличивает свое состояние на единицу, формируя следующий адрес записи в блок 12 памяти, элемент И 9 открывается по второму входу, разрешая -.занесение по каждому тактовому импульсу текущих состояний первого счетчика в первом регистре 3. Неравенство состояний второго 7 и треть его 13 счетчиков обуславливает формирование на выходе второго элемент

8сравнения сигнала, разрешакицего первому элементу 6 сравнения осуществлять сравнение текушрх состояний первого счетчика 2, поступающих на его первый вход, с кодом суммы Т j. + Т;, , постоянно считываемым по i-му адресу блока 12 памяти, до момента совпадения кодов

на входах первого элемента 6 сравнения.

По заднему фронту входного импульса на выходе формирователя 10 импульсов снова формируется короткий импульс, работа блоков устройства происходит аналогично описанному, при этом по i + 1-му адресу блока 12 памяти заносится код относительного времени окончания первого входного импульса Т + Ту,, где Tj - состояние первого счетчика; в момент окончания длительности входного импульса, а второй счетчик 7 в очередной раз увеличивает свое состояние на единицу.

При поступлении последующих импульсов на вход устройства работа упомянутых блоков циклически повторяется.

При достижении первым счетчиком 2 состояния, равного коду, записанному по i-му адресу блока 12 памяти (Т + %д соответствует отработке устройством заданного времени задержки Т,, на выходе первого элемента 6 сравнения формируется импульс, увеличивающий состояние третьего счетчика 13 на единицу. При этом единичное состояние младшего разряда третьего счетчика 13 передается на выход устройства и. 5 таким образом, начинается формирование выходного задержанного импульса. Далее происходит сравнение кода Tj + Tj. , записанного по i + 1-МУ адресу блока 12 памйти, с текущим сострянием первого счетчика 2. При достижении состоянием первого счетчика 2 значения Т + Т, на выходе первого элемента 6 сравне ния формируется импульс, увеличиваю 1ЦИЙ состояние третьего счетчика 13 на единицу. При этом заканчивает ся формирование выходного импульса равного по длительности первому входному импульсу и задержанного относительного него на заданное вре мя задержки Tj,, . Далее процесс формирования задержанных импульсов хщклически повторяется посредством аналогичного описанному сравнения кодов, занесен ных в блок 12 памяти, с текущим состоянием первого счетчика 2. При уменьшении частоты следования входных импульсов или прекращении поступления импульсов на вход устройства продолжается считьшание из блока 12 памяти кодов, характери зующих моменты смены состояний на входе устройства и формирование задержанных импульсов аналогично описанному, до тех пор, пока состояния второго 7 и третьего 13 счетчиков н станут равными, что свидетельствует об окончании формирования последнего из поступивших до этого момента на вход устройства импульса, задержанного на заданное время задержки. В результате на выходе второго элемента 8 сравнения прекращается фор шpoвaниe сигнала, разрешающего работу первого элемента:6 сравнения до.поступления следующего импульса на вход устройства с целью предотвр щения повторногоформирования длительности уже сформированньк импуль сов при последующих циклах счета первого счетчика 2. При поступлении последующих сери импульсов на вхол устройства функци нирование последнего происходит аналогично описанному. Во втором случае на вход устройства поступает стационарная последовательность импульсов. При этом время задержки Т может быть как больше нескольких -периодов следования входных импульсов ТСА, так и 35 меньше длительности одного входного импульса Ти. Если Tj. Т„, то по переднему фронту каждого очередного импульса происходит запись в блок памяти кодов fj + Tj,, где Ту - код, характеризующий момент поступления очередного импульса входной последовательности и разрешение работы первого элемента 6 сравнения в результате увеличения на единицу состояния второго счетчика 7. По окончании отра- ботки первым сетчиком 2 времени задержки код его ;Состояния становится равным Т j + TI,, в результате чего на выходе первого элемента 6 сравнения формируется сигнал, увеличивающий состояние третьего счетчика 13 на единицу, начиная тем самым формирование выходного задержанного импульса . В результате сравнения кодов состояний второго 7 и третьего 13 счетчиков снова запрещается работа первого элемента 6 сравнения до окончания длительности входного импульса. По заднему входного импульса происходит запись в блок 12 памяти кода Т J + Tj, Т.- + , + + Т, разрешается работа первого элемента 6 сравнения до момента достижения состоянием первого счетчика 2 кода Tj + Т,, после чего состояния второго 7 и третьего 13 счетчиков сравниваются, работа первого элемента 6 сравнения запрещается, формирование выходного импульса заканчивается и устройство готово к приему следующего j + 1-го импульса. Длительность вькодного импульса в этом случае также равна длительности входного импульса (Т р (Т/ + - Т)-(Т + тр Т„), При поступлении на вход устройства следующих импульсов функционирование устройства происходит аналогично описанному. Минимальное время задержки разно длительности иМпульса на выходе формирователя 10 импульсов и складывается из времени суммирования сумматором 5 и времени записи в блок 12 памяти. Если Т п , коды моментов смены состояния на входе устройства, просуммированные с кодом задержки, циклически заносятся в блок 12 памяти, затем по истечении времени задержки также циклически считываются, и происходит формирование

7

задержанных импульсов с восстановлением лара 1етров входных импульсов. Функционирование узлов устройства при записи, чтении кодов из блока памяти и формировании задержанных импульсов не отличается от работы этих узлов при задержке серии импульсов. Максимальное время задержки при этом определяется объемом используемого блока памяти и равно ,о( Т(.д- К, где К - количество ячеек блока 12 памяти.

Управление длительностью задержки в процессе работы устройства в любом из режимов можно осуществлять путем записи новых кодов задержки во второй регистр 4.

Блокировка занесения кодов состояний первого счетчика 2 в регистр 3 на время суммирования сумматором 5 и записи в блок памяти результато суммирования в моменты поступления на вход устройства фронтов задерживаемых импульсов позволяет задерживать импульсы, не синхронизированные с тактовыми импульсами устройства.

358

Кроме того, использование регистра 3 и блокировка занесения в него кодов состояния счетчика 2 во время записи кодов, полученных на сумматоре, в блок 12 памяти обусловливают сохранение высокой точности измерения и формирования длительностей импульсов, определяемое быстродействием счетчика 2, независимо от бьют-:

родействия сумматора 5 и длительности времени записи в блок 12 памяти, J4TO позволяет, например, при использовании в качестве первого счетчика 2 микросхемы серии ЭСЛ получить погрешность измерения длительности входного импульса, не превьпоающ то 10 не, без увеличения потребляемой мощности, так как остальные блоки могут строиться на микросхемах серии ТТЛ.

Р необходимости построения энергег. тически экономичных устройств для реализации блоков устройства можно использовать микросхемы КМОП серии, отличающиеся малой потребляемой

мощностью при сохранении достаточно высокой точности за счет применения в качестве первого счетчика 2 микросхемы серии ТТЛ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство задержки импульсов | 1981 |

|

SU1019611A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для регистрации информации | 1985 |

|

SU1355984A1 |

УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ, содержащее генератор тактовых имцульсов, выход которого соединен со счетным входом первого счетчика первый и второй регистры, сумматор, первый элемент сравнения, первый информационный вход которого соединен с информационным выходом первого .Счетчика, второй счетчик, второй элемент сравнения, элемент И, о т - личающееся тем, что, с целью расширения функциональных возможностей за счет сохранения длительностей входных импульсов и пауз и за счет обеспечения работы в условиях отсутствия синхронизации входных импульсов тактовЬ1ми импульсами , устройства, а также сокращения объема оборудования, в него введены формирователь импульсов, триггер, блок памяти и третий счетчик, причем выход генератора тактовых импульсов соединен с входом синхронизации триггера и первым входом элемента И, информационный вход первого регистра соединен с выходом первого счетчика, вход синхронизации - с выходом элемента И, а выход - с первым входом сумматора, вход устройства соединен с входом формирователя импульсов, выход которого соединен с D-входом триггера, второй вход элемента И соединен с инверсным выходом триггера, входом разрешения записи блока памяти и счетным входом второго, счетчика, выход второго регистра соединен с (Л вторым входом сумматора, вход адреса записи блока памяти соединен с: с информационным выходом второго счетчика и первый входом второго элемента сравнения, вход адреса чтения - с информационным выходом третьего счетчика и вторым входом ;о ел второго элемента сравнения, информационный вход - с выходом сумматора 4ib выход - с вторым входом первого 00 элемента сравнения, вход разрешения сравнения которого соединен с выхоел дом второго элемента сравнения, а выход - со счетным входом третьего счетчика, выход младшего разряда которого является выходом устройства.

| Авторское свидетельство СССР № 756619, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство задержки импульсов | 1975 |

|

SU524312A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-30—Публикация

1984-03-06—Подача