(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| Конвейерное вычислительное устройство | 1985 |

|

SU1322261A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| Устройство для суммирования М чисел | 1984 |

|

SU1200281A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Устройство для суммирования @ @ -разрядных двоичных чисел | 1984 |

|

SU1277095A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации. Целью изобретения является повышение быстродействия. Цель достигается введением в состав устройства, содержащего первый и второй преобразователи кода числа в двоичный код количества единиц и пять элементов задержки, дополнительно четырех одноразрядных сумматоров и новых связей. Устройство осуществляет параллельный по словам и последовательный по разрядам способ сложения, при этом обрабатывая по два разрядных среза сразу. Устройство допускает одновременное сложение до семи чисел (M≤7). 1 ил.

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации.

Целью изобретения является повышение быстродействия.

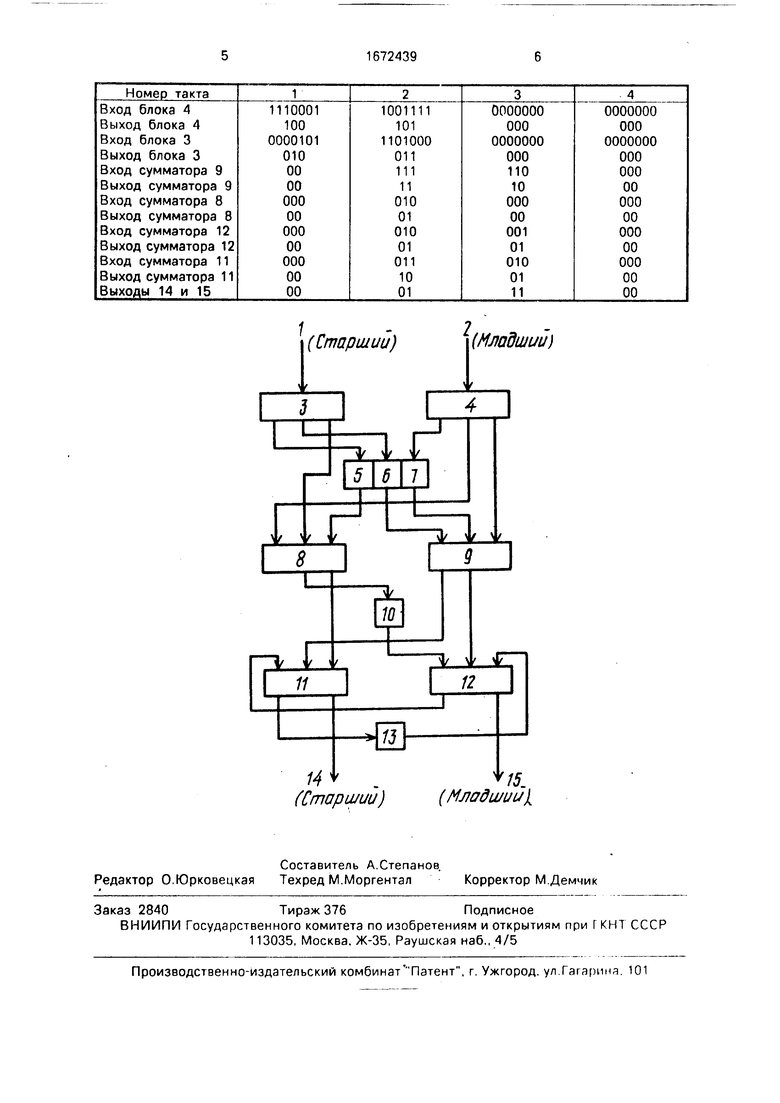

На чертеже приведена структурная схема устройства для суммирования М чисел, где М 7.

Устройство содержит входы 1 старшего разряда среза, входы 2 младшего разрядного среза, преобразователи 3 и 4 кода числа в двоичный код количества единиц, элементы 5-7 задержки, одноразрядные сумматоры 8 и 9, элемент 10 задержки, одноразрядные сумматоры 11 и 12, элемент 13 задержки, выход 14 старшего разряда суммы и выход 15 младшего разряда суммы.

Устройство позволяет одновременно суммировать до семи чисел, обрабатывая сразу по два разрядных среза.

Устройство работает следующим образом.

Все элементы задержки в начальный момент сброшены. На вход 2 подаются сначала первый (младший) разрядный срез входных чисел, на вход 1 подается второй разрядный срез входных чисел. На выходах преобразователей 3 и 4 будет сумма единиц соответствующего разрядного среза в двоичном коде. Младшие разряды суммы разрядных срезов поступают на входы сумматоров 8 и 9. Второй выход блока 4 является переносом в (1+1)-й разряд и подается на вход сумматора 8. Старший выход блока 4 является выходом переноса в (+2)-й разряд и подается на вход элемента 7 задеро VI го

CJ

о

жки, чтобы в следующем такте поступить на вход сумматора 9, Второй выход суммы (1+1)- го разрядного среза является переносом в (42)-й разряд, и поэтому через элемент 6 задержки в следующем такте поступает на вход сумматора 9, старший выход блока 3 является переносом в (+3)-й разряд и в следующем такте поступает на вход сумматора 8. Аналогично соединены и выходы сумматоров 8, 9,11 и 12. Таким образом, на выходе 15 формируется младший разряд суммы, а на выходе 14 - старший. В следующем такте на входы 2 подается третий разрядный срез входных чисел, а на вход 1 - четвертый. На выходе 15 формируется значение третьего бита суммы, а на выходе 14 - четвертого. И так далее, пока не сформируются все разряды суммы входных чисел.

Пример. Пусть необходимо сложить семь четырехразрядных входных чисел 1101, 1001,0001, 1100,0110,0100,0111.

Информация на входах и выходах бло- коб после каждого такта приведена в таблице.

Таким образом, на выходах 14 и 15 сформировалась сумма семи входных чисел 00110100 1101 + 1001 +0001 + 1100+ + 0110 + 0100 + 0111.

Таким образом, за счет параллельной обработки двух смежных разрядных срезов обеспечивается повышение быстродействия по сравнению : известными устройствами, реализующими параллельный по словам последовательный по разрядам способ сложения.

Формула изобретения Устройство для суммирования М чисел, где М 7, содержащее первый и второй преобразователи кода числа в двоичный код количества единиц и пять элементов задержки, причем входы первого преобразователя кода числа в двоичный код количества единиц соединены с входами младшего разрядного среза входных операндов устройства, выход старшего разряда первого

преобразователя кода числа в двоичный код количества единиц соединен с входом первого элемента задержки отличающее- с я тем, что, с целью повышения быстродействия, устройство дополнительно содержит четыре одноразрядных сумматора, причем входы второго преобразователя кода числа в двоичный код количества единиц соединены с входами старшего разрядного среза

входных операндов устройства, а выходы разрядов с первого по третий соединены соответственно с первым входом первого одноразрядного сумматора, с входом второго элемента задержки и входом третьего

элемента задержки, выходы первого и второго разрядов первого преобразователя кода числа в двоичный код количества единиц соединены соответственно с первым входом второго и вторым входом первого одноразрядных сумматоров, второй и третий входы второго одноразрядного сумматора соединены соответственно с выходами второго и третьего элементов задержки, выход третьего элемента задержки соединен с

третьим входом первого одноразрядного сумматора, выход суммы которого соединен с первым входом третьего одноразрядного сумматора, а выход переноса соединен с входом-четвертого элемента задержки, выход которого подключен к первому входу четвертого одноразрядного сумматора, второй вход которого соединен с выходом суммы второго одноразрядного сумматора, выход переноса второго одноразрядного

сумматора соединен с вторым входом третьего одноразрядного сумматора, третий вход которого соединен с выходом переноса четвертого одноразрядного сумматора, выход переноса третьего одноразрядного сумматора через пятый элемент задержки соединен с третьим входом четвертого одноразрядного сумматора, выходы суммы третьего и четвертого одноразрядных сумматоров соединены соответственно с выходами старшего и младшего разрядов суммы устройств.

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования М чисел | 1984 |

|

SU1200281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-04-11—Подача