Изобретение относится к автоматике и вычислительной технике и может быть использовано для проверки и наладки сложных цифровых устройств и систем,

Цель изобретения - расширение области применения путем обеспечения возможности контроля динам:ических характеристик цифровых систем

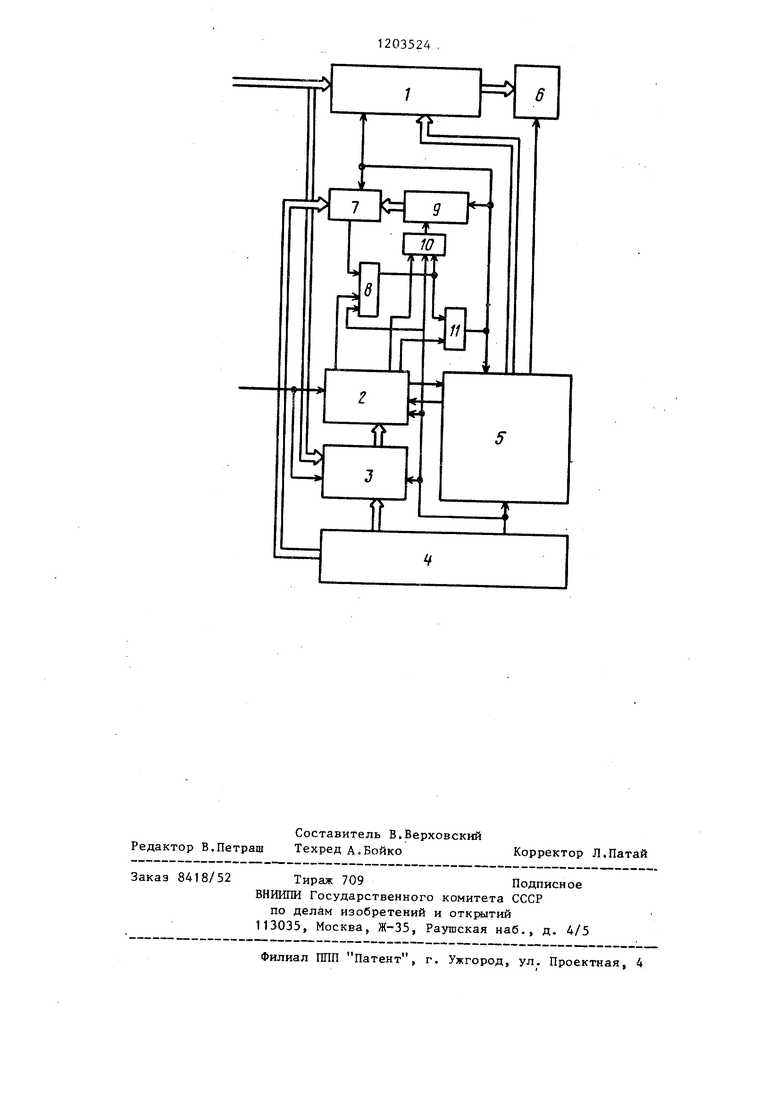

На чертеже изображена блок-схема устройства.

Устройство содержит блок 1 памяти, блок 2 формирования тактов, блок 3 формирования сигнала запуска, клавиатуру 4, блок 5 управления, блок индикации, сравнения, триггер 8, счетчик 9, элемент ИЛИ 10, элмент И 1 1 .

Устройство работает следующим образом,

Перед запуском необходимо подключить входы группы устройства к исследуемым точкам объекта контроля, подключить вход устройства, к тактовому выходу объекта контроля, уста- новить с помощью клавиатуры 4 код запускающего слова, величину зоны анализа, число пропусков момента анализа, а также инициализировать сигнал сброса.

По сигналу сброса блок 3 форми- рования сигнала запуска устанавливается в состояние О, блок 2 формирования тактов - в. состояние О, счетчик 9 через элемент ИЛИ 10 - в состояние О, триггер 8 - в состояние 1.

В результате прохождения сигн.ала сброса потенциал через элемент ИЛИ 10 удерживает счетчик 9 в сброшенном состоянии, запрещая счет Разрешающий потенциал с выхода триггера 8 не препятствует прохождению импульсов записи через элемент И 11 на вход блока 1 памяти. Сигнал с вт рого выхода на третий вход блока 2 формирования тактов разрешает прохождение тактовых сигн-алов, сигнал с третьего выхода блока 2 запрещает прохождение импульсов с выхода элемента И 11.

Входная информация последовательно фиксируется в блоке памяти, при заполнении которого происходит переполнение, и запись прсЙ1сходит снова с первых адресов блока 1 памяти.

о

s

0

5 g

5

5

7/ 2

А. Ч

Параллельно с указанным процеС сом происходит сравнение текущей информации на предмет выявления кода, аналогичного заданному пользователем. При появлении такого кода на выходе блока 3 под тактовые импульсы появляется ю- пульс и при равенстве комбинации с комбинацией, набранной пользователем, формируется под тактовый импульс сигнал, поступающий на вход-блока 2 и устанавливающий последний в состояние 1. Данный сигнал разрешает прохождение импульсов на установочньй вход триггера, снимает потенциал сброса с входа элемента ИЛИ 10, чем разрешается счет счетчика и прохождение импульсов записи с выхода элемента И 11 .

Входная информация, записываемая в блоке 1 памяти под тактовые импульсы через элемент И 11, с момента. равенства кодов начинает просчитываться в блоке 5 управления.

В момент равенства числа импульсов,, просчитанных счетчиком 9, числу, заданному пользователем, на выходе блока 7 сравнения под такт синхронизации (импульс записи) появляется сигнал, устанавливающий триггер в состоянии О, чем прерывается прохождение импульсов в блок 1 памяти через элемент И 11 (запись первой пачки) и сбрасывается счетчик через элемент ИЛИ 10. Как следствие, прекращается счет и формирование адресов записи. Такое состоя- нке сохраняется до тех пор, пока во входной информации снова не появится слово (код), равное набранному пользователем. При равенстве слов цикл повторяется.

Последующая упаковка информационных пачек в блоке 1 памяти производится описанным выше способом до тех пор, пока число И1 1пульсов записи не будет равно половине объема блока.

Информация отражается на блоке индикации для анализа, причем, как указано выше, в памяти имеется информация До момента анализа (первая половина) и информация, упакованная в пачки После момента анализа (вторая половина).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для отладки и контроля программ | 1988 |

|

SU1509907A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для контроля информации | 1990 |

|

SU1755284A1 |

| Устройство для кусочно-линейной аппроксимации | 1990 |

|

SU1837272A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550517A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Редактор В.Петраш

Составитель В.Верховский Техред А.Бойко

Заказ 8418/52

Тираж 709Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Корректор Л.Патай

| Стасюкинас Ю.В | |||

| и др | |||

| Логический анализатор - сменный блок к универсальному осциллографу | |||

| - В сб.: Техника средств связи, сер | |||

| РИТ, вып | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шлимович Е.М | |||

| Логические анализаторы для проверки и наладки сложных цифровых устройств и систем | |||

| - Вопросы электроники, сер | |||

| ЭВТ, вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-27—Подача