Изобретение относится к области автоматике и вычислительной техники и может быть использовано в системах управления технологическими процессами.

Цель изобретения - повышение достоверности контроля.

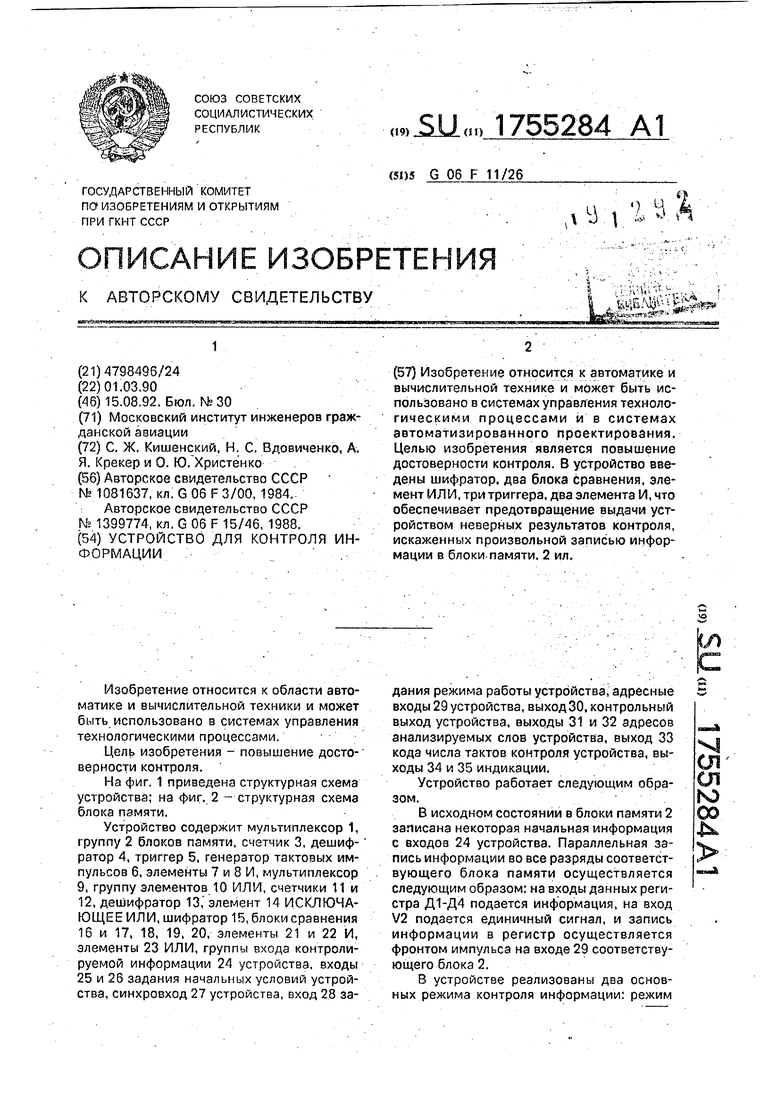

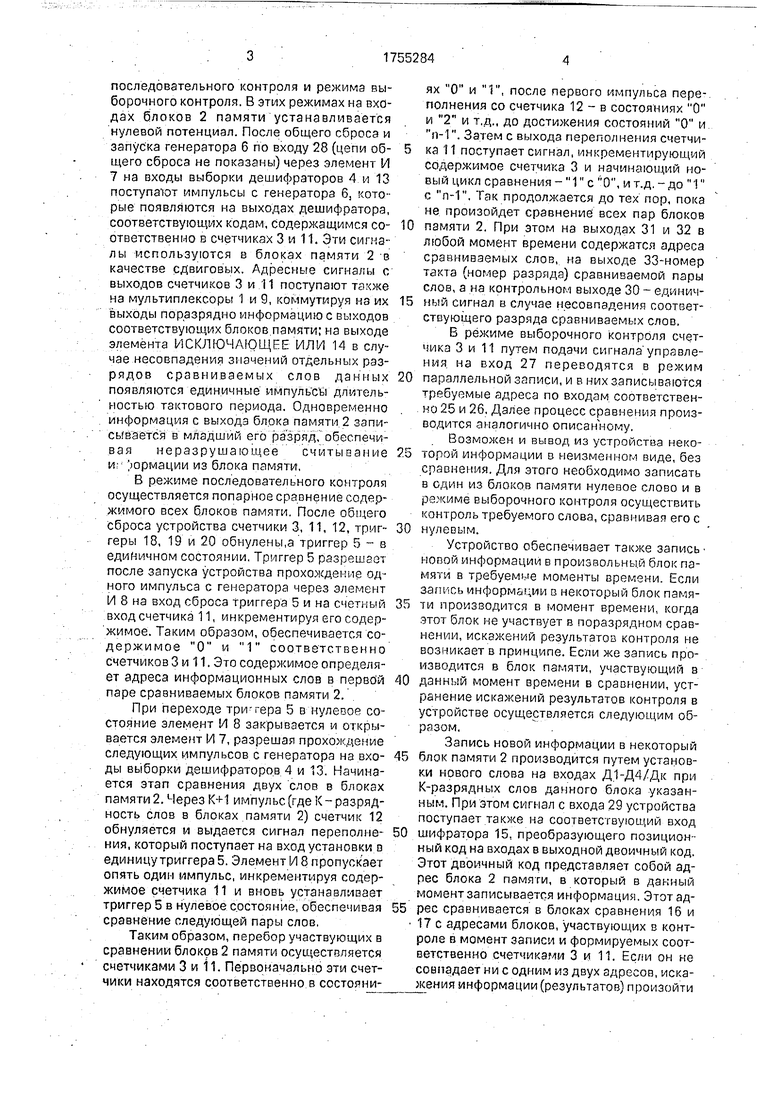

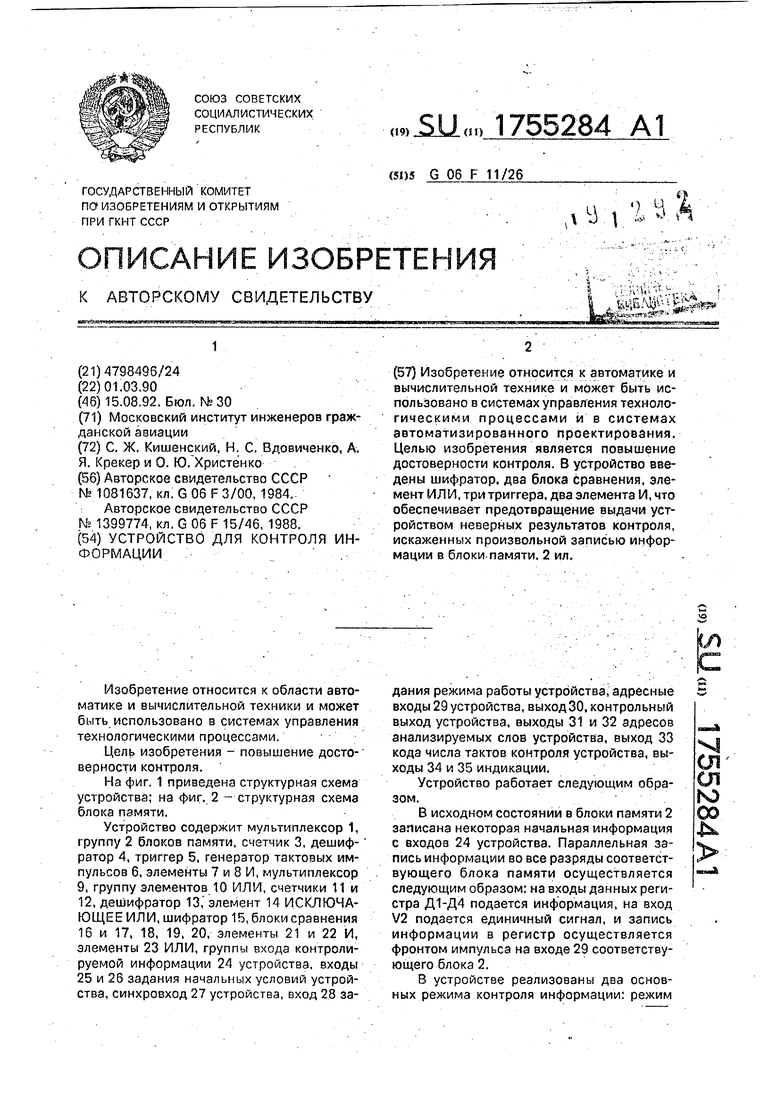

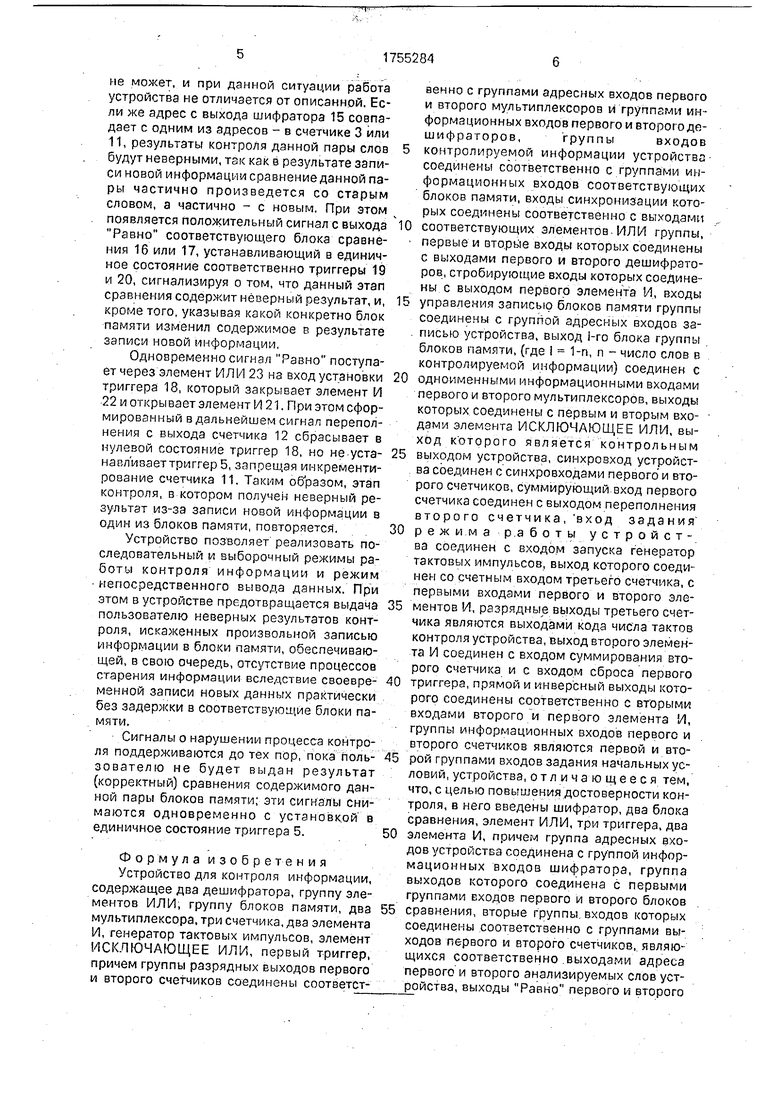

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока памяти.

Устройство содержит мультиплексор 1, группу 2 блоков памяти, счетчик 3, дешифратор 4, триггер 5, генератор тактовых импульсов 6, элементы 7 и 8 И, мультиплексор 9, группу элементов 10 ИЛИ, счетчики 11 и 12, дешифратор 13, элемент 14 ИСКЛЮЧАЮЩЕЕ ИЛИ, шифратор 15, блоки сравнения 16 и 17, 18, 19, 20, элементы 21 и 22 И, элементы 23 ИЛИ, группы входа контролируемой информации 24 устройства, входы 25 и 26 задания начальных условий устройства, синхровход 27 устройства, вход 28 задания режима работы устройства, адресные входы 29 устройства, выход30, контрольный выход устройства, выходы 31 и 32 адресов анализируемых слов устройства, выход 33 кода числа тактов контроля устройства, выходы 34 и 35 индикации.

Устройство работает следующим образом.

В исходном состоянии в блоки памяти 2 записана некоторая начальная информация с входов 24 устройства. Параллельная запись информации во все разряды соответствующего блока памяти осуществляется следующим образом: на входы данных регистра Д1-Д4 подается информация, на вход V2 подается единичный сигнал, и запись информации в регистр осуществляется фронтом импульса на входе 29 соответствующего блока 2.

В устройстве реализованы два основных режима контроля информации: режим

01 СЛ

Ю

последовательного контроля и режима выборочного контроля. В этих режимах на входах блоков 2 памяти устанавливается нулевой потенциал. После общего сброса и запуска генератора б по входу 28 (цепи общего сброса не показаны) через элемент И 7 на входы выборки дешифраторов 4 и 13 поступают импульсы с генератора 6j которые появляются на выходах дешифратора, соответствующих кодам, содержащимся соответственно в счетчиках 3 и 11. Эти сигналы используются в блоках памяти 2 в качестве сдвиговых. Адресные сигналы с выходов счетчиков 3 и 11 поступают тачже на мультиплексоры 1 и 9, коммутируя из их выходы поразрядно информацию с выходов соответствующих блоков памяти; на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 в случае несовпадения значений отдельных разрядов сравниваемых слов данных появляются единичные импульсы длительностью тактового периода. Одновременно информация с выхода блока памяти 2 записывается в младший его разряд, обеспечивая неразрушающее считывание и формации из блока памяти,

В режиме последовательного контроля осуществляется попарное сравнение содержимого всех блоков памяти. После общего сброса устройства счетчики 3, 11, 12, триггеры 18, 19 и 20 обнулены,а триггер 5 - в единичном состоянии. Триггер 5 разрешает после запуска устройства прохождение одного импульса с генератора через элемент И 8 на вход сброса триггера 5 и на счетный вход счетчика 11, инкрементируя его содержимое. Таким образом, обеспечивается содержимое О и 1 соответственно счетчиков 3 и 11. Это содержимое определяет адреса информационных слов в первой паре сравниваемых блоков памяти 2.

При переходе тритера 5 в нулевое состояние элемент И 8 закрывается и открывается элемент И 7, разрешал прохождение следующих импульсов с генератора на входы выборки дешифраторов 4 и 13. Начинается этап сравнения двух слов в блоках памяти 2. Через К+1 импульс (где К - разрядность слов в блоках памяти 2) счетчик 12 обнуляется и выдается сигнал переполнения, который поступает на вход установки в единицу триггера 5. Элемент И 8 пропускает опять один импульс, инкрементируя содержимое счетчика 11 и вновь устанавливает триггер 5 в нулевое состояние, обеспечивая сравнение следующей пары слов,

Таким образом, перебор участвующих в сравнении блоков 2 памяти осуществляется счетчиками 3 и 11. Первоначально эти счетчики находятся соответственно в состояниях О и 1, после первого импульса переполнения со счетчика 12 - в состояниях О и 2 и т.д., до достижения состояний О и n-Г. Затем с выхода переполнения счетчика 11 поступает сигнал, инкрементирующий содержимое счетчика 3 и начинающий новый цикл сравнения- с О, и т.д.-до с п-1. Так продолжается до тех пор, пока не произойдет сравнение всех пар блоков

0 памяти 2. При этом на выходах 31 и 32 в любой момент времени содержатся адреса сравниваемых слов, на выходе 33-номер такта (номер разряда) сравниваемой пары слов, а на контрольном выходе 30 - единич5 ный сигнал в случае несовпадения соответствующего разряда сравниваемых слов,

Б режиме выборочного контроля счетчика 3 и 11 путем подачи сигнала управления на вход 27 переводятся в режим

0 параллельной записи, и в них записываются требуемые адреса по входам соответственно 25 и 26, Далее процесс сравнения производится аналогично описанному,

Возможен и вывод из устройства неко5 торой информации в неизменном виде, без сравнения. Для этого необходимо записать в един из блоков памяти нулевое слово и в режиме выборочного контроля осуществить контроль требуемого слова, сравнивая его с

0 нулевым.

Устройство обеспечивает также запись новой информации в произвольный блок памяти в требуемые моменты времени. Если запись информации в некоторый блок памя5 ти производится в момент времени, когда этот блок не участвует в поразрядном сравнении, искажений результатов контроля не возникает в принципе. Если же запись производится в блок памяти, участвующий в

0 данный момент времени в сравнении, устранение искажений результатов контроля в устройстве осуществляется следующим образом.

Запись новой информации в некоторый

5 блок памяти 2 производится путем установки нового слова на входах Д1-Д4/Дк при К-разрядных слов дачного блока указанным. При этом сигнал с входа 29 устройства поступает также на соответствующий вход

0 шифратора 15. преобразующего позиционный код на входах в выходной двоичный код. Этот двоичный код представляет собой адрес блока 2 памяти, в который в данный момент записывается информация. Этотад5 рее сравнивается в блоках сравнения 16 и 17 с адресами блоков, участвующих в контроле в момент записи и формируемых соответственно счетчиками 3 и 11. Если он не совпадает ни с одним из двух адресов, искажения информации (результатов) произойти

не может, и при данной ситуации работа устройства не отличается от описанной. Если же адрес с выхода шифратора 15 совпадает с одним из адресов - в счетчике 3 или 11, результаты контроля данной пары слов будут неверными, так как в результате записи новой информации сравнение данной пары частично произведется со старым словом, а частично - с новым. При этом появляется положительный сигнал с выхода Равно соответствующего блока сравнения 16 или 17, устанавливающий в единичное состояние соответственно триггеры 19 и 20, сигнализируя о том, что данный этап сравнения содержит неверный результат, и, кроме того, указывая какой конкретно блок памяти изменил содержимое в результате записи новой информации.

Одновременно сигнал Равно поступает через элемент ИЛ И 23 на вход установки триггера 18, который закрывает элемент И 22 и открывает элемент / 21. При этом сформированный в дальнейшем сигнап переполнения с выхода счетчика 12 сбрасывает в нулевой состояние триггер 18, но не уста- навл ивэеттриггер 5, запрещая имкременти- рование счетчика 11. Таким образом, этап контроля, в котором получен неверный результат из-за записи новой информации а один из блоков памяти, повторяется.

Устройство позволяет реализовать последовательный и выборочный режимы работы контроля информации и режим непосредственного вывода данных. При этом в устройстве предотвращается выдача пользователю неверных результатов контроля, искаженных произвольной записью информации в блоки памяти, обеспечивающей, в свою очередь, отсутствие процессов старения информации вследствие своевре- менной записи новых данных практически без задержки в соответствующие блоки памяти.

Сигналы о нарушении процесса контроля поддерживаются до тех пор, пока поль- зователю не будет выдан результат (корректный) сравнения содержимого данной пары блоков памяти; эти сигналы снимаются одновременно с установкой в единичное состояние триггера 5.

Формула изобретения Устройство для контроля информации, содержащее два дешифратора, группу элементов ИЛИ, группу блоков памяти, два мультиплексора, три счетчика, два элемента И, генератор тактовых импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый триггер, причем группы разрядных выходов первого и второго счетчиков соединены соответственно с группами адресных входов первого и второго мультиплексоров и группами информационных входов первого и второго дешифраторов,группывходов контролируемой информации устройства соединены соответственно с группами информационных входов соответствующих блоков памяти, входы синхронизации которых соединены соответственно с выходами соответствующих элементов ИЛИ группы, первые и вторые входы которых соединены с выходами первого и второго дешифраторов, стробирующие входы которых соедине ны с выходом первого элемента И, входы управления записью блоков памяти группы соединены с группой адресных входов записью устройства, выход 1-го блока группы блоков памяти, (где i 1-n, п - число слов в контролируемой информации) соединен с одноименными информационными входами первого и второго мультиплексоров, выходы которых соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является контрольным выходом устройства, синхровход устройства соединен с синхровходами первого и второго счетчиков, суммирующий вход первого счетчика соединен с выходом переполнения второго счетчика, вход задания режима работы устройства соединен с входом запуска генератор тактовых импульсов, выход которого соединен со счетным входом третьего счетчика, с первыми входами первого и второго элементов И, разрядные выходы третьего счетчика являются выходами кода числа тактов контроля устройства, выход второго элемента И соединен с входом суммирования второго счетчика и с входом сброса первого триггера, прямой и инверсный выходы которого соединены соответственно с вторыми входами второго и первого элемента И, группы информационных входов первого и второго счетчиков являются первой и второй группами входов задания начальных условий, устройства, отличающееся тем, что, с целью повышения достоверности контроля, в него введены шифратор, два блока сравнения, элемент ИЛИ, три триггера, два элемента И, причем группа адресных входов устройства соединена с группой информационных входов шифратора, группа выходов которого соединена с первыми группами входов первого и второго блоков сравнения, вторые группы входов которых соединены соответственно с группами выходов первого и второго счетчиков, являющихся соответственно выходами адреса первого и второго анализируемых слов устройства, выходы Равно первого и второго

блоков сравнения соединены соответственно с первым и вторым входами элемента ИЛИ и с входами установки второго и третьего триггеров, прямые выходы которых являются выходами индикации о корректности проверки данных устройства, выход элемента ИЛИ соединен с входом установки четвертого триггера, прямой и инверсный выходы которого соединены соот24

ветстаенно с первыми входами третьего и четвертого элементов И, выход третьего элемента И соединен с входом сброса четвертого триггера, выход четвертого элемента И соединен с входами сброса второго и третьего триггеров и входом установки первого триггера, выход переполнения третьего счетчика соединен с вторыми входами третьего и четвертого элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления техноло- гическими процессами и в системах автоматизированного проектирования. Целью изобретения является повышение достоверности контроля. В устройство введены шифратор, два блока сравнения, элемент ИЛИ, три триггера, два элемента И, что обеспечивает предотвращение выдачи устройством неверных результатов контроля, искаженных произвольной записью информации в блоки памяти. 2 ил.

М Ј-4- &о$29

Otnlvl,

ft4

| Устройство для ввода информации | 1982 |

|

SU1081637A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля информации | 1986 |

|

SU1399774A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1992-08-15—Публикация

1990-03-01—Подача