120

коммутатора адреса, выход кода логических условий постоянного запоминающего устройства микрокоманд соеД1-1Нен с информационным входом регистра логическугл условий выход метки постоянного запоминающего устройства микрокоманд соединен с вторым входом первого и sffl- версными входами второго и третьего

Изобретение относится к автома- тике и вь;числительнЬй технике и может быть использовано при построении центральных и периферийных устройств управления ЭВМ к вычислительных систем.

Цель 1 ;зобретения - повышение быстродействия.

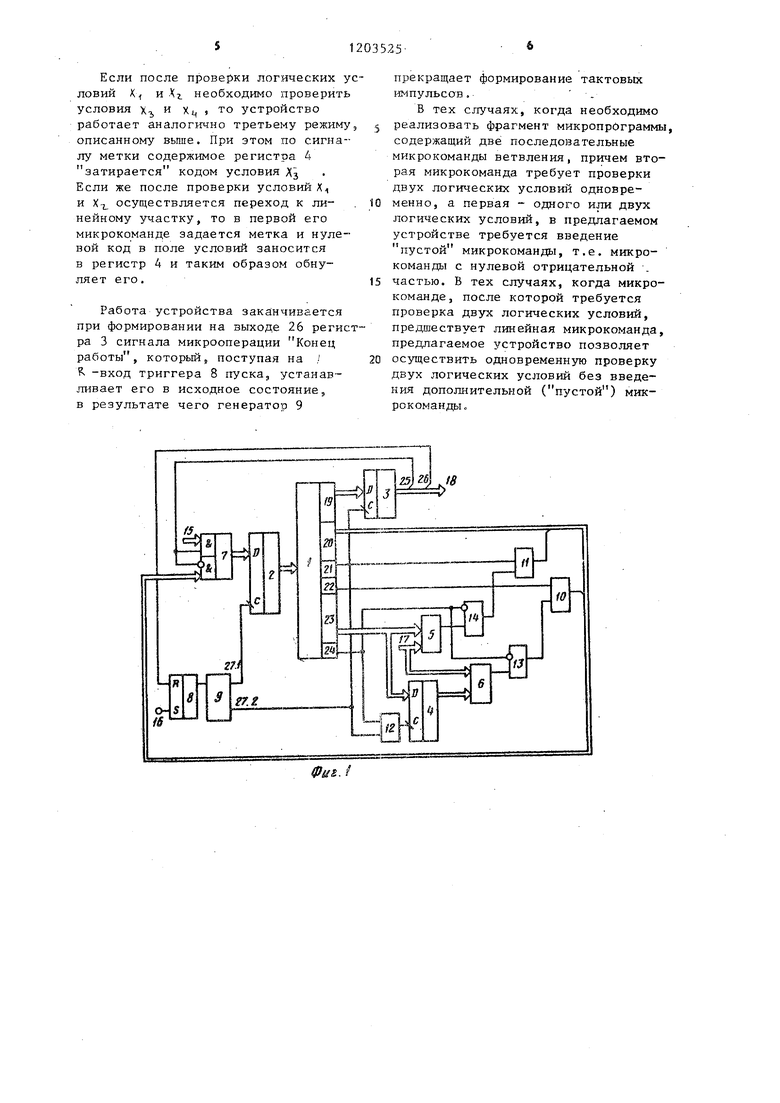

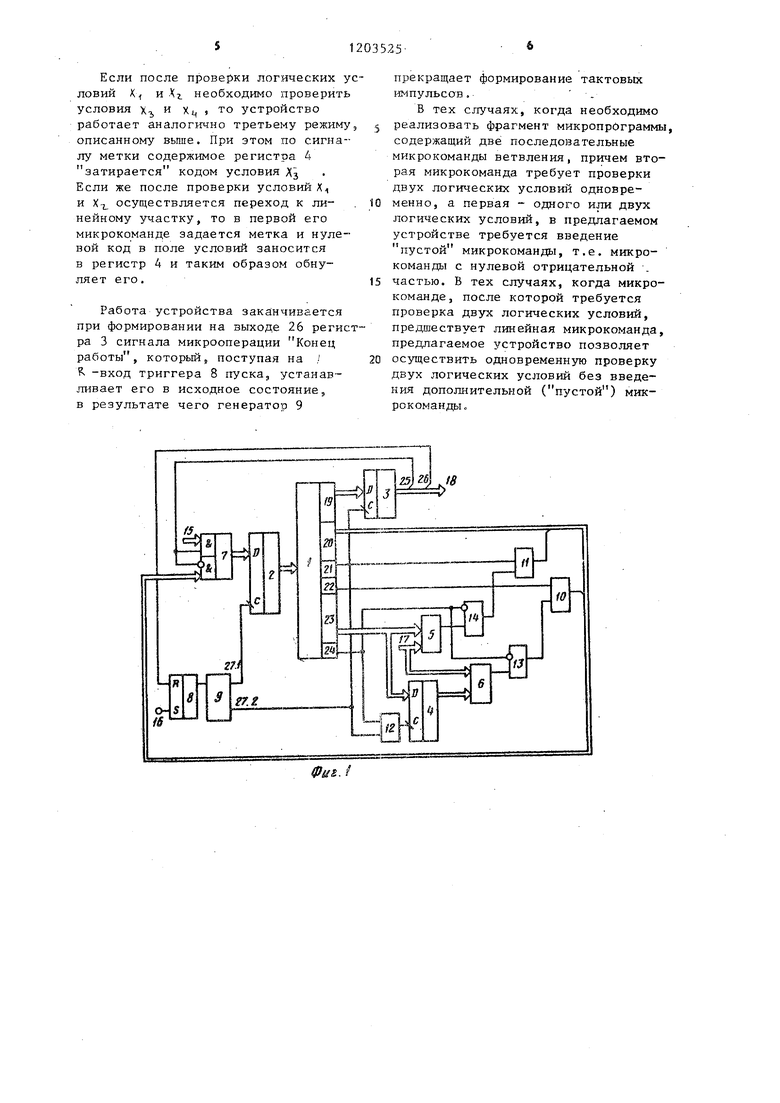

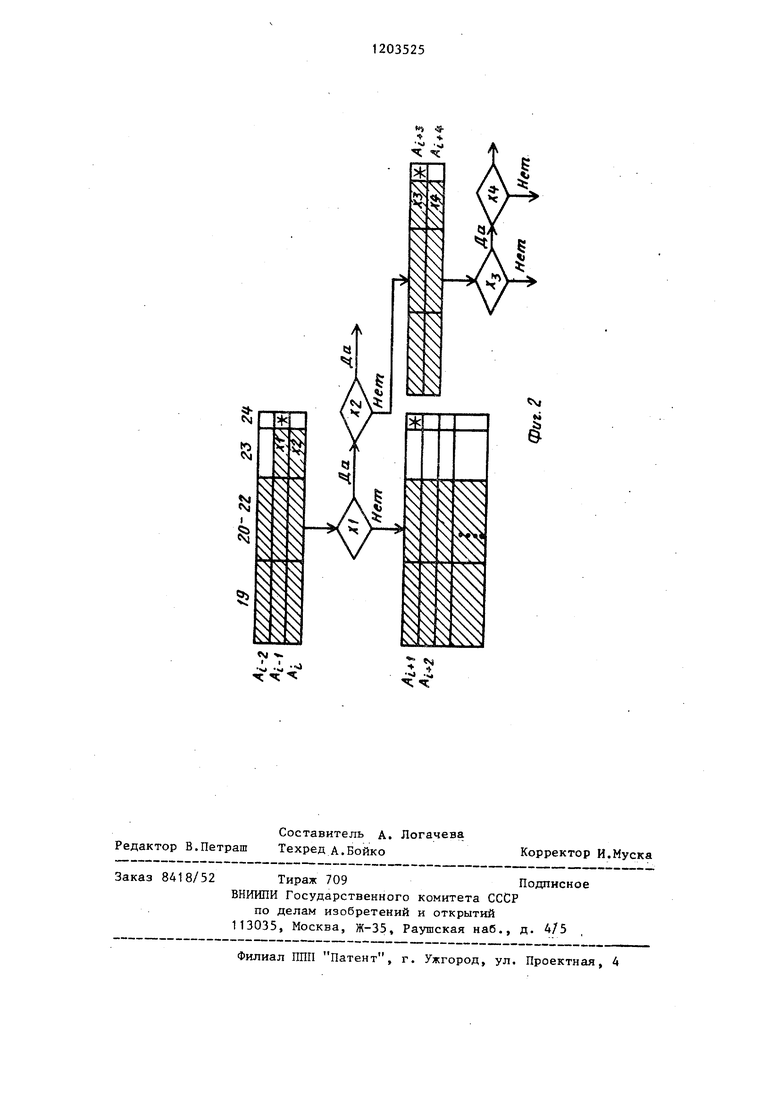

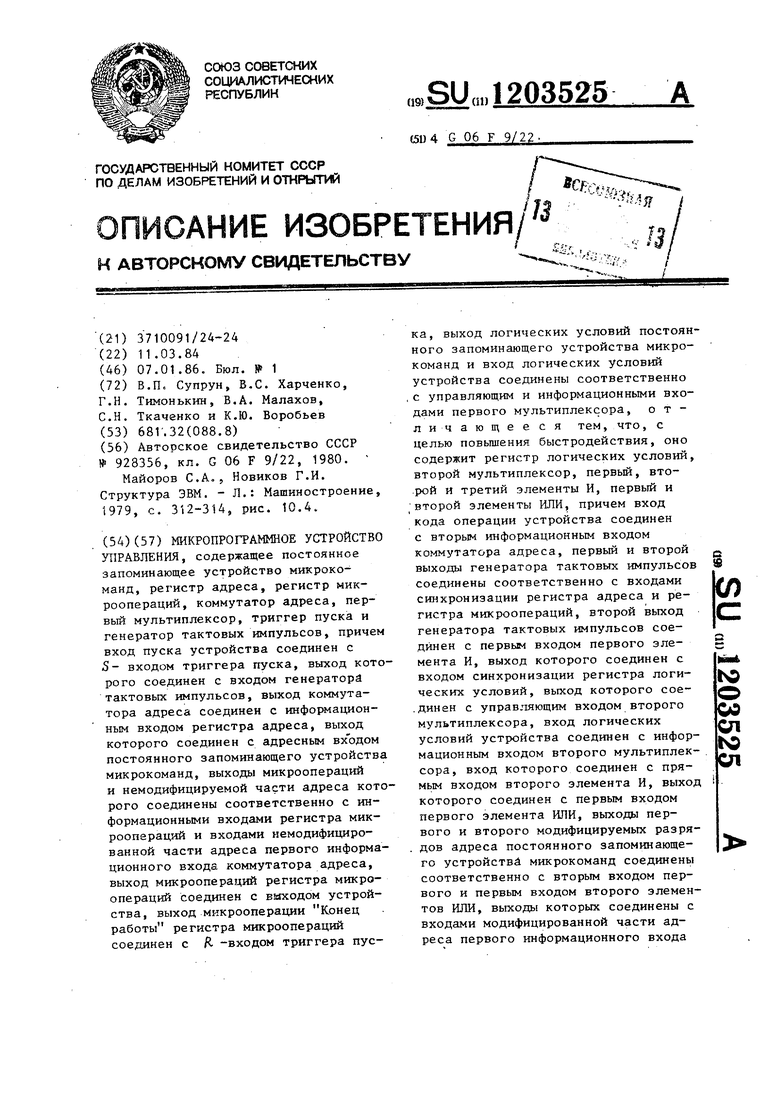

На фиг, 1 изображена функциональная схема микропрограммного устройства управления: на фиг, 2 - схемаg поясияюп ая работу устройства.

Устройство содержит постоянное Запоминающее устройство (ПЗУ) 1 микрокоманд g регистры 2-4 адреса микроопераций и логических условий соответственно, первый 5 и второй б мультиплексоры5 комг« утатор 7 адреса триггер 8 пуска, генератор 9 тактовых импульсов 5 первый 10 и второй 11 элементы ИПИ, первый 12, второй 13 и третий 14 элементы И5 входы 15 .кода; операции, 16 пуска и 17 логических условий устройства, выход 18 устройства, выходы 19-24 микроопераций, немодифицируемой части адреса, второго и первого модифицируемых разрядов адреса кода логических условий и метки постоянного запоминающего устройства микрокоманд соответственно, выходы 25 и 26 микроопераций Конец команды и Конец работы соответственно5 первый 27.1„ и 27 с 2 второй выходы генератора тактовых игшульсов соответственно.

Устройство работает след ующим Образом.

В исходном состоянии все элементы схемы находятся в нулевом состоянии, а в разряде регистра 3 микроопераций, соответствующем микроопеэлементов И, выход первого мультиплексора соединен с прямым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход микрооперации Конед команды регистра микроопераций соединен с управля- ЮБДИМ входом коммутатора адреса.

рации Конец команды (выход 25), записана (цепи приведения схемы в исходное состояние не пока- занрл) , По сигналу Пуск , поступающему через вход 16 устройства на 5™вход триггера 8, последний устанавливается в единичное состояние. При этом на выходах генератора 9 возбуждаются последовательности тактовых импульсов.

По первому тактовому импульсу L , поступающему на синхровход регистра 2 адреса, последний открывается. При этом код операции, являющийся адресом первой микрокоманды выполняемой микропрограммы, через коммутатор 7 поступает на информационный . вход регистра 2 адреса. По записан- НО1-Г, в регистре 2 адресу в ПЗУ 1 микрокоманд выбирается соответствующая микрокоманда и поступает на его выходы 19-24, При наличии - сигнала на синхровходе регистра 3 микроопераций операционная часть микрокоманды с выхода 19 поступает на информационный вход регистра 3 микроопераций. Сигналы микроопераций с регистра 3 микроопераций поступают на выход 18 устройства.

При формировании адреса очередной микрокоманды возможны следующие режимь ра.боты устройства;

формирование адреса очередной микрокоманды при выполнении линейных участков.микропрограмм без проверки логических условий,

формирование адреса очередной микрокоманды при проверке одного логического условия,

формирование адреса очередной микрокоманды при проверке двух лог1 :ческих условий одновременно.

Рассмотрим работу устройства в этих режимах.

Первый режим. При считывании микрокоманды из ПЗУ 1 микрокоманд адрес очередной микрокоманды формируется следующим образом. Немодифицируемая часть адреса очередной микрокоманды с выхода 20 поступает на соответствующие входы первого информационного входа коммутатора 7 адреса. Значение модифицируемых разрядов адреса очередной микрокоманды поступает с выходов 21 и 22 через элементы ИЛИ 11 и 10 на вход коммутатора 7. Поскольку в поле 23 и-регистре 4 при этом записан нулевой код, то на.выходе мультиплексоров 5 и 6 и элементов И 13 и 14 присутствуют нулевые сигналы. Ввиду отсутствия сигнала микрооперации Конец команды адрес очередной микроко- мандь через коммутатор 7 поступает на информационный вход регистра 2 адреса. При формировании на выходе 27.1 генератора 9 очередного тактового импульса адрес микрокоманды записывается в регистр 2 адреса, Далее устройство работает в этом режиме аналогично описанному выше. Второй режим. Если при выполнении текущей микрокоманды необходимо проверить значение логического условия и произвести ветвление микропрограммы, то на выходе 23 ПЗУ 1 микрокоманд будет считан код этого логического условия. Значения логических условий с входа 17 поступают на первый мультиплексор 5 Формирование значения модифицируемого разряда адреса очередной микрокоманды осуществляется на втором элементе ИЛИ 11 путем реали, зации логической функции

где 0 - значение модифицируемого разряда адреса очередной микрокоманды на выходе 21 ПЗУ 1 микрокоманд (в микрокоманде ветвления й(. 0);

Х - значение проверяемого логического условия, формируемого на выходе мультиплексора 5.

Значение сигнала г. поступает на вход модифицированных разрядов адреса первого информационного входа коммутатора 7 адреса, Посколь

203525

ку в регистре 4 при этом сохраняется нулевой код, то сигнал на выходе мультиплексора 6 равен нулю и модификации второго адресного разряда не

5 происходит.

Третий режим. Если при выполнении микрокоманд необходимо реализовать проверку двух логических условий, то предлагаемое устройство ра10 ботает следующим образом. При считывании микрокоманды i., на выходе 24 ПЗУ 1 микрокоманд присутствует единичный сигнал - метка. По второму тактовому импульсу i проис15 ходит запись операционной части микрокоманды А-,. в регистр 3 и запись кода логического условия в регистр 4 логических условий. Метка запрещает прохождение сигналов

20 через второй 13 и третий 14 элементы И, блокируя тем самым модификацию младших адресных разрядов. Формирование адреса микрокоманды Л; , содержащей код второго проверяемого

25 логического условия XT. , т.е, собственно микрокомандь ветвления происходит по очередному импульсу I, после его окончания метка пропадает, второй 13 и третий 14 элементы И открываются. По Lг . происходит считывание операционной части микрокоманды А,

Код логического условия Xi поступает на мультиплексор 5, а код логического условия Х - на муль типлексор б, С входа 17 значения логических условий подаются на информационные входы мультиплексоров 5 и 6. Значения проверяемых условий iC и Xj с выходов мультиплексоров 5 и 6 через открытые элементы И 14 и 13 поступают на элемейты ИЛИ 1t и 10. Модифицированные разряды адреса очередной микрокоманды А| поступают на входы модифицированной части разрядов адреса первого информационного входа коммутатора 7 адреса.,

Механизм модификации в этом режиме полностйо аналогичен описан5 ному во втором режиме. Отличие состоит лишь в том, что при этом на элементах ИЛИ 10 и 11 модифици- Р1ТОТСЯ (изменяются с нуля на единицу при единичном значении условий

55 Xi и XT, ABS младших разряда одновременно, что позволяет осуществлять ветвление по трем - четырем направлениям.

30

40

Если после проверки логических уловий Х и Кг. необходимо проверить условия х и Xt, то устройство работает аналогично третьему режиму описанному выше. При этом по сигналу метки содержимое регистра 4 затирается кодом условия Xj Если же после проверки условий Х и X-j осуществляется переход к линейному участку, то в первой его микрокоманде задается метка и нулевой код в поле условий заносится в регистр 4 и таким образом обнуляет его.

Работа устройства зака;нчивается при формировании на выходе 26 регисра 3 сигнала микрооперации Конец работы, который, поступая на / -вход триггера 8 пуска, устанавливает его в исходное состояние, в результате чего генератор 9

прекращает формирование тактовых импульсов. .

В тех случаях, когда необходимо

реализовать фрагмент микропрограммы, содержащий две последовательные микрокоманды ветвления, причем вторая микрокоманда требует проверки двух логических условий одновременно, а первая - одного или двух логических условий, в предлагаемом устройстве требуется введение пустой микрокоманды, т.е. микрокоманды с нулевой отрицательной .

частью. В тех случаях, когда микрокоманде, после которой требуется проверка двух логических условий, предшествует линейная микрокоманда, предлагаемое устройство позволяет

осуществить одновременную проверку двух логических условий без введения дополнительной (пустой) микрокоманды.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

f/s. i

| Микропрограммное устройство управления | 1980 |

|

SU928356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С.АО, Новиков Г.И | |||

| Структура ЭВМ | |||

| - Л.: Машиностроение, | |||

Авторы

Даты

1986-01-07—Публикация

1984-03-11—Подача