Изобретение относится к цифровой вычислительной технике и может быть использовано в аппаратуре передачи данньпс сигналами трех уровней на большие расстояния.

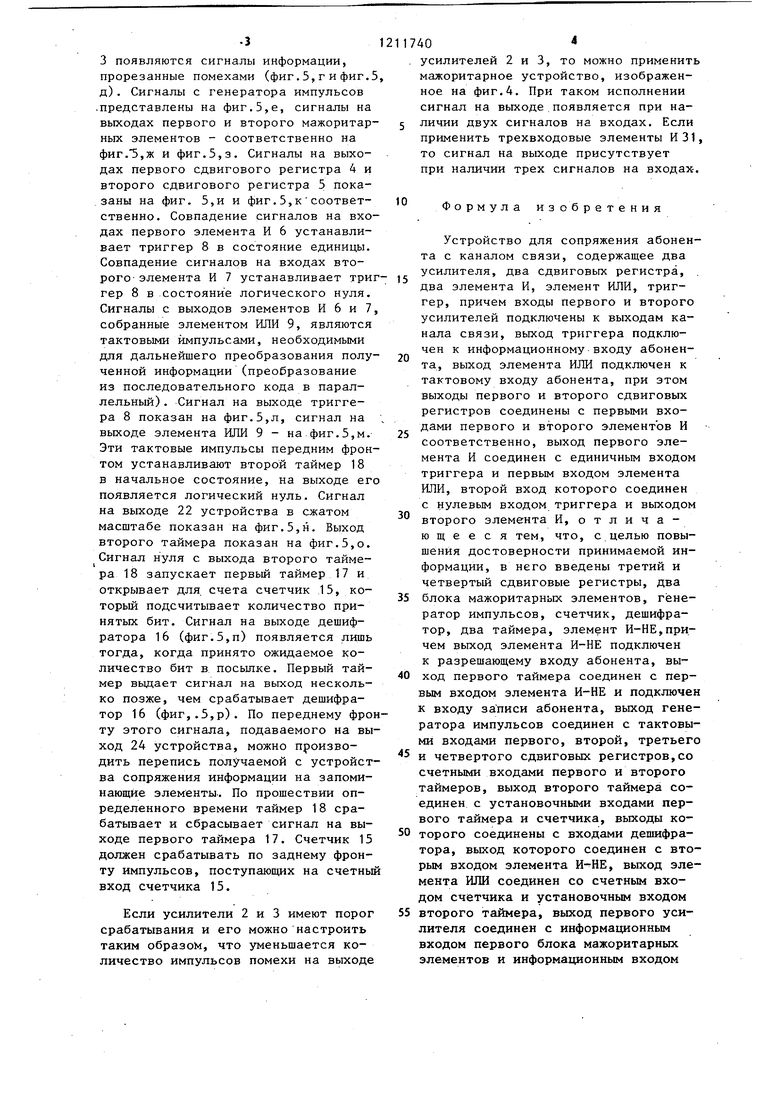

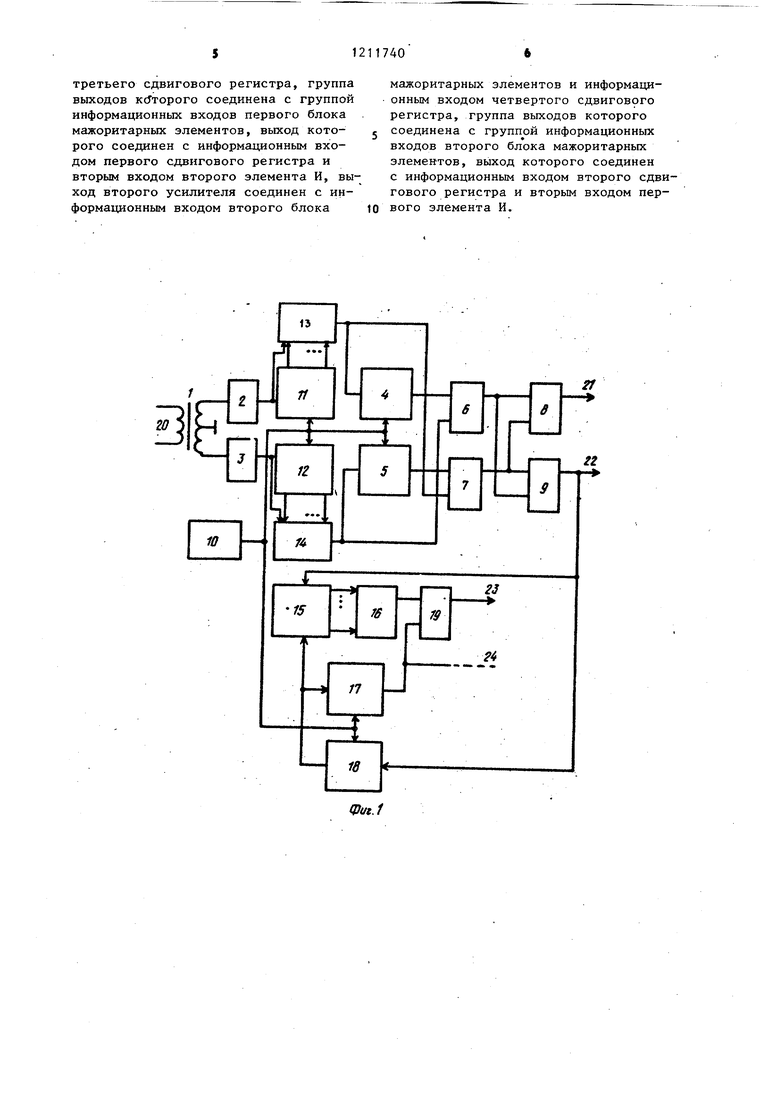

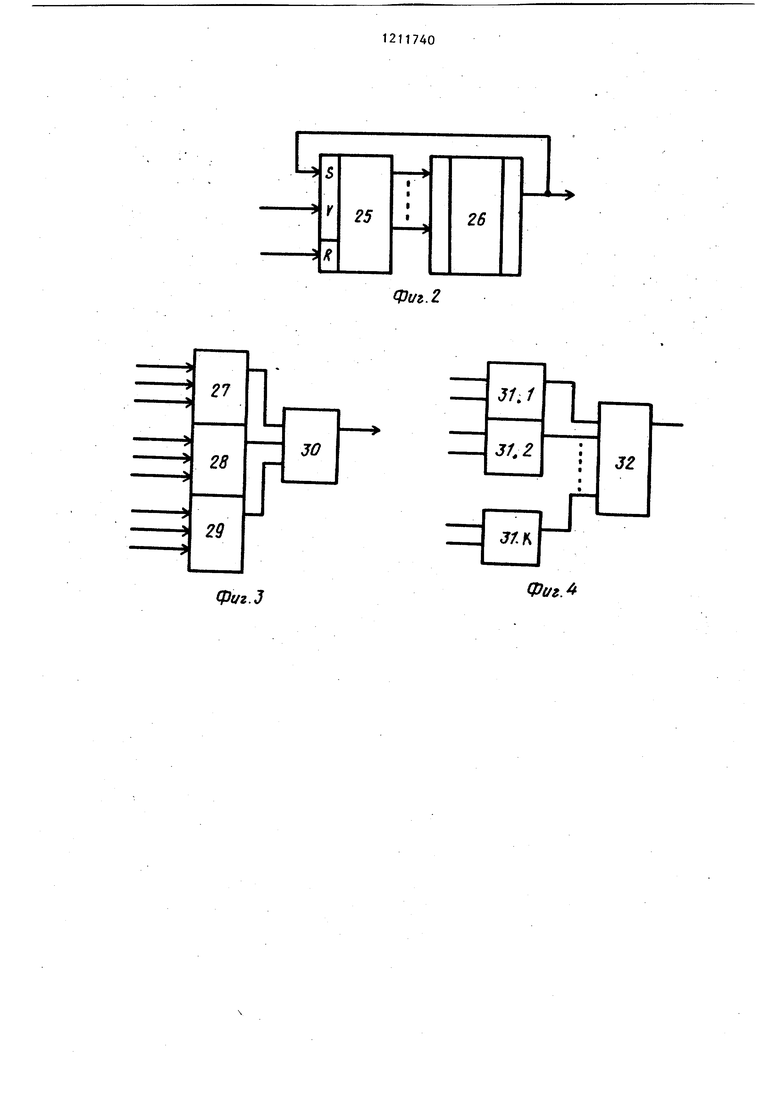

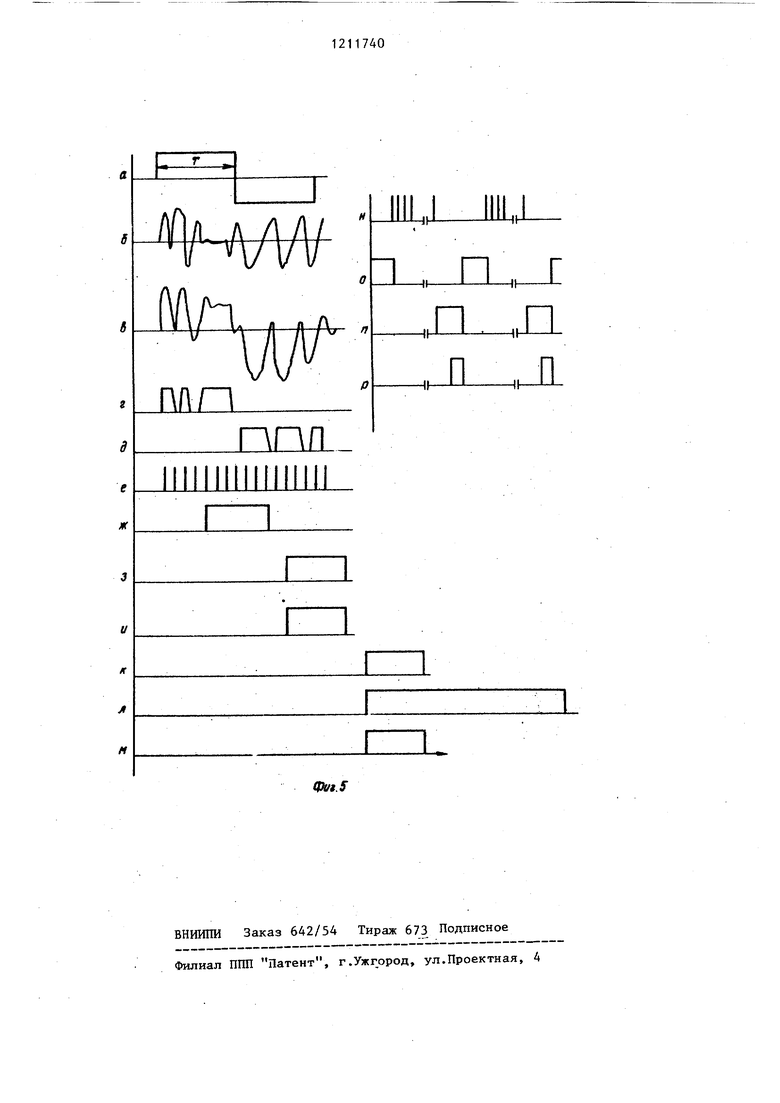

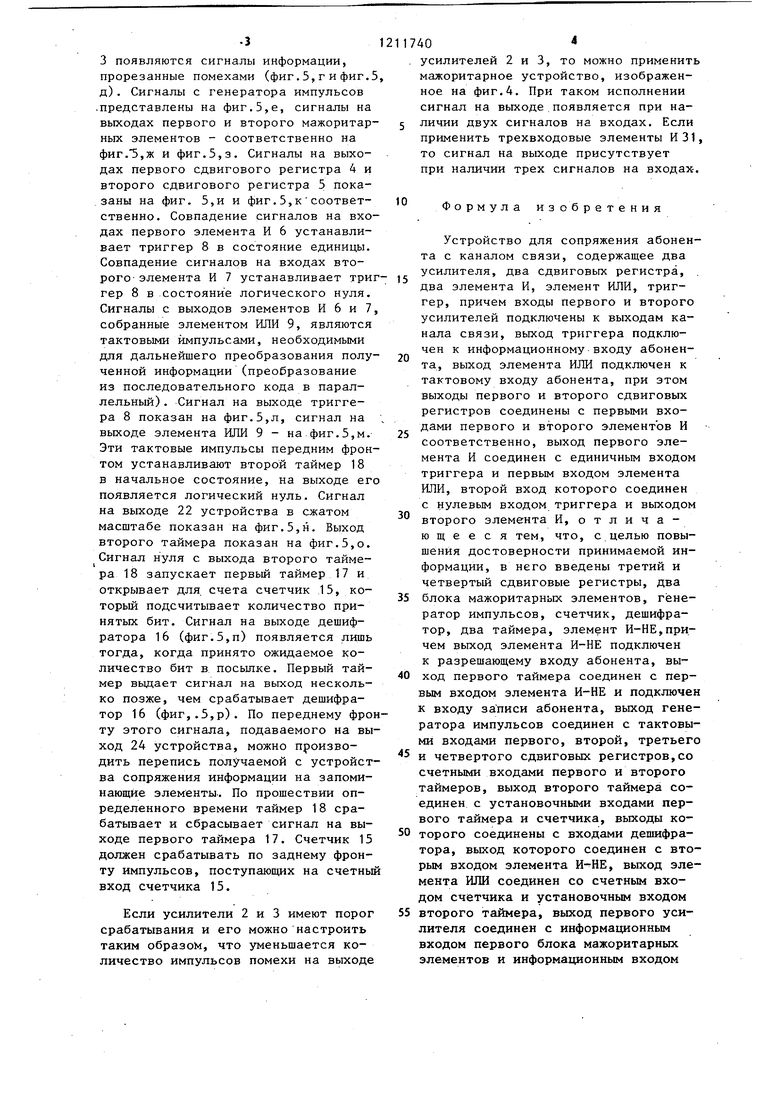

Цель изобретения - повьшение достоверности принимаемой информации. На фиг,1 представлена функциональная схема устройства; на фиг.2 таймер; на фиг.З и 4 - мажоритар- ный элемент; на фиг.5 - временная диафрагма работы устройства.

Устройство сопряжения (фиг.1) содержит транформатор 1, первый усилитель 2, второй усилитель 3, первы сдвиговой регистр 4, второй сдвиговой регистр 5, первый элемент И 6, второй элемент И 7, триггер 8, элемент ИЛИ 9, генератор 10 импульсов, третий сдвиговый регистр 11, четвертый сдвиговый регистр 12, первый блок 13 мажоритарных элементов, второй блок 14 мажоритарных элементов, счетчик 15, дешифратор 16, первый таймер 17, второй таймер 18, элемен И-НЕ 19, вход 20 устройства, информационный выход 21, тактовый выход 22 выход 23 разрешения, выход 24 записи.

Таймер (фиг.2) состоит из счетчика 25 и дешифратора 26. Счетчик считает, если на входе С присутствует потенциал логического нуля, и останавливается, если на входе С появляется потенциал логической единицы.

Блок мажоритарных элементов (фиг.З),например, для девяти входов состоит из стандартных трехвходовых и мажоритарных элементов 27 - 30, соединенных, как показано на фиг.З.

Другой пример выполнения блока мажоритарных элементов представлен на фиг.4. Он состоит из элементов И 31.1 -И 31.К и элемента ИЛИ 32.

Устройство работает следующим образом.

До прихода сигнала информации, вид которого представлен на фиг. 5, а, на выходах усилителей 2 и 3 присутствует потенциал логического нуля, на фоне которого появляются импульсы помехи. Генератор 10 импульсов постоянно вьщает сдвигающие импульсы на сдвиговые регистры. На выходе блока 13 или 14 (фиг.З) появляется сигнал лишь в том случае, если на большинстве его входов присутствует сигнал (например, на 5

10

15

0

11

5

5

0

5

0

5

0

5

740

входах из 9). При применении блока 13 или 14, выполненого по фиг.З, полагается, что сигнал помехи занимает меньше времени, чем сигнал информации на фоне помех. На фиг. 5,б показан пример сигнала помехи. Частота генератора 10 выбрана таким образом, что сдвиговые регистры 4, 5, 11, 12 задерживают сигналы на время Т (фиг.5,а).

Сигнал на выходе элементов И 6 и 7 появляется лишь в том случае, если- сигнал появился на выходе одного блока 14 или 13 и через время Т появился на выходе параллельного блока 13 или 14, т.е. если сигнал помехи повторяет форму полезного сиг- нала. До прихода сигнала информации на тактовом выходе устройства (на выходе элемента ИЛИ 9) присутствует потенциал логического нуля. На выходе второго таймера 18 - потенциал логической единицы, так как счетчик 25, входящий во второй таймер 1 8, при наличии потенциала логического нуля на нулевом входе при включении питания досчитывает до числа, определяемого дешифратором 26, входящим во второй таймер 18. На выходе первого таймера 17 присутствует потенциал логического нуля, так-как счетчик 25, входящий в первый таймер 25, устанавливается в нулевое состояние по нулевому входу потенциалом логической единицы, поступающей с выхода второго таймера 18. Потенциал логической единицы с выхода второго таймера 18 держит также в нулевом состоянии выходы счетчика 15. На выходе элемента И-НЕ 19 - логическая единица, говорит о том, что в данный момент времени принято неправильное количество бит. На выходе записи устройства присутствует логический нуль, говорящий о том, что с принятой информацией не следует проводить никаких операций. На тактовом выходе - логический нуль. Информация на вьпсоде триггера 8 и выходе устройства 21 игнорируется, так как она при отсутствии тактовых импульсов и наличии запрещающих сигналов на выходах устройства 23 и 23 не должна обрабатьшаться устройствами, использующими информацию с выхода 21.

С приходом сигнала, содержащего информацию на выход 20 устройства (фиг.5,в), на выходе усилителей 2 и

3

3 появляются сигналы информации, прорезанные помехами (фиг.5,г и фиг,5 д). Сигналы с генератора импульсов .представлены на фиг.5,е, сигналы на выходах первого и второго мажоритарных элементов - соответственно на фиг.5,ж и фиг.5,3. Сигналы на выходах первого сдвигового регистра 4 и второго сдвигового регистра 5 показаны на фиг. 5,и и фиг.5,к соответственно. Совпадение сигналов на входах первого элемента И 6 устанавливает триггер 8 в состояние единицы. Совпадение сигналов на входах второго- элемента И 7 устанавливает триг гер 8 в состояние логического нуля. Сигналы с выходов элементов И 6 и 7 собранные элементом ИЛИ 9, являются тактовыми импульсами, необходимыми для дальнейшего преобразования полученной информации (преобразование из последовательного кода в параллельный) . Сигнал на выходе триггера 8 показан на фиг.5,л, сигнал на выходе элемента ИЛИ 9 - на.фиг.5,м. Эти тактовые импульсы передним фронтом устанавливают второй таймер 18 в начальное состояние, на выходе его появляется логический нуль. Сигнал на выходе 22 устройства в сжатом масштабе показан на фиг.5,н. Выход второго таймера показан на фиг.5,о. Сигнал нуля с выхода второго таймера 18 запускает первый таймер 17 и открывает для счета счетчик 15, который подсчитывает количество принятых бит. Сигнал на выходе дешифратора 16 (фиг.5,п) появляется лишь тогда, когда принято ожидаемое количество бит в посылке. Первый таймер вьщает сигнал на выход несколько позже, чем срабатывает дешифратор 16 (фиг,.5,р). По переднему фронту этого сигнала, подаваемого на выход 24 устройства, можно производить перепись получаемой с устройства сопряжения информации на запоминающие элементы.. По прошествии определенного времени таймер 18 срабатывает и сбрасывает сигнал на выходе первого таймера 17. Счетчик 15 должен срабатывать по заднему фронту импульсов, поступающих на счетный вход счетчика 15.

Если усилители 2 и 3 имеют порог срабатывания и его можно настроить таким образом, что уменьшается количество импульсов помехи на выходе

211740

. усилителей 2 и 3, то можно применить мажоритарное устройство, изображенное на фиг.4. При таком исполнении сигнал на выходе появляется при на- 5 личии двух сигналов на входах. Если применить трехвходовые элементы И 31, то сигнал на выходе присутствует при наличии трех сигналов на входах-.

10

Формула изобретения

15

20

25

Устройство для сопряжения абонента с каналом связи, содержащее два усилителя, два сдвиговых регистра, . два элемента И, элемент ИЛИ, триггер, причем входы первого и второго усилителей подключены к выходам канала связи, выход триггера подключен к информационному входу абонента, выход элемента ИЛИ подключен к тактовому входу абонента, при этом выходы первого и второго сдвиговых регистров соединены с первыми входами первого и второго элементов И соответственно, выход первого элемента И соединен с единичным входом триггера и первым входом элемента ИЛИ, второй вход которого соединен с нулевым входом триггера и выходом второго элемента И, отличающееся тем, что, с целью повышения достоверности принимаемой информации, в него введены третий и четвертый сдвиговые регистры, два

35 блока мажоритарных элементов, генератор импульсов, счетчик, дешифратор, два таймера, элемент И-НЕ,причем выход элемента И-НЕ подключен к разрешающему входу абонента, вы40 ход первого таймера соединен с первым входом элемента И-НЕ и подключен к входу записи абонента, выход генератора импульсов соединен с тактовыми входами первого, второй, третьего

45 и четвертого сдвиговых регистров,со счетными входами первого и второго таймеров, выход второго таймера соединен с установочными входами первого таймера и счетчика, выходы ко50 торого соединены с входами дешифратора, выход которого соединен с вторым входом элемента , выход элемента ИЛИ соединен со счетным входом счетчика и установочным входом

55 второго таймера, выход первого усилителя соединен с информационным входом первого блока мажоритарных элементов и информационным входом

третьего сдвигового регистра, группа выходов которого соединена с группой информационньпс входов первого блока мажоритарных элементов, выход которого соединен с информадионным входом первого сдвигового регистра и вторым входом второго элемента И, выход второго усилителя соединен с информационным входом второго блока

мажоритарных элементов и информационным входом четвертого сдвиговрго регистра, группа выходов которого соединена с группой информационных входов второго блока мажоритарньк элементов, выход которого соединен с информационным входом второго сдвигового регистра и вторьш входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для сортировки информации | 1986 |

|

SU1386989A2 |

| Устройство для анализа неисправностей ЭВМ | 1981 |

|

SU957213A1 |

| Резервированное устройство | 1989 |

|

SU1635185A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для передачи и приема информации | 1983 |

|

SU1156109A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1229968A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

Устройство относится к цифровой вычислительной технике и можеть быть использовано в аппаратуре передачи данных. Основной задачей устройства является повышение достоверности принимаемой информации. Устройство содержит трансформатор, два усилителя, генератор импульсов, четыре сдвиговых регистра, два блока мажоритарных элементов, счетчик, дешифратор, два таймера, элемент ИЛИ,два элемента И, элемент И-НЕ. 5 ил. 4;

21

Фиг.г

27

J/./

28

Г

30

29

J/,

Jf

J/.K

Фиг.д

Фиг A

nnn

П .. П

ппп

Illllllllllllllll

nn

r I

| Способ и схема обработки бинарной информации,содержащейся в сигнале трех уровней | 1980 |

|

SU926638A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система для контроля электронных устройств | 1980 |

|

SU1005063A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-22—Подача