1зобретение относится к запомина- ющим устройствам и може быть использовано в устройствах сопряжения вычислительных машин, в адаптивных системах измерений и вьгчислительньо системах для сопряжения их с каналами передачи информации.

Целью изобретения является повышение надежности устройства.

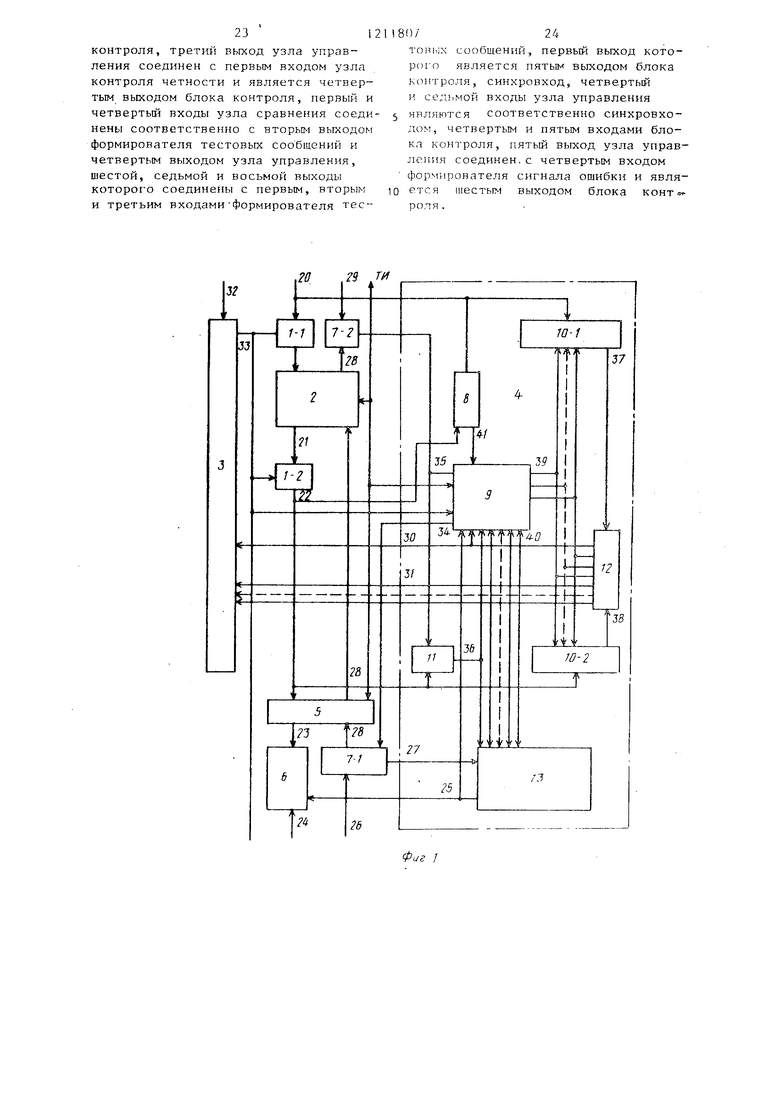

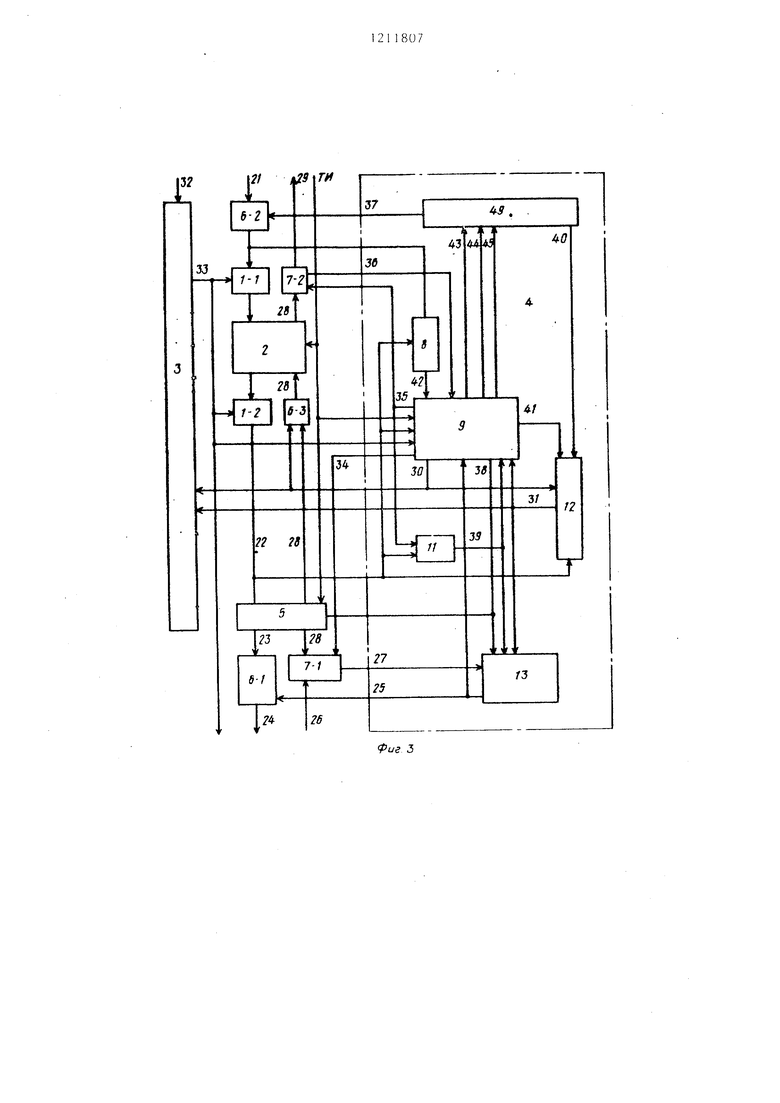

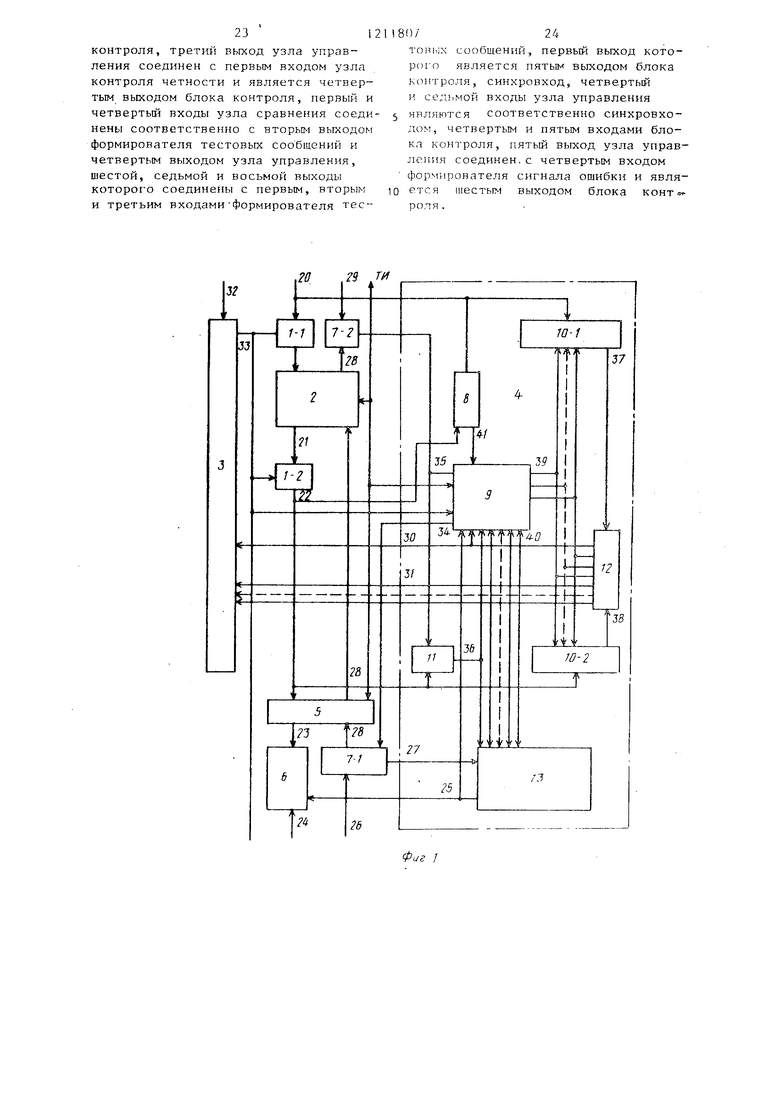

На фиг. 1-2 представлены функцио- нальные схемы буферного запоминающего устройства, первьш вариант выпол-нения; на фиг.3-4 - то же, второй вариант выполнения.

Устройство содержит коммутаторы ii-1, 1-2, накопитель 2, блок 3 -управления, блок 4 контроля, буферный регистр 5, блоки элементов tUiH 6, ключевые злементы 7, нуль-орган 8, узел 9 управления, узлы 10 строчного контроля, узел 11 контроля четности, узел 12 сравнения, формировате ль 13 сигнала ошибки, триггеры 14, элемен- ты ИЛИ 15, элементы И 16, элементы 17 запрета, распределитель 18, груп- па анализаторов 19 активности, входы-выходы 20-48 устройства, формиро ватель 49 тестовых сообщений, элемент 50 задержки.

Вход 20 буферного запоминаюшего устройства (h -разрядный) соединен с входом первого коммутатора -1 и первым входом блока 4 контроля, выход коммутатора 1-1 соединен с (иt k)-разрядным входом накопителя 2 информадии, () -разрядный выход 21 которого соединен с входом второго коммутатора 1-2, выход 22 которого соединен с вторым входом блока 4 и входом буферного регистра- 5, выход 23 которого через блок эле ментов ИЛИ 6 подключен к i. -разрядному выходу 24 устройства, а торой вход 25 группы элементов ИЛИ 6 соединен с вторым выходом блока 4 контроля, при этом управляющий вход устройства является входом первого ключевого элемента 7-1, первьп- выход 27 которого соединен с третьиз входом блока 4, а второй выход 28 через управляющие вход 28 и выход 28 регистра 5 и накопителя 2 соединен с входом 28 второго ключевого элемента 7-2, выход которого является управляющим выходом 29 устройства. синхронизирующий вход ТИ которого является синхровходом накопителя 2 информадии, регистра 5 и блока 4,

|

.; :-, с;

5

8072

упра.вляющий выход 30 и гтервый выход 3. которого соединены соответственно с управляющим входом блока 3 уг равления, второй управляющий вход I ксп орого является входом сброса 32 устройства, а выход 33 блока 3 яц- ляется сигнальным выходом ycTpo i- ства, а также соединен с управляю- ai;-i m входами коммутаторов 1-1 и 1-2 и четвертым входом блока 4, третий 34 и четвертый 35 выходы К(5торого соединены с управляющими входами соответственно первого 7-1 и второго 7-2 ключевых элементов.

ПервьЕ вход 20 блока 4 контроля является входом первого узла строчного контроля 10-1 и первьм входом нуль-органа В,, второй вход которого я зляется вторым входом 22 блока, который является также входом второ- I o узла 10-2 строчного контроля к вторым входом узла 11 контроля четности вькод 36 которого соединен с вторым входом узла 9 управления проверкой и вторым входом формирователя 3 си нала ошибки, первый вход 27 и выход 25 которого являются со- (П ветственно третьим входом к вторым вых.одом блока, а выход 25 соединен также и с первьм входом узла 9, первый выход 30 которого является управляющ -1м выходом блока и соединен с третьим входом узла 12 сравнения, ;1ервый 37 и второй 38 входы которого соединены с 1зыходами узлов 10-1 и 10-2 строчного контроля, управляющие входы которых и четвертый вход узла 12 соединены с четвертым выходом 39 узла 9, пятьк выход 40 кото- рог о соединен с четвертым входом узла 13, при этом выход узла 12 сравь:ения является первым выходом 31 блока, а также соединен с третьим а кодом формирователя 13 сигнала отибки и пятым входом узла 9 управления, третий вход которого соединен с выходом 41 нуль-органа 8, кроме тэго четвертый вход 33 и синхро- иход ТИ;, а также третий 34 и четвер- тьл-i 35 вьзходы блока являются соответ- стненно четвертом входом, синхровходом, вторым и третьим: выходами узла 9 управленияS а его третий вьосод.ЗЗ соединен также с первым входом узла контроля четности.

Буферный регистр 5 вьтолнен логично регистрам накопителя 2. Ключевой элемент 7-2 собран на эле5

0

5

менте запрета. Ключевой элемент 7-1 содержит элемент запрета с выходом 28 и элемент И с выходом 27.

. Нуль-орган 8 собран по схеме реверсивного счетчика. На выходе 41 имеется сигнал, если в накопителе 2 нет информации.

Узлы 10 строчного контроля содержат м-разрядные счетчики, число которых соответствует числу разря- дев сообщения. Переполнение счетчиков не должно нарушить общего счета.

Узел 11 контроля четности может быть собран по любой известной схем и должен формировать сигнал ошибки при нарушении поперечной пословной четности сообщений.

Узел 12 сравнения реализует порарядное сравнение контрольных чисел каждой строки, последовательно поступающих на его входы 37 и 38, с выдачей в соответствующую цепь выхода 31. При этом номер цепи выхода 31 определяется номером цепи на входе 39.

Формирователь 13 сигнала ошибки содержит регистр, аналогичный регистрам накопителя 2, и логические элементы , обеспечивающие запись в его разряды байта состояния с признаком ошибки четности и байта уточненного состояния с признаками номе ров каналов, в которых обнаружена строчная ошибка.

Группа анализаторов 19 активност например дифференцирующая цепь, формирует сигнал на выходе по переднему фронту сигнала, поступающего на его вход.

Узел управления проверкой (фиг.2 работает следующим образом.

Выход первого триггера 14-1 является вторым выходом 34 узла, его первьй вход соединен с выходом первого элемента ИЛИ 15-1, а второй вход 25 является первым входом узла второй вход 36 которого соединен с первыми входами первого элемента ИЛИ 15-1 и второго триггера 14-2, выход которого является третьим выходом 35 узла, а также соединен с прямым входом первого элемента 17-1 запрета и входом первого элемента И 16-1, второй вход которого является третьим входом 41 узла, а его выход является первым выходом 30 узла и, кроме того, соединен с инверсным входом первого элемента 17

5

0

5

5

5

0

0

5

0

запрета, выход которого соединен с первым входом 42 распределителя 18, ныход первого элемента И 16-1 соединен также с первыми входами второго 6-2 и третьего 16-3 элементов И, при этом второй вход третьего элемента И 16-3 является синхровходом узла, а его выход соединен с вторым входом 43 распределителя 18, первый выход 44 которого соединен с прямым входом второго элемента 17-2 запрета и вторыми входами первого элемента ПЛИ 15-1 и второго элемента И 16-2, выход которого соединен с первым входом второго элемента ИЛИ 15-2, а третий вход через третий триггер 14-3, третий элемент ИЛИ 15- 3 и группу анализаторов 19 активности подключен к четвертому входу 33 узла, пятый вход 31 которого через четвертый элемент ИЛИ 15-4 подключен к первому входу четвертого триггера 14-4, выход которого соединен с инверсным входом второго элемента 17-2 запрета, выход которого соединен с вторым входом второго элемента НЛ1-1 15-2, вьгход которого соединен с вторыми входами второго 14-2, третьего 14-3 и четвертого 14-4 триггеров, а также является пятым выходом 40 узла, четвертый выход 39 которого является вторым выходом распределителя 18.

При поступлении на вход 36 сигнала (ошибка четности он поступает на вход триггера 14-2, который перебрасывается и на его выходе формируется сигнал, кроме того, сигнал с входа 36 через элемент ИЛИ 15-1 поступает на вход триггера 14-1, на выходе 34 которого также формируется сигнал. При поступлении на вход 25 триггера 14-1 сигнала (признака байта состояния) он возвращается в исходное состояние и сигнал с его выхода 34 снимается.

Сигнал с выхода триггера 14-2 поступает на вы-ход 35 узла (сигнал запрета приема информации в устройство и начала контроля четности) и на прямой вход элемента 17-1 запрета, на выходе 42 которого формируется сигнал, поступающий на первые входы триггеров 14-5, 14-6, 14-7, которые перебрасьюаются и на их выходах формируются сигналы. Эти . сигналы поступают на первые элементов И 16-4, 6-5 и 16-6, частично разрешая их, а также на инверсные входы злементов загфета 17-3, 17-4 и 17-5; которые запрещаются .

Кроме того, сигнал с вькода три1

гера 14-2 поступает на вход элемента И 16-1.5 поэтому при поступлении на вход 41 сигнала признака отсутствия информации в накопителе) на его выходе формируется сигнал, по-- ступающий на выход, 30 узла (сигнал разрешения сравнения и перЕ распре- деления каналов),а на инве зсныС; вход элемента П-, с выхода 42 которого снимается сигнал, и на входы элЕмектоБ И 6-2 и l ci-3. Поэтому тактовые сигналы ТИ, поступающие на вход элемента И 16-3 ются па его выход 43 с которого постунают на входы элемента и элeмe} тa И 16-4. Пр-и этом тактовг, сигнал поступает через элемент И 16-4 па выход 39-1 (считывание дтьч С1)авнения кодов первой строки и подачи результата сравнения в цепь первого канала), а также на вход тригтера 14-5, котог)ый eosiipaiuaeT- ся п исходное состояние и сигнал с его выхода снимается,. При этом за-- прещается элемент И i 6-4 и разрешается элеь е1гг 17-3 запрета. Поэтому следующий такт(5вый сигнал ТИ с входа 43 через элемент 17-3 запрета и элемент v I 6-5 поступае Т на выход 39-2 и на вход T{)iii repa 14-65 котор возвращается i; исхо/июе состояние,

Пос:ле выдачи рас :рс;;елителем 18 всех унравляющих с;п } алон . необходирольных кодов 1:-:исел; ;о каждой строке (г;ана:1у| сигнал поступает на выход 44, с которого подается на вторые входы зл:еме;; :-а ilMii 16-1 и элемента И 16-2, а на прямой вход элемента 17-2 запре 1 а .

Возможны два случая. В первом ошибка четности возпикает за пределами устройства, тсзгда нет строчной ошибки в канале. Поэтому на вх;: 31 элемента ИЛИ 15-4 сигнал не поступает и триггер 14-4 остается в исходном состоянии, В этом случ;:1.: на выходе элемента 17-2 запрета формируется сигнал, поступающий на вход элемента ИЛИ 15-2,

Во втором есть строчная ошибка в- одном из каналов, и сигнал с; вхо.д 31 через элемент ИЛИ 15-4 подается на вход триггера 14- -i. на зыходе

С

которого формируется сигнал, поступающий на иliвepcE ый вход элемента 17-2 занрета и запрещающий его.

В этом случае после перераспределения каналов на вход 33 поступает сигнал, который через группу анализаторов 19 активности и элемент ИЛИ 15-3 переключает триггер 14-3, с выхода которого поступает на третий вход элеме}1та И 16-2, на выходе которого формируется сигнал, поступа- юишй через элемент ИЛИ 15-2 на выход 40 узла и на вторые входы триггеров ;4-2,. 14-3 и 14-4, которые возвращаются в исходное состояние. При этом г.нимаются сигч1алы с выходов 35,30 и 4U. Сигнал с вькода 34 снимается ггосле поступления на вход 25 триггера 14-1 п ризнака передачи байта у; очвеююго состояния.

- Буферное запоминающее устройство лерному варианту ( фиг . 1 ) работает (следующим образом.

При наличии сигнала на выходе 29 на вход 20 устройства поступают с(;оГ)ще)шя. Эти сообщения подаются lia Бход узла 10-1 и построчно через cvMM;i.TOp - на вход накопителя 2, )s котором такто 1ыми сигналами ТИ ((юощения 1:1родвигаются к его выходу

21.

После г:оступления в первый ре- тис-тр накопителя 2 очередного сооб- цсния снимается сигнал с его выхода 28 а следовательно,и с выхода 29 устройства, при освобождении первого регистра накопителя 2 на выходе 28 формируется сигнал, который через к:тючевой элемент 7-2 поступает на выход 29 устройства. В ответ на этот сигнал на вход 20 наступает г черсдное сообщение.

При }1аличии сигршла на входе 28 :;.: КОГ1ителя 2 тактовые сигналы ТИ считывают сообщения с-накопителя 2 d. выход 21, с которого сообщения (:рез KOhfM -татор 1-2 поступают на 22 узлов 10-2 строчного конт- о:;ля, 1 де суммируются построчно единиц, и узла I 1 ,, в котором рс:ализуется проверка на четность :каждо; о сообщения, и при ее наруше- :i.HK iia вькоде 36 формируется сигнал О Нибки четности,

Крдме того, сбобщения с выхода

22коммутатора 1-2 поступают на ход регистра 5, с вькода 28 которого гл-;И1 5ается сигнал,- поэтому очеред- з;ые сообщения ожидают в накопителе

2 освобождения регистра 5. Если на входе 26 устройства имеется то он через ключевой элемент 7-1 поступает на вход 28 регистра 5, который при поступлении на его вход ТИ тактового сигнала выдает сообщение на выход 23, с которого оно через элементы ИЛИ 6 поступает на выход 24 устройства. При этом регистр 5 освобождается от информации и на его выходе 28 формируется сигнал готовности принять очередное сообщение.

Если на вькод 36 узла 1 поступает сигнал ошибки четности, то он поступает на вход узла 13 и запомин ется в байте состояния, а также подается на вход узла 9, на вькодах 34 и 35 которого формируются сигна- лы. Сигнал с вькода 35 поступает на входы узла I1, запрещая контроль четности, и ключевого элемента 7-2, который запрещается и сигналы на выход 29 не подаются, что исключает подачу очередных сообщений-на вход 20 устройства.

Сигнал с выхода 34 узла 9 по- ступает на вход ключевого элемента 7-1, который отключает вход 26 от выхода 28 и соединяет его с выходом 27. Поэтому сигнал готовности принять очередное сообщение с входа 26 подается через ключевой элемент 7-1 на вход 27 узла 13, который выдает байт состояния с признаком ошибки четности на выход 25, с которого он через элементы ИЛИ 6 поступает на выход 24, а признак сообщения поступает также на вход 25 узла 9, который снимает сигнал с выхода 34, и ключевой элемент 7-1 возвращается в исходное состояние, при котором его вход 26 соединен с выходом 28. Поэтому сообщения, имеющиеся в накопителе 2, передаются на выход 24 аналогично описанному. После освобождения накопителя 2 от информации на выходе 41 нуль- органа 2 формируется сигнал, поступающий на вход узла 9, который формирует сигналы на выходах 30 и 39. Сигнал с выхода 30 поступает на входы узла 12 сравнения и блок 3 управления и разрешает их работу. Сигналы с выхода 39 поступают на входы узлов 10-1, 10-2 и 12. При этом синфазно на выходы 37 и 38

10

15

20

5

0

5

Q

5

0

5

ь(в

з: юв 10-1 и 10-2 последовательно поступают числа, соответствующие количеству единичных бит в соответ- ств то1пей строке, которые сравнива- югся в узле 12. Если коды равны, 1О сигнал на выходе 31 не формируется. Если числа не равны,то формируется сигнал ошибки, поступающий Б одну из цепей выхода 31. При этом цепь выхода 31 соответствует той цепи входа-39, в которой в данное время имеется сигнал.

Сигнал строчной ощибки соответствующего канала передачи информации с выхода 31 узла 12 поступает в узлы 9 и 13, а также в блок 3.

Если строчной ошибки нет, то узел 13 выдает байт уточненного состояния с признаком исправности всех каналов, а узел 9 заканчивает проверку, снимает управляющие сигналы и разрешает продолжену е передачи информации.

При наличии строчной ошибки узел 13 запоминает номер канала, в котором возникала ошибка, т.е. формирует байт уточненного состояния, что позволяет определить разряды сообщений части переданного массива от байта состояния до байта уточненного состояния, в которых возможна ошибка с целью последующей корректировки таких сообщений.

В блоке 3 при этом формируется управляющий сигнал на отключение неисправного канала и подключение резервного. Этот сигнал подается в соответствующую цепь выхода 33 блока 3, с которого сигнал подается на сигнальный выход устройства и на управляющие входы коммутаторов каналов 1-1 и 1-2, которые исключают неисправный и подключают резервньш каналы. Кроме того, сигнал с выхода 33 блока 3 поступает на вход узла 9.

Узел 9 после проверки всех каналов, т.е. после сравнения всех чисел узлов 10, формирует сигналы на выходах 34 и 40 и снимает с выходов 30 и 35. При этом сигнал с выхода 34 поступает на вход ключевого элемента 7-1, а сигнал с выхода 4 - на вход узла 13, который подает на выход 25 байт уточненного состояния, которьй через элементы 6 РШИ поступает на выход 24, а признак байта поступает на вход узла 9, который снимает сигнал с выхода 34.

Поэтому сигналы с вхо,гш 27 -черса клйчевой элемент 1 -} Г1одаютг;я на вход 28 регистра 5„

Снятие сигнала с выхода 30 запрещает работу узла 12 к блока 3„

3 снятие сигнала с .выхода

запрещает работу узла 11 контроля чег- кости; а также снимает занрет с ключевого элемента 7-2 котсрьш передает сигналы с входа 28 на ныход 29, В ответ на эти сигналы на 13ХОД 20 устройства ностунают очередные сообщения5 которые ан.ало1-ичн онисаннону нередаются на его выход 2 4 ,

Сигнал с выхода АО также снимается .

Предла.т аемый вариант буферно: о запоминающего устройства обладает простотой решения поставленной задачи и небольшой задержкой в ;1е1зеД( :- че информадии, необход шой для нро- нерки и корректировки каналов нере- дачи данньк,

В то же время он имеет недоста- чж 5 который заключае тся в тоМ; что нри передач.е большого объема инфорь;адии в устройстве не ксклнчен едини шый сбой ,,которь;й ггриводит к корректировке каналов передачи даннь;х и тем самым к преждевременному исполаъ ; О1 ани10 резервных каналов и iioisKc нерсгдачи данг1ых,.

С делью З С граненл- я указанного недостатка и новыиени}; надежности контроля предлагается второй ант освобожденл- я након ителк 2 о информадии. Через него пропускается группа. тесто1- ь:х сообщенил , по ре- зулвтатам анализа которой принимается решение на корректировку каналоБ передачи данньгх.

При этом зозраст ает время задерж I;H в передаче информадии (особенно тех случаях, когда накопитель 2 имеет большую емкость) ., которое не- обходимо для проверки /и коррект1-г0о,г 1 ;и каналов передачи данных, а также усложняются функциоиальные езязи,

Вход 21 буо зерного запоминающего -устройства ( п - разрядньш j является ггервьпм входом второго блока злеА::е;{ - тов ИЛИ 6-2, второй 37 вход котсрой соединен с пятым выходом блока k 1 онтроля5 а выход - с входом первото коммутатора

и первым вхор.ом

Е Лска 4 контроля, выход коммутатора 1-1 соединен с (ni И )азрядным вхо

80710

дом накопителя 2 информации ( г; 1) - paзpядн лй В1ьгход которого соединен с лтсрым входом блока 4 и нервым Еходо1м буферного регистра 5, вькод 23 которого через первый блок эле- I eHTO; ИЛИ 6-1 подключен к п раз рядному выходу 24 устройства а второй вход 25 группы э.чементов ИЛИ б -i соединен с вторым выходом блока ког-;троля, нри этом управляющий нход 25 устройства является входом

.первого ключевого элемента 7-1, первый выход 27 которого соединен с третьим входом блока 4, а второй ьыход 28 через управляющие вход 28 и ;зыход 28 регистра 5, блок элементов 1 1И 6-3 и накопитель 2 соединен с нходом 28 второго ключевого элемента 7-2 ,. первьш выход которого является упр;)нляющим выходом 29 устройства, а выход соедипен с пятым входом контроля „ сипхронизир-ующий F5X04. устройства является синхро- iixoiJ,oM накопителя 2 информадии, ре- ;-И1: гра 5 и 6JiOKa 4 контроля, управ- , 1янлга1й выход 30 и первьш выход 31 кот(1рого соединены соответственно :; нторь.м входом блока элементов ИЛИ 6-3, первьп- управляющим входом п -ixo.-HJM блока 3 управления, второй упр;и лкющий вход которого является BXfiiio - 32 сброса устройства, а вы- ;сод 33 блока 3 является сигнальным г.ьп-го/лом устройства и соединен с унрггв.икющкми В ХОД а МИ коммутатора 1 :-: 1-2 и четвертым входом блока 4, Т тетий 34, четвертый 33 и шестой 38 которого соединены соответ- гггвенно с управляющими входами нер- восо 7-1, второго 7-2 ключевых эле- ,пе;; ;-ов и вторым входом буферного регистра Ъ,

1ервый вход блока 4 контроля явля- I первым входом нуль-органа В, ;-ой вход которого является вторьм :,см 22 блока, и соединен с шестым :ом узла управления проверкой и входами узла i 2 сравнения ;j:a 1 1 контроля четности, выход :;iroporo соединен с вторыми вхо- : узлов управления проверкой формирователя 13 сигнала оиибкИ; (ьгл вход 27 и ныход 25 которого ютйя соответственно третьим :ом и вторым выходом блока, а ;д 25 соединен также и с первым 1,ом узла 9 5 первьгй выход 30 кото- : ярпяетдя управляющим выходом

блока и соединен с третьим BxoflONf узла 12 сравнения, первый 40 и четвертый 41 входы которого соединены соответственно с вторьм выходом формирователя 49 тестовых сообщений и четвертым выходом узла 9 управления, шестой 43, седьмой 44 и восьмой 45 выходы которого являются первььм, вторым и третьим входами формирователя 49 тестовых сообщений, первьш ю выход которого 37 является пятым выходом блока 4 контроля. Синхро- вход, седьмой 36 и четвертый 33 входы узла 9 управления являются соответственно синхровходом, пятым ts и четвертым входами блока 4 контроля, пятый 38 выход узла 9 управления является шесть м выходом блока 4 контроля и соединен с четвертым входом формирователя сигнала 13 20 ошибки, выход 31 узла 12 сравнения является первым выходом блока 4 контроля и соединен с третьим входом формирователя 13 сигнала ошибки и пятым входом узла 9 управления, тре- 25 тий выход 35 которого является четвертым выходом блока 4 контроля и соединен с первым входом узла 11 контроля четности.

Буферный регистр 5 выполнен ана- зо огично регистрам накопителя 2.

Ключевые элементы 7 содержат элемент запрета с выходом 28 (29) и элемент И с выходом 27 {2ь}.

Формирователь 49 тестовых сообщений - управляемое постоянное, запоминающее устройство с хранимыми в нем тестовыми сообщениями, которые в соответствии с сигналами на входе 44 последовательно подаются либо на выход 37, либо на выход 40 соответственно, при подаче сигналов на входы 43 или 45.

Узел 11 контроля четности может быть собран по любой известной схеме и должен формировать на выходе 39 сигнал ошибки при нарушении пословой четности сообщений.

Узел 12 сравнения реализует поразрядное сравнение контрольных чисел аждой строки, последовательно по- ступающих на его входы 0 и 22, с ошибки в соответствующую епь выхода 31 при наличии сигнала в оответствующей цепи на входе 41.

Формирователь 13 сигнала ошибки содержит регистр, аналогичный регистрам накопителя 2, и логические элементы, обеспечивающие запись в

35

4Q

ю ts 20 25

зо

5

Q

иго разряды байта состояния с признаком ошибки четности и байта уточнен- нсго состояния с признаками номеров каналов, в которых обнаружена строч- н;1я ошибка.

Группа анализаторов 19 активности например ди(х|)еренцирующая цепь, формирует сигнал на выходе по переднему фронту сигнала, поступающего на его вход.

Распределитель 18 может быть выполнен на основе кольцевого счетчика, выходной сигнал которого последовательно появляется на выходах 44, а затем на выходе 48.

Элемент 50 задержки может быть выттолнен на основе счетчика, вход 38 которого является входом обнуления счетчика, время задержки определяется числом тактовых сигналов ТИ, поступающих на его вход.

Узел 9 управления проверкой работает следующим образом.

Выход первого триггера 14-1 является вторым выходом 34 узла, его первый вход - первым входом 25 узла, а второй вход соединен с выходом первого элемента 1ШИ 15-1, первый вход которого является вторым 39 входом узла и соединен с первым входом второго триггера 14-2, выход которого является третьим 35 выходом узла и соединен с вторым входом первого элемента И 16-1, первый вход которого является третьим 42 входом узла и соединен с первыми входами второго элемента 17-2 запрета и второго элемента И 16-2, а вход которого является четвертым 41 выходом узла и соединен с вторыми входами четвертого элемента И 16-4 и элемента 50 задержки, вьгход которого соединен с вторым входом третьего Зо темента 17-3 запрета, выход которого соединен с вторым входом второго элемента ИЛИ 15-2, выход которого является пятым 38 выходом узла и соединен с третьим входом элемента 50 задержки и вторыми входами пятого и шестого триггеров 14-5 и 14-6, первым входом восьмого триггера 14-8 и вторыми входами второго, третьего и четвертого триггеров 14-2, 14-3, 14-4, при этом выход первого элемента И 16-1 соединен с первыми входами первого элемента 17-1 запрета и третьего тригтера 14-3, выход которого соединен с вторыми входами первого 17-1 и

второго элемеитон з мтрста, выАод KO i opoi o сг едннс} с парвьм входом четркртого трттера lA-A, выход которого является перзьш 30 выходом узлл и соединен со вторыми входами второго и третьего элементов И 16-2 и 6-3 и- первог О элеме:-:- та ИЛИ 15-1, при этом выход первого злемента 17-1 запрета соединен с первьми входами се,д,ьмого эл(ме1-:та ИЛИ 15-7 и седьмого триггера 14-7,, выход которого днляется шестым 43 выходом узла и соединен с вторым входом шестого элемента И 16-6,, третий вход которого является сед, MbfM 36 входом узда, а выход пен с; втор.ым входом niecToi O элемента Ш1И 15-6, выход 47 которого соединен с вторым входом раснрс.де- лителя 18, первый выход которого является седьмым 44 В)ходом узла, а второй 48 - соединен с вторьп- входом седьмого триггера 14-7 г: первьпч входом третьего элементй И 1 6-3 . выход которого соединег: с вторыми входами восьмого триггера 14-8 и седьмого элемента Г:ЛИ 15-7,, выхо/1 которого 46 соединен с нервьм входом распределителя 18, этом входами пятого элемента ИЛИ 15-5 является 1иеетой 22 вход узла, а выход пятого элемента tUIH 15-5 соединен с первым входом пятого элемента И 16-5, выход которот о соедю1ен с первы -; цходом inecToi o элемента ИЛИ 15-6, кроме того. Bf-,i- ход восьмого триггера 14-8 ивляе-гси 45 выходом узла к сс:е.г),;--:нен с вторым входом пятого элемента И 16-5, кроме тог о, входы грутшы анализаторов 19 активности гиляттсл четвертым 33 входом уяла,, а В ;1ходь группы анализаторов 9 активности соединены с входами чет1и;рт С1Го элемента ИЛИ 15-4, выход которого соединен с первым вхо,г;ом четвертого элемента И 16-4. выход котогюг о соединен с первым входом второгчэ элемента ИЛИ 15-2, кроме тог о, пхо; третьего элемента ИЛИ 15-3 вляюг с.я пятым 31 входом узла J а выход его элемента ИЛИ 15-3 соеди1- ен с первым входом пятого триггера 1--5 выход которого соединен с первым входом третьего элемента 7-2, синхровход ТИ узла соединен с пзр- входом шестого элемента И 1 5-6 и первым входом задержки 20.

1,1-п на,ч ; чоти(ку)п;. погту- пячипиГ: .на ХОД 39, нервюра. ывает Г1)и;-)тр -2, на л1,;Х(;де 35 KOfripcjro форл;Ируе-гч-я С):гна:(5 пс)ступаюи1ИЙ н: Е; вход злеме/и а 1 Ik-l и нп ныхпл уола 4, как cHi ii,:ui запоета 1фр:ем; KiiOopMauHH и контроля че пюси;. Кио- I or-O; СИ) нй,л с: входа 39 через ),;- :: ieirr ИЛИ 15-1 :тоступает на

O триггера 14-1, которьй }iepe6pacbaia- .,я м на сг о выхода формируется сит нал. постулаюшкк па ;5ыход 34 узла 4 сшл-им; на передачу байта сое-- Tc :iiH:irj , lifjcjiti пбре;1ач1- бай га состо5 нимя ii,;i иход 2Ь григгера 14-1 пост;, и;;ет прнз)1ак переданного байта cci TOj-iHiiH „ npii ЭТО1-1 триггер 14-1 . o;j; ряп аетс я к исхо;,пое состо ;н1;е , ч ;-иг1- ал °с его выхода 34 сиРгмается.

и При п(;сту 1: енли па вход 42 злемен- :: ii ;b-l осжтбондения на- к()r:т:lч ля С) : ;1;:форма 1;ии на его выхо- „II/ формируется CHi Haj, котсрыз через :э::1 l/--i запрета и з :снеит

- i:.,.ii, : jiociyiiacT вход расгфеде .пг:гл ; iB и чодготанлгизггет его к (Т1 е, кр,:, того,, с Г нал с выхода .-н :-;;: i/-i запрета поступает на -у ипч ;,;; la--, который :еребра-- Ci ;ь,;, г;-ч и с;пч;а,;; с его зыходг; нодатсч ;лл:;х сооо1яаннм I и на вход эле- i--i;;,:4 И 6-;)- Ч -г-тично разрешая - 41 :ччг п,ч :;г-и:и си пала на входе 36. i :-j4,)M (4iyi a:.: тактовые сигяаль ТИ ч( гч 3 ч::чч--сч;т И 16-6 поступают на Ч орой иход распределителя 18., на :Ч.ч. д ч, | ко1ч;рг;)о IO С Л е д ОН 3 Т е льно :;ч Ч, |;;игч а,ль считывания тестовьх (Ч ,, .

(игна:г с выхода з,лемента И 16-1 |1;)Ч чупч(: 1 также на вход триггера 3, А(Т( ттеребрасьшастся, и / 1.ЧЧС ныхо,де формируется сигнал,

М(Ч ТЧ-:1ЛЦ)1, VD пряМОЙ ВХОД ВТОрОТ О

ЧЧЧОН-1Ч1 17-2 -jaiipeTa, а также на п;Ч)Г:;)сиь:й :чхол пе,рвого элемента за- рч-ivi I /ч,-: хо . орый запрещается,

Ji4i гччстзЧ, н нако1;итель пер- -чч J т;.;СтовочО сообиения сьг на: с )да 42 с:чикае1ч::я т , е ,, снимается , ч-п,срсиогг; входа злемента 17--2 тгапрста, i-ia ;;1ыходе которого нри этом ф(; :- ;1руется сигнал 5 поступающий ia чхо.п триггера I 4-4 ,. которьш перебрасывается, и CKi-нал с его выхода 1(ичг гьчат на вход э: емеита 1 16-3

мня сравнения- н аил.чи-за KaiiiUioiH . Кроме того, сигнал с пыхода триггер 14-4 поступай - па вход элемента И 16-2 и через элемент ИЛИ 15-1 на вход триггера 14-1, на выхо 34 которого подается сигнал для выдачи байта уточненного состояния.

После того как распределитель 8 выдает псе сигналы для считывания тестовых сооб1цений сигнал подается на его выход 48, с которого поступа ет на вход триггера 14-7, который возвращается в исходное состояние, и сигнал с его выхода 43 снимается, при этом запрещается элемент И 16-6 и тактовые сигналы на вход 47 распределителя 8 не подаются.

Кроме того, сигнал с выхода 48 распределителя 18 поступает lui вход элемента Н 16-3, на выходе которого формируется сигнал, поступающий через элемент ИМИ 15-7 на вход 46 распределителя 18, который подготавливается для выдачи очередной серии па выход 44.

Сигнал с выхода элемента И 16-3 поступает также на вход тригг ера 14-8, которьй перебрасывается и на его выходе 45 формируется сигнал, поступающий на выход узла (сигнал разрешения подачи тестовых сообщений для сравнершя) и на вход элемента И 16-5 частично его разрешая.

При поступлении тестовых сообщений на вход 22 элемента l-LHH 15-5 сигнал с его выхода подается на вхо элемента И 16-5, на выходе которого в этом случае формируется си1 нал, который через элемент Ш1И 15-6 поступает.на вход 47 распределителя 18, который в этом случае подает сигналы на выход 44. Таким образом, каждое тес товое сообщение, поступающее на вход 22, формирует в соотвествующей цепи выхода 44 распределителя 18 очередной сигнал для считывания соответствующих тестовых сообщений из формирователя 49 тестовых сообщений (фиг.З).

После сравнения последнего тестового сообщения на вход 42 поступает сигнал, которьй подается на входы элементов 16-1 , 17-2, а также элемента И 16-2, на выходе которого формируется сигнал, поступающий на вход элемента И 16-4, на выход 41 устройства (сигнал считьшания результатов сравнения и на вход

I8(

:)jiCMeirra 50 задержк{1, которг,1Й запускается и начинает отсчитьшать пре- МП зл:1ержки, которое определяется чи.слом тактовых сигналов ТИ, посту- J пающих на его вход.

В ответ на сигнал, поступающий на выход 41, на вход 31 подается результат сравнения. При этом возможны два варианта. При первом

10 FU1 вход 31 поступает единичныебит ошибки, тогда через элемент ИЧИ 13-3 на вход триггера 14-5 поступает сигнал, триггер перебрасывается и сигнал с его выхода

15 поступает на инверсный вход элемента 17-3, который запрещается . При втором ошибки в канале нет, а значит нет сигнала на входе триггера I4-5, который остается в исходном

20 состоя1 ии. Поэтому элемент запрета 17-3 остается в разрешенном состоянии.

После коррекции каналов на вход 33 поступает сигнал откорректиро2.) ванного канала, этот сигнал через группу анализаторов 19 активности и 3JieNieHT 1ШИ 15-4 поступает на вход трпгтера 14-6, который перебрасывается и сигнал с его выхода поступа30 с i на вход элемента И 16-4, на выходе которого при этом формируется сигнал, поступающий через элемент И. I 5-2 на выход 38 для выдачи байта уточненного состояния и об- )1уле}шя буферного регистра. После пере.чачи байта уточненного состояния нл вход 25 поступает сигнал, которым триггер 14-1 возвращается в исходное состояние и сигнал с его выхода 34 снимается.

Кроме того, сигнал с выхода элемента ИЛИ 15-2 поступает на вторые входы триггеров 14-2, 14-3,14-4, 14-5, 14-6, 14-8, которые возвращаются в исходное состояние и сигналы

5

0

5

0

5

с их выходов снимаются.

Сигнал с выхода элемента ИЛИ 15-2 поступает также на вход задержки 50, которая сбрасывается и счет времени задержки прекращается.

Если бы на входы 33 не поступили сигналы о произведенной коррекции каналов, то после заданного времени на выход задержки 50 поступает сигнал, который подается на вход элемента 17-3 запрета. При этом возможны два случая. В первом элемент 17-3 запрета разрешен, и на его вы17

ходе формируетс;я сиг ип.тц кото;эь1Й через элемент ИЛИ 15-2 постз/пает : его выход 38 ji глкмает все yn:JSHj) i- ющие сигнал. аналогично описанно:-О - Во втором элемент 7-3 запрещается сигналом на его итгверсном входе,; тогда на выходе элемента. i сигнал не формируется и ycTpoi iCTBi::- нрекрагцает прием и г ередачу информации до устранения ошибки, возник-- шей в устройстве.

Буферное запоминающее устр ;йст1:н: по второму варианту рабоч ает cji .-,n ; щим образом (фиг,3).

Если нерзьш регистр накоггителя 2 свободен, то на выходе 28 HiiKo- нителя 2 имеется сигналj через ключевой элемент 7-/ постуг1;и. на вькод 29. В ответ на этот сигиа/ на вход 21 подаются очередные coooi; кия тек 1цего массива данньгх, -)тн сообщения через блок элементов 6-2 и коммутатор 1-1 ноступают в накоп таль 2, в котором продвигаются тактовыми 1-1мг;ульсами ТР1 к его вьпсоду,

Кроме того, сообп .сния с зьпсодов блоков элементов ЯЛК 6-2 постунают на вход нуль-органа 8, которьп- c TvtMHpyeT их.

Если на вход 2k пас-гупагт с:.игна то он через ключе150 -1 элемент -- „ регистр 5, блок элементов ИПИ б-- :; подастся на вход 28 накопителя 2, В ответ на этот сигнал тактовые сигналы Т И подают на выход наьгониг; ля 2 теку1цие. с ообщения, которые через к оммутатор 1-2, регист}- 5 блок элементов ИЛИ 6-1 носгупают на выход 24 устройства,

Кроме того, соо6и|;е 1и : с 22 коммутатора 1-2 на ;;п нрещенные входы узлов 9 г 2, а -гаг же на входы нуль-органа 8,, ко (-орь:м их вычич ает из имеющейся ,. м узла 1 1 5 KOTOpbrit иронеряет йк ;;; четность.

При обнгфунепии ошибки --к-тк на выход 39 узла 11 постунает нал ошибки, который нодзется т- 13 и 9. Узел 13 формирует байт состояния с признано. ошибки ч ти, а узел 9 формирует сиг-ца.:- выходах 35 и 34. Сигнал е: ньгхс 35 поступает на вход узла 1 v прещает контроль четгюсти, а i на вход ключевого элемента 7-2 которьш С11ой выход 2ii соединяв пььчодом 36. Поэтому- на выход 2

-)-:.- ;-ройств,-, сигналь; не п;-ст нлкп , а з:1;-;чи 1 не издаются сооби1,ения на 11Х(1Д 21. -г . е . прекращается нрием т : :-y;j;ero м,: ссива данных.

( А- Г на л с выхода 34 постунает на вход к;:ючево:-о элемента 7-1, кото- pi.iM -вой j- ,xo,;i 26 OTK- n oi igeT от вы :;::о;-;а 28 и ,иняет с выходом 27 . Прн -;том пре- чратяает ся передача со

е:;ий из регистра 5 и снимается с---7 нал с ег о 28. что запреща i:T передачу сообщений из накопителя 2, Сигнал с входа 26 в этом случае по; 1 -упает на вход 2/ узла 13, KOTO- PI, подав - на выход 25 байт состоя- п:- ; ; ,, оторьц ; через блок элементов i-i.llrl b-i ностунает на вькод 24, а 1эиз5 ак, байта г:остояния, кроме того 11ост-у1тает iia вход 25 узла 9, кото- pi- if: при этом сникает сигнал с выход 2-i-. Поэтому ключевой элемент 7 (-осдиняет свой нход 26 с выходом 28 :л счсрсдны;:: сообщения из накопителя 2 1:о:;-гупаю : на выход 24.

Иосле 11(-п:эедачи последнего сообще н;;.| гз накопителя 2 нуль-орган 1о ;миру( сигнал на выходе 42, :-П(.-тупаюший п узел 9, который при ; -ч-.-; рлзрепает вход 36 и формирует

-и-палы на И1:гхо1;ах 43 и 44,. поступа --) 1,не в формирователь 49. Формирова- -:п 49 в ответ лодает на выход

1 -гестов;,1е сообщения, которые :-;i(; блок элементов ИЛИ 6-2,, ком::; га-:-ор 1-1 постунают в накопитель

ган SsKOTopbtti снимает сиг- 2 узла 9, при этомформиру- на зыходс 30, с которог -I входы блока 3 и узла

г t

;ачи носледнего сигнал 1я считьтзания носледне госбщения из формирова пя 49 скглмается с входа 43 1-с1 1лп;рова-1-еля 49 и его выход 37 за- iivica-ается., Однопрсменно занрептается (), 36 и формируе-т-ся сигнал на f: n:jiic 45 узла 9; с которого постун : :П вход формирователя 49 и откры : ;-; ; его «г-п-ип, iO. Кроме тогО; от- ;пы.-;,1ется зход 22 узла 9, а также :-;.р -П1рустся сигна ; на вькоде 34, мс ;;туп;1Ю 1ий ключевой элемент 7-1,

cjpbin cot:. iHHHeT вход 26 с з-ьгходом 27

Сигнал с выхода 30 узла 9 через C.I ок элемен-гов ИЛИ 6-3 ностуггает на )кол, 28 на ;опителя 2. Поэтому тесто :i-::e с, с выхода накопителя 2

. IS

од;;

иг

П

зрсиае : II с D е

)В

9

через коммутатор 1-2 поступают на вход регистра 5, но не проходят на его выход 23, так как нет сигнала на его входе 28, а также поступают на вход 22 узла 12 и через вход 22 узла 9 подаются на выход 44. Поэтому тестовые сообщения с выхода 40 формирователя 49 поступают на вход узла 12 синфазно с аналогичными тестовыми сообщениями, поступающими на его. вход 22, где происходит их поразрядное сравнение и накопление результатов сравнения.

После выдачи и сравнения последнего тестового сообщения нуль-орган 8 формирует сигнал на выходе 42 с которого он поступает в узел 9, которьш формирует сигнал на выходе 41, поступающий в узел 12. При этом узел 12 выдает результаты сравнения на выход 31, с которого они поступают в блок 3, узел 9 и формирователь 13. Формирователь 13 формирует байт уточненного состояния с признаком номера неисправного канал (разряда) или с признаком только ошибки четности, если неисправного канала нет. Блок 3 формирует управляющие сигналы на выходе 33, поступающие на выход устройства и в коммутаторы 1-1 и 1-2, которые исключают неисправный канал и заменяют его резервным.

Сигналы с выхода 33 блока 3 поступают также на вход узла 9, который формирует сигнал на выходе 38, с которого он поступает на вход регистра 5 и обнуляет его, а также на вход формирователя 13, который выдает на выход 25 байт уточненного состояния, поступающий через блок элементов ИЛИ 6-1 на. выход 24, а его признак поступает и на вход 25 узла 9, который снимает сигнал с выхода 34. При этом ключевой элемент 7-1 соединяет свой вход 26 с выходом 28.

Кроме того, узел 9 снимает сигналы с выхода 35, при этом разрешается работа узла 11 контроля четности а также ключевой элемент 7-2 соединет свей выход 28 с выходом 29, что разрешает подачу сообщений прерванного массива на вход 21; с выхода 45, при этом формирователь 49 запрещает выход 40; с выхода 30, при этом запрещается работа блока 3 и узла 12, а также через блок элемен1180/20

тон или 6-3 снимается сигнал с входа 28 накопителя 2; а также с выходов 41 и 38.

Схема устройства возвращена в 5 исходное положение, при котором на входе 21 пр1 нлмается информация, накапливается в накопителе 2 и по запросам на входе 26 выдается на выход 24 аналох ично описанному. 10

Ф о р м у л а и 3 о б р е т е н и я

1. Буферное запоминающее устройство по авт.св. 1ОЬЗI635 о т л и -

f5 ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены буферный регистр, блок элементов ИЛИ и два ключепых элемента, пр5-ием выход второго

20 коммутатора подключен к первому входу буферного регистра, первый выход которого соединен с первым входом блока элементов ИЛИ, выход которого является информационным

5 выходом устройства , второй вход блока элементов ИЛИ соединен с вторым выходом блока контроля, пер- ВЫ1 выход первого ключевого элемента является управляющим входом устрой0 ства, первый выход соединен с третьим входом блока контроля, а второй выход соединен с вторым входом буферного регистра, второй выход которого подключен к управляющему входу

накопителя, управляющий вход которого подключен к первому входу второго ключевого элемента, выход которого является управляющим выходом устройства, третий вход буферного

Q регистра является синхронизирующим входом устройства, вторые входы первого и второго ключевых элементов соединены с третьим и четвертым выходами блока контроля соответствен5 но, четвертый вход которого соединен с выходом блока управления.

2. Устройство по п.1, отличающееся тем, что блок контроля содержит нуль-орган, узел управления, контроля четности, первый и второй узлы строчного контроля, узел сравнения и формирователь сигнала ошибки, причем первые входы первого узла строчного контро- ля и нуль-органа являются первым входом блока контроля, второй вход нуль-органа соединен с первым входом второго узла строчного контроля

0

21i

и вторым входом узла контролч четности и является иторьм входам блек с; контроля, выход узла контроля четности соединен с вторыми входами узла управления и формирсватгля сигнала опшбки, первый вход хоторогс является третьим входом блок.:; контроля, а выход подключен к первому входу узла управления и являг-тся в гс рьм выходом блока контроля, черЕь. й выход узла управления соедингп с третьим входом узла ср)авнеик.1 и является управляющих выходом блока контроля,, второй и первый входы узла сравнения соединены с выхода: ;, соответствующих узлов строчного контроля управления, вхо.пь которьгл и четвертый вход узла сравнения соединены с четвертьм выходом узла управления, пятый зь:код которого соединен с четвертым входом формирователя сигнала ошибки, вход которого и пятый вход узла управления соединень с вь-ходом узла сравнения и являются Г1ервым выходом блока контроля, тре7 :г й ихс Г; узла управления подклзочен к :;5ьгход нуль-органа, а четвертый вход и сннхровход узла управленяя язлякпс;- соответствеяно четвертым входом и синхровходом блока контроля, а второй и трети : ВЫХОД111 узла управ::с- ния являются соответственно третьим и четвертым выходами блока кэнтро ;::. третий выход узла управления с: псрвьм )ходом уз,1:а контроля чеп-ос т и. 1

3. Буферное запоми}.аюи;ее у строй-- ство по авт.сл, N- 1053163, о т ;: .- - чаю щ е е с я тем, что, с цель:: повышения па71.ежности устройс 1 Ег; ; :i3 ввсд.смы буфериьй регистр, бл( элементов ШТИ и два eBbix. элемента, причем выход второг о кoм Jyтaтopa соединен с первьа- .гкс:;i,(.: буфирно1ч) регистра,, первь:т iji ixoi:. кот(5рого соединен с пе.рвьж ,дся - первого блока элементов ИЛИ, ьтор:;; вход которого соедине - с вморым В1ЛХОДОМ б.лока KOHTPOJJH, а выход ляетсл ип(рормацио;шым выходом устройства, первый вход первшч; клк:- чевого э:1еме1гга является ynp.nviFidi ,иь входом устройства,, гтервьш вых.с;ц пегчюгс киочевого элемента соединен с T l). Ы1М нходоМ блока KOKTpi:.i:iH,, ; :(11);:м-ч | . мяход соединен с вторыту; .1: д л: Пх г чимюго регистра, -порой

-;:.1Х(;д KO iMjporo соедине/; с: первым ОХ.ОДО--1 З ретьего блока элементов ИЛИ, выход которого I1oдк.чFJчeн к управляю- ДС:му УХОДУ накопителя, управляющий jbix::vi которого соединен с первым Г;ходом вт(зрого ключевого элемента, которого является управ- л.г. выходом устройства, а в горой зых:з.;.1 подключен к пятому входу блока хомтроля, третий вход буферного ре- : исгра являе-гся синхронизирующим 1ХОДОМ устройства, четвертый вход эуферногг) рег истра соединен с шестым входом блока контроля, вторые входы lepijoro л второго ключевьп элементов соединены е третьи 5 и четверты;- - ых::да,ми блока контроля соответствен- :io, четвертый вход которого соединен С; вькодом блока управления, второй третьего блока элементов ИЛИ лоед.инен с управляющит- входом блока | .;о -:троля,, первый вход BTOpoi o блока ;;лементо;ч И.лИ является информацион- чым входом устройства, второй вход -(.единеиЧ с пятым выходом блока контроля, выход второг о блока элементов соедЮ В с входом первого комму- :;г: о; а и lU pBtjK - вхо.дом блока контро-

. стройство по п. J , о т л и ч а- ,0 ш, е е с я тем, что блок контроля :ч.- дс ржи г :;у::ь-ор1 дн, узел управле- г1ня , )ватель тестовых сообщений, узел кc;нтpoJ я четности, узел .равнения и формирователь сигнала )Ц Абки, jr :)H ;eM нервый вход нуль- орг зна является первым входом : -j:o::-.:a коитро-ля, второй вход соединен

исч тым входом узла управления и :п орыми входами узла контроля чет- I и 31 сравмекия и является и til блока контроля, выход 1 1 1 с ця четности соединен с ь и о тами узла управления и v t сиг;1ала ошибки , пер- Jорого является третьим

контроля, вьпкод узла

1 1 IT единен с третьим входом t J U чч сигнала ошибки и пятым

( f f контроля, формиро

1I Лс) ошибки соединен с

1 г 1М узла управления и явля

Е1м вьссодом блока контроля, 1 1 с I , узла управления явля- IV.JI 11 выходом блока контроля,

Р1t 1 ч J 1 узла управления соединен - С одом узла сравнения и т- 1 авляюпшм выходом блока

2312

контроля, третий выход узла управления соединен с первым входом узла контроля четности и является четвертым выходом блока контроля, первый и четвертый входы узла сравнения соединены соответственно с вторым выходом формирователя тестовых сообщений и четвертым выходом узла управления, шестой, седьмой и восьмой выходы которого соедине 1 1 с первым, втopы и третьим входами формирователя Tec,20 .29 ТИ

ISO/24

TOBi.ix сообщений, первый выход кото- рс.и о является пятым выходом блока кс1нтроля, синхровход, четвертый и входы узла управления

5 яиляются соответственно синхровхо- лом, четвертым и пятым входами блока контроля, пятый выход узла управления соединен.с четвертым входом формирователя сигнала ошибки и явля- 10 ется шестым выходом блока роля .

ВНИИПИ Заказ 64//5/ Тиргж 544 Подписное Филиал ППП Патент, г.Ужгород,ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Система асинхронной двусторонней передачи данных между передающей и приемной станциями | 1983 |

|

SU1521297A3 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| Устройство для приемопередачи информации с контролем ошибок | 1987 |

|

SU1425757A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для обмена информацией между эвм и магнитным накопителем | 1984 |

|

SU1218391A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в устройствах сопряжения вычислительных машин, в адаптивных системах измерений и вычислительных системах для сопряжения их с каналами передачи информации. Целью изобретения является повьпие- ние надежности устройства. Изобретение является усовершенствованием основного изобретения по авт.св. 1053163. Устройство по первому варианту содержит коммутаторы, накопитель, блок управления, блок контроля, буферный регистр, блоки элементов {.ШИ, ключевые элементы, нуль- орган, узел управления, узлы строчного контроля, узел контроля четности, узел сравнения, формирователь сигнала ошибки, триггеры, элементы ИЛИ, элементы И, элементы запрета, распределитель, группу анализаторов активности. Но второму варианту устройство содержит формирователь тестовых сообщений, элемент задержки. Устройство по первому варианту обладает простотой решения поставленной задачи и небольшой задержкой в передаче информад1п-, необход1-1Мой для проверки и корректировки каналов передачи данных .В то,же время он имеет недостаток, который заключается в том, что при передаче большого объема информации в устройстве не исключен единичный сбой, которьй приведет к корректировке каналов передачи данных, что может привести к преждевременному использование резервных каналов и остановке передачи данных. Для устранения этого недостатка предлагается второй вариант освобождения накопителя от информации, по которому через него пропускается группа тестовых сообщений. По результатам анализа принимается решение на корректировку каналов передачи данных. 2с. и 2 з.п. ф-лы. 4 ил. (О (Л

| Буферное запоминающее устройство | 1982 |

|

SU1053163A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-10—Подача