1

Изобретение относится к импульсной технике и может быть использовано для осуществления синхронизации с тактовой частотой случайных последовательностей импульсов произволь- ной длительности в устройствах преоб разования, обработки, накопления и передачи информации, для которых необходимо минимизировать вероятность потери полезной информации, заключен ,ной во входном сигнале.

Целью изобретения является повышение надежности функционирования путем исключения возможности пропус- ка входных импульсов при сохранении пропорциональности длительности выходных импульсов числу периодов следования тактовых импульсов , с которыми полностью или час- тично совпадает входной импульс.

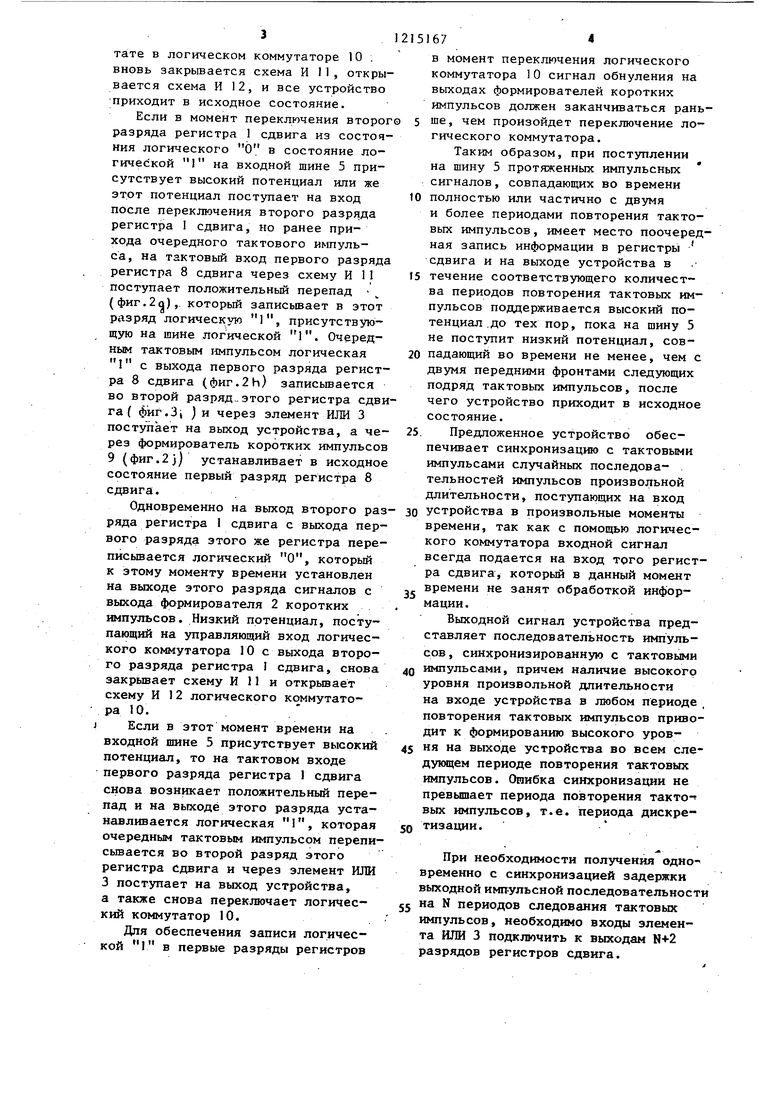

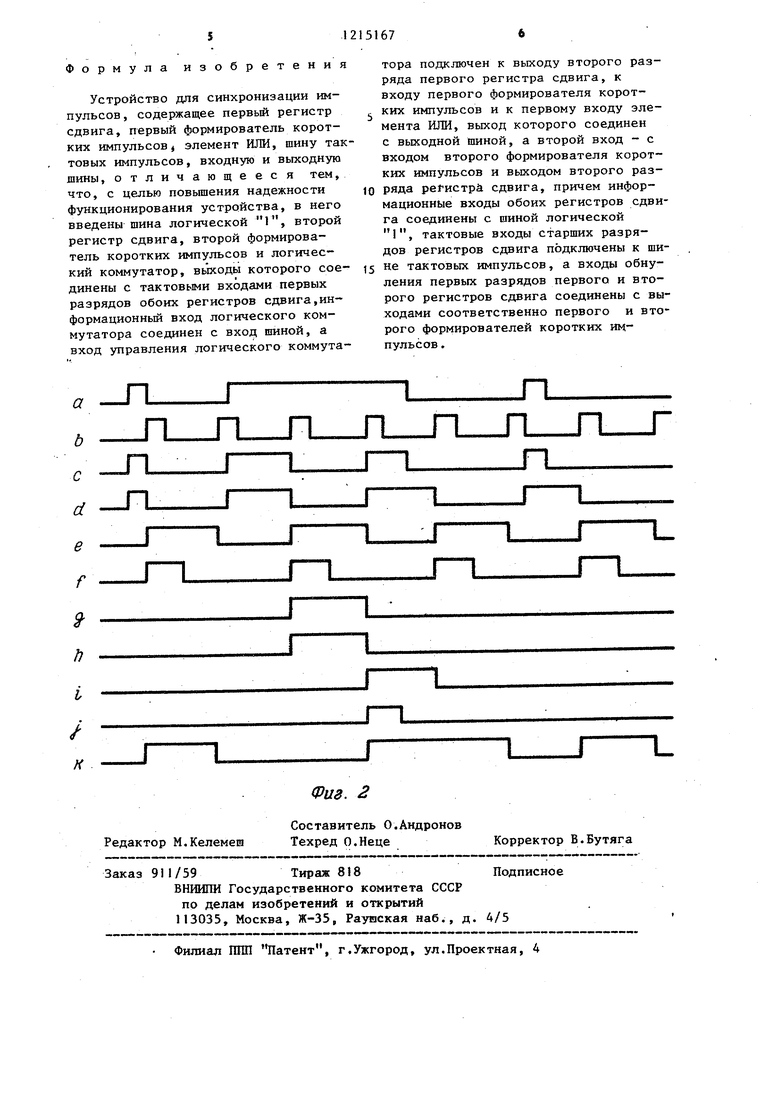

На фиг.1 приведена функциональная схема устройства для синхронизации импульсов; на фиг.

о

времен

ные диаграммы его работы.

Устройство для синхронизации импульсов содержит регистр 1 сдвига, формирователь 2 коротких импульсов, элемент ИЛИ 3, шину 4 тактовых импульсов, входную шину 5 и вы- ходную шину 6, шину 7 логической 1, второй регистр 8 сдвига, второй формирователь 9 коротких импульсов, логический коммутатор 10, вы- полненньм на логических эдементах 11 и 12 и коммутирующем элементе 13 Выходы коммутатора 10 соединены с тактовыми входами первых разрядов обоих регистров 1 и 8 сдвига, информационный вход соединен с входной ши ной, а вход управления подключен к выходу второго разряда первого регистра 1 сдвига, к входу первого формирователя 2 коротких импульсов и к первому входу элемента ИЛИ 3, выход которого соединен с выходной шиной 6, а второй вход - с входом второго формирователя 9 коротких импульсов и выходом второго разряда второго регистра 8 сдвига, причем ин- формационные входы обоих регистров 1 и 8 сдвига связаны с шиной 7 логической 1, тактовые входы всех разрядов репистров I и 8 сдвига, кроме первых, подключены к шине 4 тактовых импульсов, а входы обнуления первых разрядов первого и второго регист- ров 1 и 8 сдвига соединены с выхо

0

5 0

5

0 з 0 5 j

672

дами соответственно первого и второ-) го формирователей 2, 9 коротких импульсов .

Устройство работает следующим образом.

В исходном состоянии .при отсутствии входной информации (логический Q) на шине 5 устройства на выходах всех разрядов регистров сдвига сохраняется состояние логического О и данный потенциал через элемент ИЛИ 3 поступает на выходную шину 6 устройства. Низкий потенциал.с выхода второго разряда регистра 1 сдвига, поступающий на управляющий вход логического коммутатора, закрьшает схему И 11 и открьшает схему И 12, обеспечивая передачу сигнала с входной шины 5 (фиг.2 а) на тактовый вход первого разряда регистра сдвига (фиг.2с),

Передним фронтом гшпульса входной информации логическая 1, поступающая с шины 7 на информационный вход регистра 1 сдвига, записывается первый разряд, и на его выходе появляется логическая 1 (фиг. 2d).

Передним фронтом ближайшего тактового импульса (фиг., ь), поступшо- щего через шину 4 на тактовый вход второго разряда регистра 1 сдвига, логическая 1 с выхода первого разряда переписывается на выход второго разряда регистра сдвига (фиг.2в) и через элемент ИЛИ 3 поступает на , выходную шину 6 устройства (фиг.2|1). Одновременно высокий потенциал логической 1 с выхода второго разряда регистра 1 сдвига поступает на управляющий вход логического коммутатора 10, где открьшает схему И 11 и закрьшает схему И 12, а также через формирователь 2 коротких импульсов фиг.2 f сбрасьшает в исходное состояние первый разряд регистра Г сдвига (фиг.2 d).

Если в момент переключения логического коммутатора 10 и в последующее время, большее периода следования тактовых импульсов, на входной шине 5 устройства отсутствует высокий потенциал, то триггер первого разряда регистра 8 сдвига не изменяет своего состояния, а во второй разряд регистра 1 сдвига очередным тактовым импульсом записыйается логический О с выхода первого разряда этого же регистра, в резуль312151

тате в логическом коммутаторе 10 : вновь закрьгоается схема ИМ, открывается схема И 12, и все устройство приходит в исходное состояние.

Если Б момент переключения второго 5 разряда регистра 1 сдвига из состояния логического О в состояние логической 1 на входной шине 5 присутствует высокий потенциал или же этот потенциал поступает на вход Ю после переключения второго разряда регистра 1 сдвига, но ранее прихода очередного тактового импульса, на тактовый вход первого разряда регистра 8 сдвига через схему И 11 15 поступает положительньй перепад (фиг.2а),. который записьшает в этот разряд логическую 1, присутствующую на шине логической 1. Очередным тактовым гдапульсом логическая 20 1 с выхода первого разряда регистра 8 сдвига (фиг.2Ь} записьшается во второй разряд., этого регистра сдвига ( фиг.З; ) и через элемент ИЛИ 3 поступает на выход устройства, а че- 25. рез формирователь коротких импульсов 9 (фиг.2)) устанавливает в исходное состояние первый разряд регистра 8 сдвига.

Одновременно на выход второго раз- зо ряда регистра I сдвига с выхода первого разряда этого же регистра пере- письшается логический О, который к этому моменту времени установлен на выходе этого разряда сигналов с 35 выхода формирователя 2 коротких импульсов. Низкий потенциал, поступающий на управляющий вход логического коммутатора 10 с выхода второго разряда регистра I сдвига, снова 40 закрывает схему И П и открьшает схему И 12 логического коммутатора 10.

Если в этот момент времени на входной шине 5 присутствует высокий 5 потенциал, то на тактовом входе первого разряда регистра 1 сдвига снова возникает положительный перепад и на выходе этого разряда устанавливается логическая I , которая

очередным тактовым импульсом перепи- сьшается во второй разряд этого регистра Сдвига и через элемент ИЛИ 3 поступает на выход устройства, а также снова переключает логичес- кий коммутатор 10.

Для обеспечения записи логической 1 в первые разряды регистров

5 0 5.

о 5 0

5

0

5

67

в момент переключения логического коммутатора 10 сигнал обнуления на выходах формирователей коротких импульсов должен заканчиваться раньше, чем произойдет переключение логического коммутатора.

Таким образом, при поступлении на шину 5 протяженных импульсных сигналов, совпадающих во времени полностью или частично с двумя и более периодами повторения тактовых импульсов, имеет место поочередная запись информации в регистры сдвига и на выходе устройства в течение соответствующего количества периодов повторения тактовых импульсов поддерживается высокий потенциал .до тех пор, пока на шину 5 не поступит низкий потенциал, совпадающий во времени не менее, чем с двумя передними фронтами следующих подряд тактовых импульсов, после чего устройство приходит в исходное состояние.

Предложенное устройство обеспечивает синхронизацию с тактовыми импульсами случайных последовательностей импульсов произвольной длительности, поступающих на вход устройства в произвольные моменты времени, так как с помощью логического коммутатора входной сигнал всегда подается на вход того регистра сдвига, который в данный момент времени не занят обработкой информации .

Выходной сигнал устройства представляет последовательность импульсов , синхронизированную с тактовыми импульсами, причем наличие высокого уровня произвольной длительности на входе устройства в любом периоде , повторения тактовых импульсов приводит к формированию высокого уровня на выходе устройства во всем еле дукицем периоде повторения тактовых импульсов. Ошибка синхронизации не превышает периода повторения такго-г вых импульсов, т.е. периода дискретизации.

При необходимости получения одно временно с синхронизацией задержки выходной импульсной последовательности на N периодов следования тактовых импульсов, иеобходимо входы элемента ИЛИ 3 подключить к выходам N+2 разрядов регистров сдвига.

Формула изобретения

Устройство для синхронизации импульсов , содержащее первый регистр сдвига, первый формирователь коротких импульсов, элемент ИЛИ, шину тактовых импульсов, входную и выходную шины, отличающееся тем, что, с целью повышения надежности функционирования устройства, в него введены шина логической 1, второй регистр сдвига, второй формирователь коротких импульсов и логический коммутатор, выходы которого соединены с тактовыми входами первых разрядов обоих регистров сдвига,информационный вход логического коммутатора соединен с вход шиной, а вход управления логического коммутаа b с d е f

h

L

/ к

Заказ 911/59Тираж 818Подписное

ВНИИ1ВД Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

тора подключен к выходу второго разряда первого регистра сдвига, к входу первого формирователя корот- ких импульсов и к первому входу элемента ИЛИ, выход которого соединен с выходной шиной, а второй вход - с входом второго формирователя коротких импульсов и выходом второго разряда регистра сдвига, причем информационные входы обоих регистров сдвига соединены с шиной логической 1, тактовые входы старших разрядов регистров сдвига подключены к шине тактовых импульсов, а входы обнуления первых разрядов первого и второго регистров сдвига соединены с выходами соответственно первого и второго формирователей коротких импульсов ,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Генератор сочетаний | 1984 |

|

SU1166090A1 |

| Устройство для индикации экстремального значения последовательности цифровых величин | 1988 |

|

SU1529461A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Сенсорный переключатель | 1986 |

|

SU1425824A1 |

| Формирователь последовательностей импульсов | 1986 |

|

SU1441467A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Времяимпульсный компаратор | 1986 |

|

SU1403361A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

Изобретение относится к импуЛьс- ной технике и может использоваться в устройствах преобразования для синхронизации с тактовой частотой . случайных последовательностей импульсов произвольной длительности, в устройствах обработки, накопления и пе, редачи информации, когда необходимо уменьшить вероятность потери полезной информации, заключенной во входном сигнале. Цель изобретения - по- вышение надежности устройства - достигается исключением возможности пропуска входных импульсов при сохранении пропорциональности длительности выходных импульсов числу периодов следования .тактовых импульсов, с которыми полностью или частично совпадает входной импульс. Устройство содержит регистры 1 и 8 сдвига, формирователи 2 и 9 коротких импульсов, логический элемент ИЛИ 3 тактовых импульсов 4, входную 5, выходную 6, логический I 7, логический коммутатор 10, выполненный на. логических элементах 11 и 12 и коьму-. тирующем элементе 13. 2 ил. (Л

| Автоматическое устройство дляКОНТРОля НАпРяжЕНия пРи РАзРядЕ АККуМу-ляТОРОВ | 1979 |

|

SU853716A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство задержки импульсов | 1979 |

|

SU864527A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-28—Публикация

1984-06-22—Подача