4 4

li О)

Изобретение относится к импульсной технике и может быть использовайо в устройствах для выработки периодических последовательностей импульсов для управления микросхемами с зарядовой связью.

Цель изобретения - повьпцение помехоустойчивости и расширение функциональных возможностей формировате- ля последовательностей импульсов за счет кодового управления количеством импульсов, формируемых в пачках.

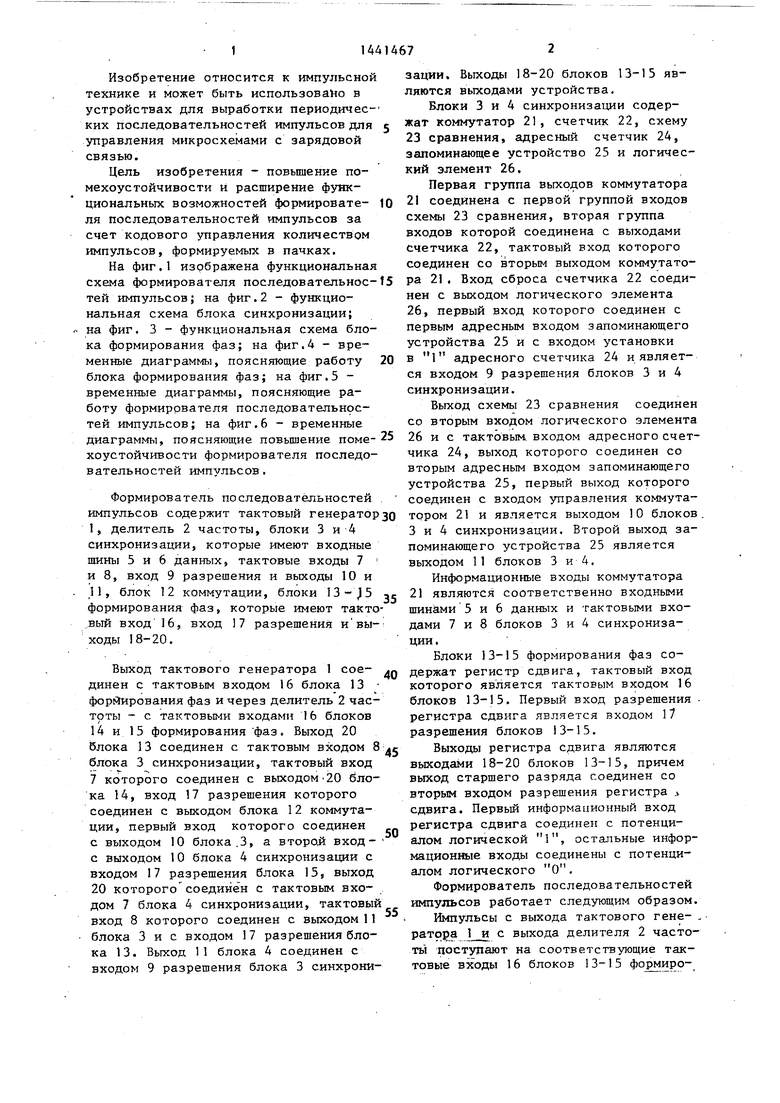

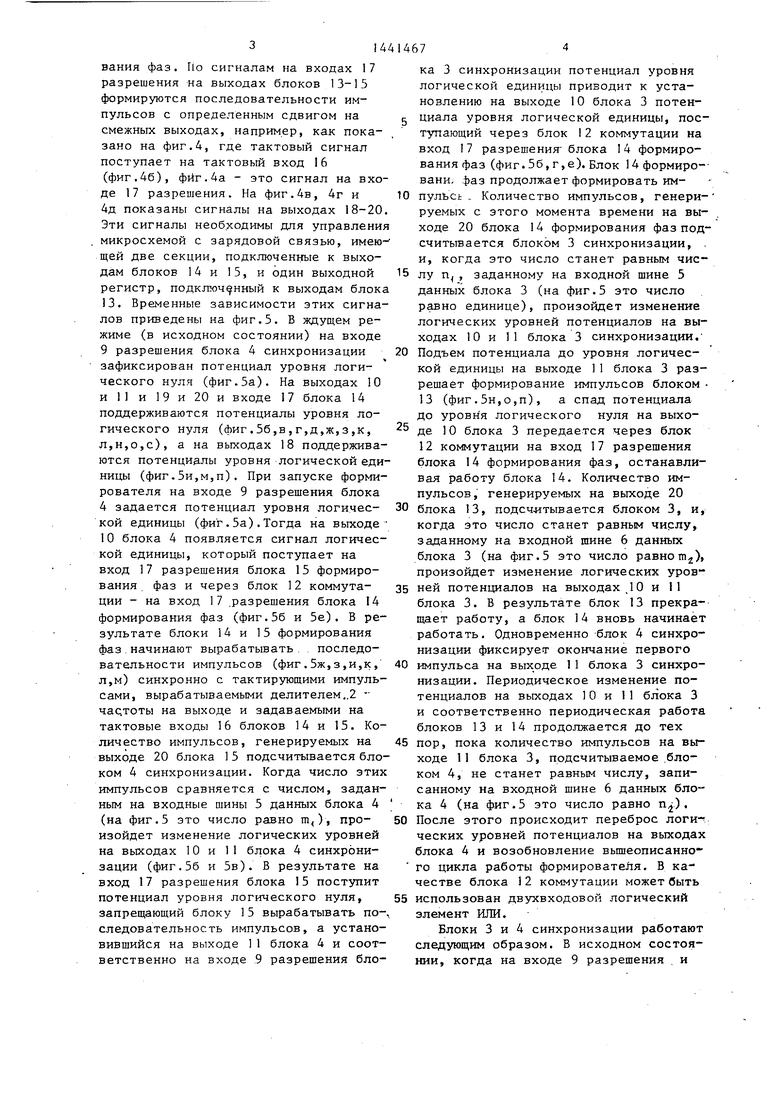

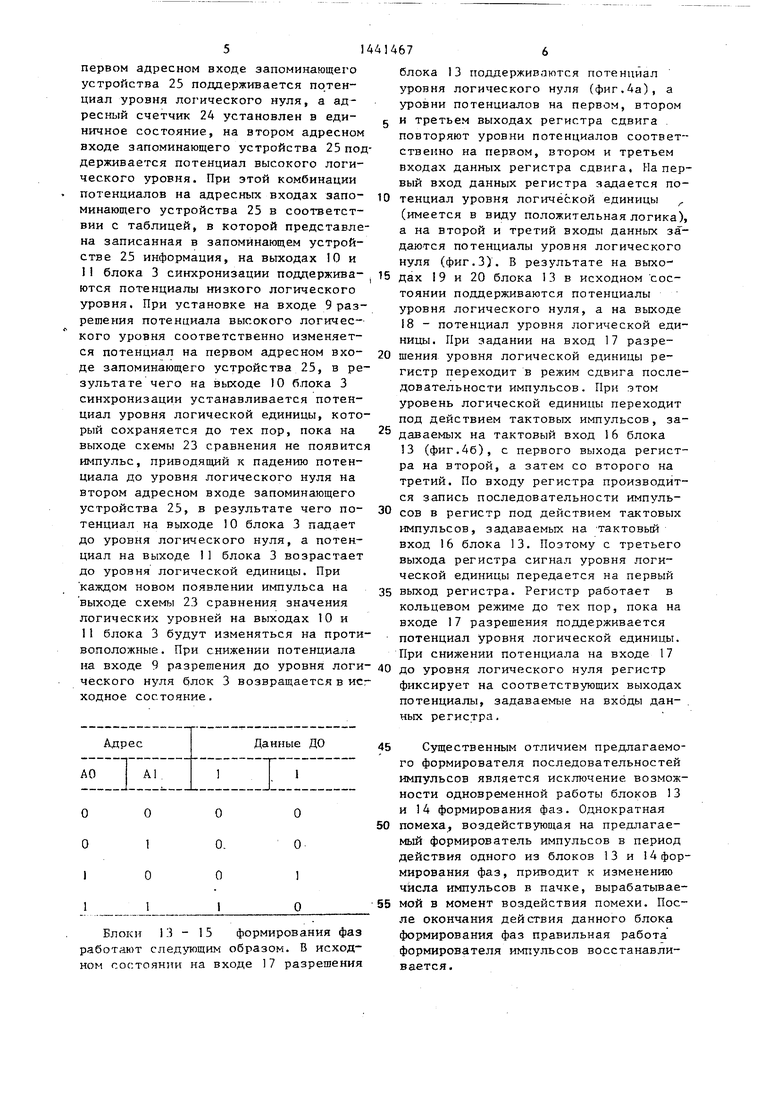

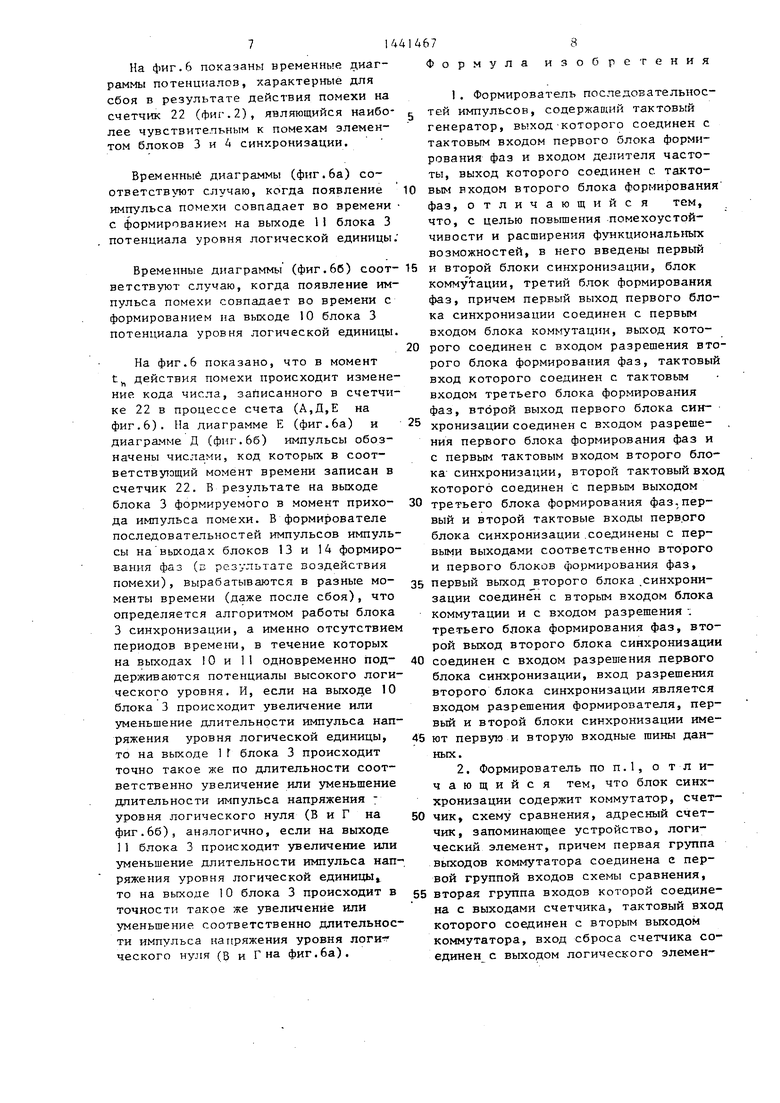

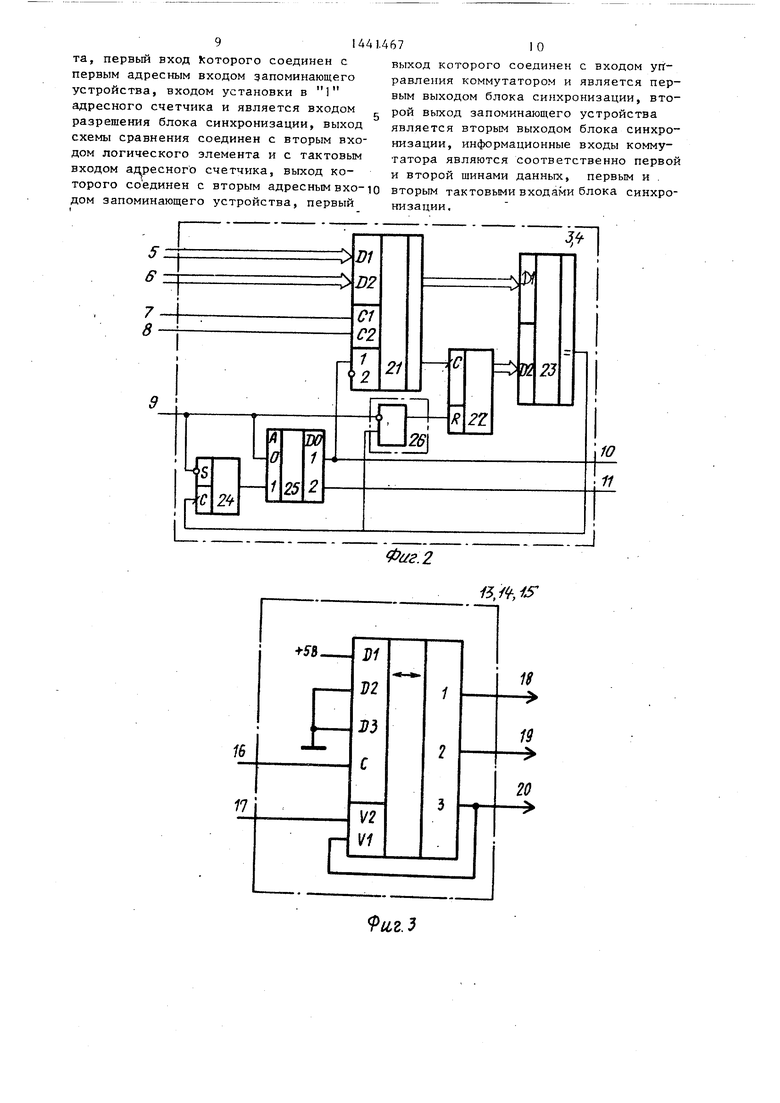

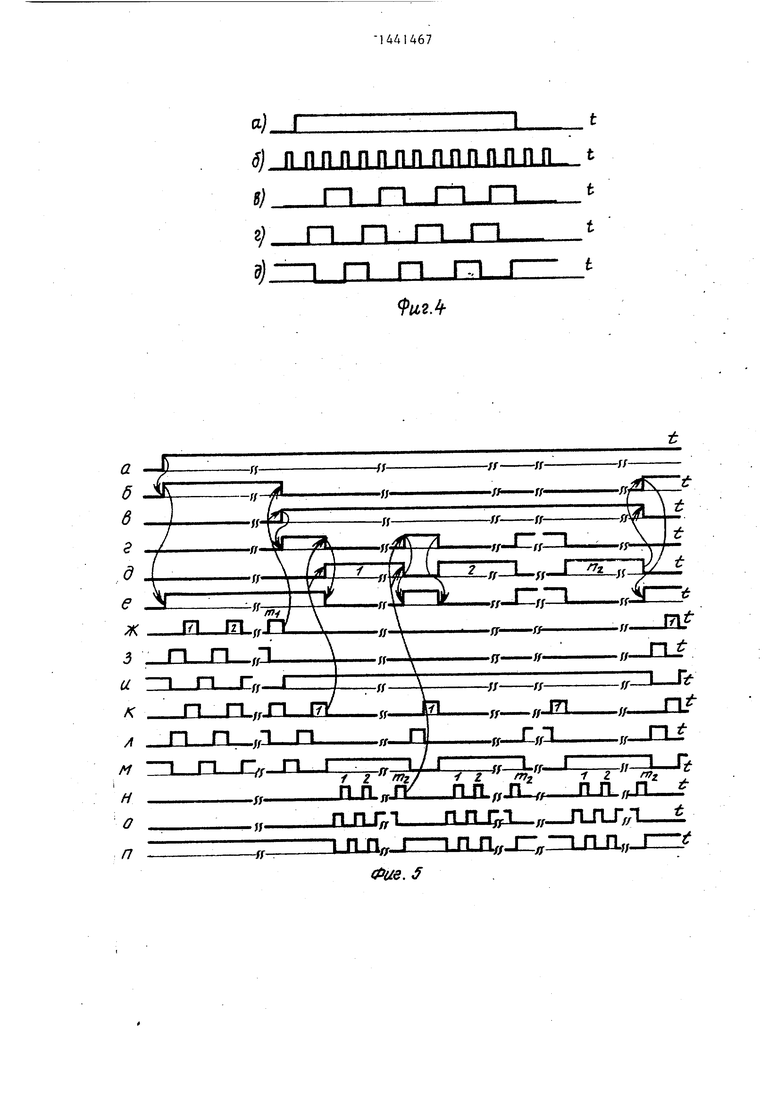

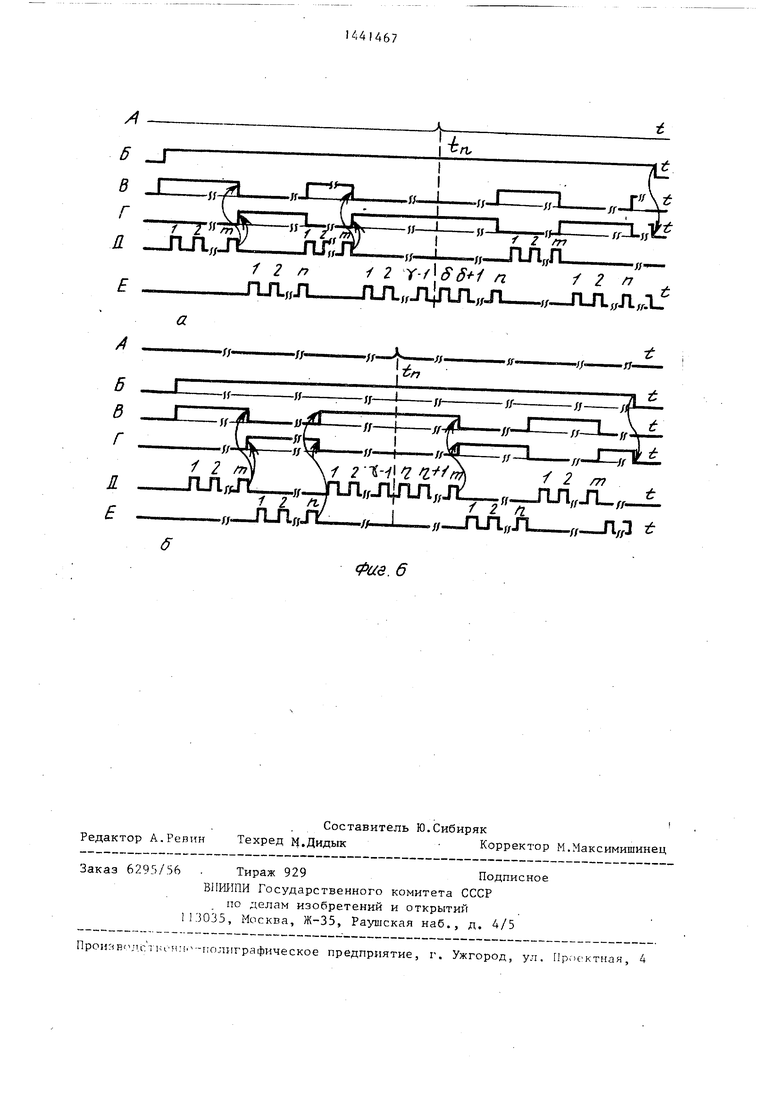

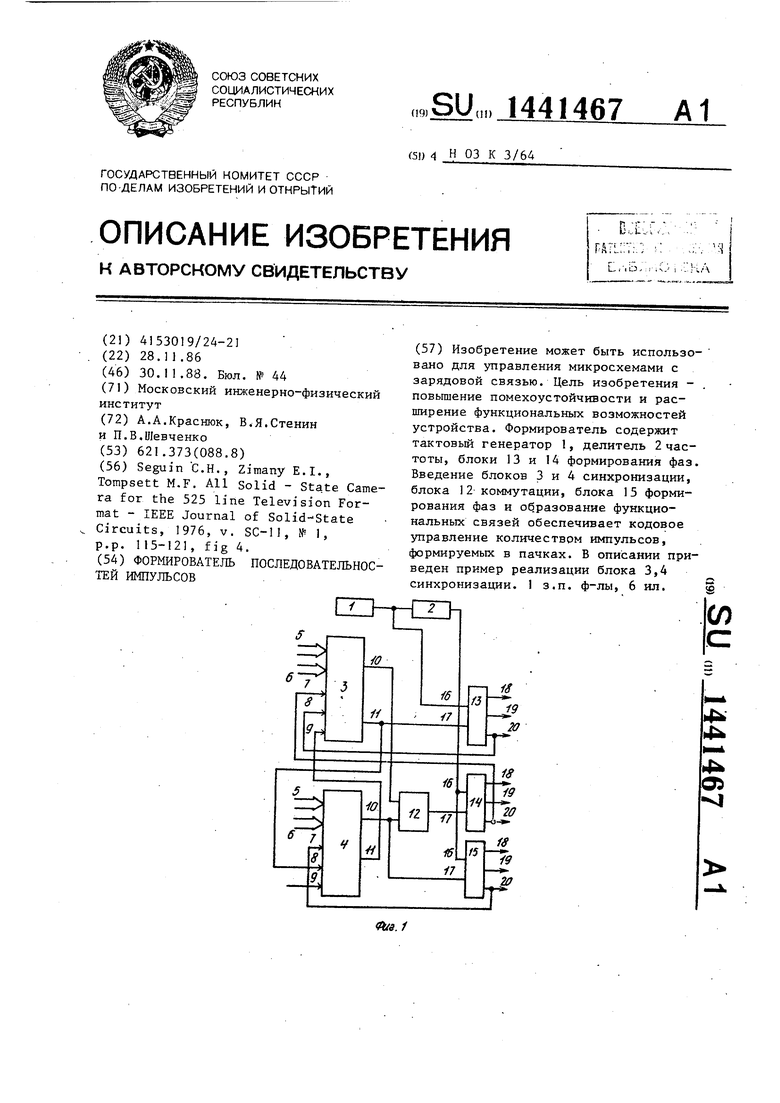

На фиг.1 изображена функциональная схема формирователя последовательноетей импульсов; на фиг.2 - функциональная схема блока синхронизации; на фиг. 3 - функциональная схема блока формирования фаз; на фиг.4 - временные диaгpaм ы, поясняющие работу блока формирования фаз; на фиг.5 - временные диаграммы, поясняющие работу формирователя последовательностей импульсов; на фиг.6 - временные диаграммы, поясняющие повышение помехоустойчивости формирователя последовательностей импульсов.

Формирователь последовательностей импульсов содержит тактовый генератор 1, делитель 2 частоты, блоки 3 и 4 синхронизации, которые имеют входные шины 5 и 6 данных, тактовые входы 7 и 8, вход 9 разрешения и выходы 10 и ,11, блок 12 коммутации, блоки 13--)5 формирования фаз, которые имеют тактовый вход 16, вход 17 разрешения и выходы 18-20.

Выход тактового генератора 1 сое

динен с тактовым входом 16 блока 13 формирования фаз и через делитель 2 частоты - с тактовыми входами 16 блоков 14 и 15 формирования фаз. Выход 20 блока 13 соединен с тактовым входом 8 блока 3 синхронизации, тактовый вход 7 которого соединен с выходом 20 блока 14, вход 17 разрешения которого соединен с выходом блока 12 коммутации, первый вход которого соединен с выходом 10 блока.3, а второй вход- с выходом 10 блока 4 синхронизации с входом 17 разрешения блока 15, выход 20 которого соединен с тактовым входом 7 блока 4 синхронизации, тактовый вход 8 которого соединен с выходом 11 блока 3 и с входом 17 разрешения блока 13. Выход П блока 4 соединен с входом 9 разрешения блока 3 синхрони

о с

0

с

0

5

зации. Выходы 18-20 блоков 13-15 являются выходами устройства.

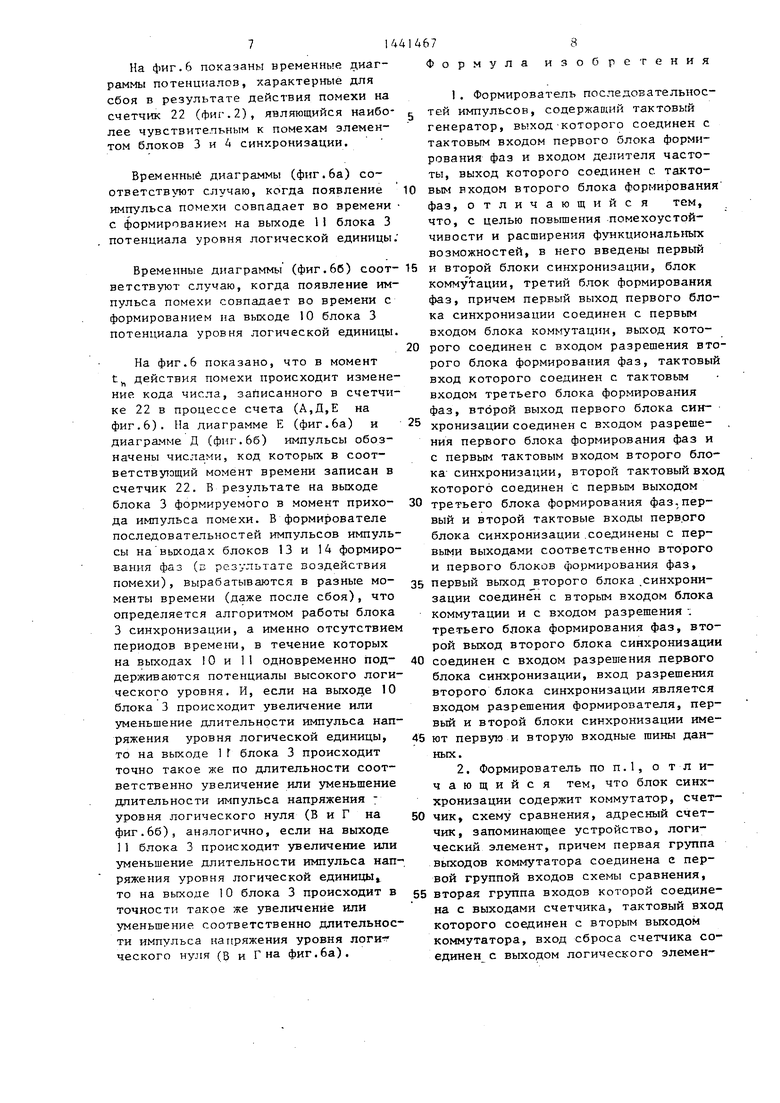

Блоки 3 и 4 синхронизации содержат коммутатор 21, счетчик 22, схему 23 сравнения, адресный счетчик 24, запоминающее устройство 25 и логический элемент 26.

Первая группа выходов коммутатора 21 соединена с первой группой входов схемы 23 сравнения, вторая группа входов которой соединена с выходами счетчика 22, тактовый вход которого соединен со вторым выходом коммутатора 21. Вход сброса счетчика 22 соединен с выходом логического элемента 26, первый вход которого соединен с первым адресным входом запоминающего устройства 25 и с входом установки в 1 адресного счетчика 24 и является входом 9 разрешения блоков 3 и 4 синхронизации.

Выход схемы 23 сравнения соединен со вторым входом логического элемента 26 и с тактовый входом адресного счетчика 24, выход которого соединен со вторым адресным входом запоминающего устройства 25, первый выход которого соединен с входом управления коммутатором 21 и является выходом 10 блоков. 3 и 4 синхронизации. Второй выход запоминающего устройства 25 является выходом 11 блоков 3 и 4,

Информационные входы коммутатора 21 являются соответственно входными шинами 5 и 6 данных и тактовыми входами 7 и 8 блоков 3 и 4 синхронизации ,

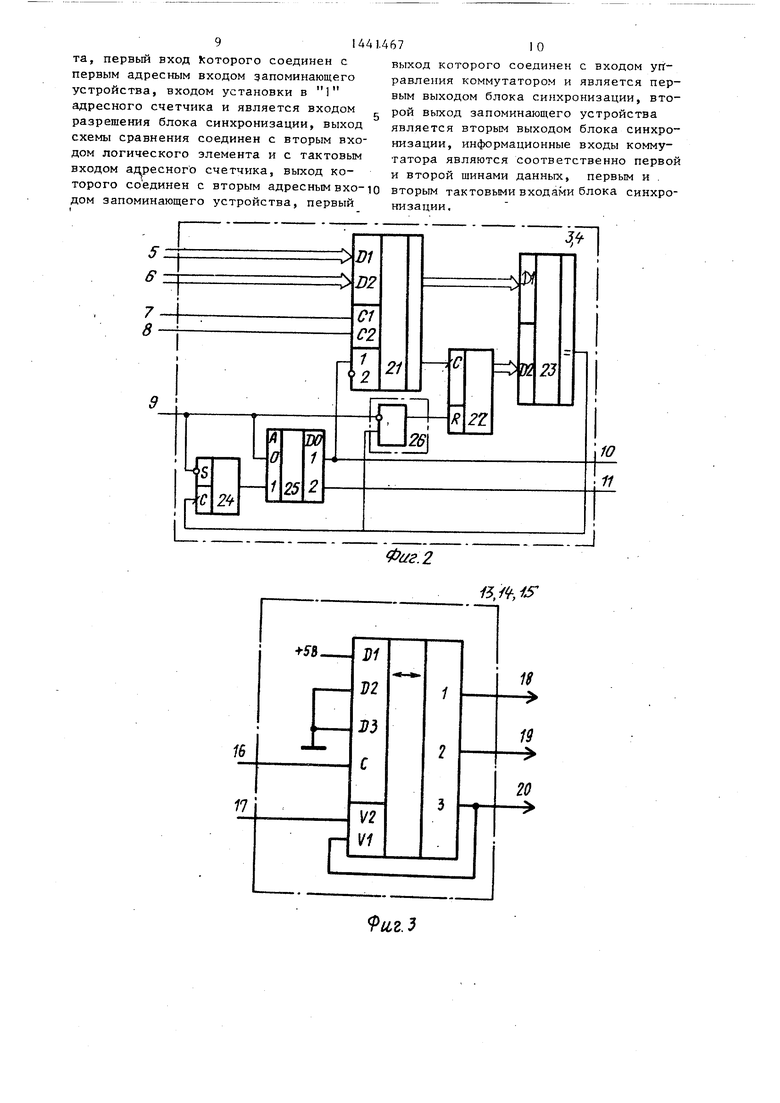

Блоки 13-15 формирования фаз содержат регистр сдвига, тактовый вход которого является тактовым входом 16 блоков 13-15. Первый вход разрешения - регистра сдвига является входом 17 разрешения блоков 13-15.

Выходы регистра сдвига являются выходами 18-20 блоков 13-15, причем выход старшего разряда соединен со вторым входом разрешения регистра . сдвига. Первый информационный вход регистра сдвига соединен с потенциалом логической 1, остальные информационные входы соединены с потенциалом логического О.

Формирователь последовательностей импульсов работает следующим образом.

Шпульсы с выхода тактового гене- . ратора 1 и с выхода делителя 2 часто- Tbi поступают на соответствующие тактовые входы 16 блоков 13-15 формиро314414674

вания фаз. По сигналам на входах 17 ка 3 синхронизации потенциал уровня разрешения на выходах блоков 13-15 логической единицы приводит к уста- формируются последовательности им- новлению на выходе 10 блока 3 потен- пульсов с определенным сдвигом на циала уровня логической единицы, пос- смежньгх выходах, например, как пока- , тупающий через блок 12 коммутации на зано на фиг.4, где тактовый сигнал вход 17 разрешения блока 14 формиро- поступает на тактовый вход 16вания фаз (фиг.56, г,е). Блок 14 формиро-(фиг.46), фйг.4а - это сигнал на вхо- ванн, фаз продолжает формировать им- де 17 разрешения. На фиг.4в, 4г и 10 пульсь „ Количество импульсов, генери- 4д показаны сигналы на выходах 18-20. руемых с этого момента времени на вы- Эти сигналы необходимы для управления ходе 20 блока 14 формирования фаз под- . микросхемой с зарядовой связью, имею- считьтается блоком 3 синхронизации, . щей две секции, подключенные к выхо- и, когда это число станет равньгм чис- дам блоков 14 и 15, и один выходной 15 лу п , заданному на входной шине 5 регистр, подключенный к выходам блока данных блока 3 (на фиг.5 это число 13. Временные зависимости этих сигна- равно единице), произойдет изменение лов приведены на фиг.5. В ждущем ре- логических уровней потенциалов на выжиме (в исходном состоянии) на входе ходах 10 и 11 блока 3 синхронизации,

9разрешения блока 4 синхронизации 20 Подъем потенциала до уровня логичес- зафиксирован потенциал уровня логи- кой единицы на выходе 11 блока 3 раз- ческого нуля (фиг.5а). На выходах 10 решает формирование импульсов блоком- и 11 и 19 и 20 и входе 17 блока 14 13 (фиг.5н,о,п), а спад потенциала поддерживаются потенциалы уровня ло- до уровн я логического нуля на выхо- гического нуля (фиг.56,в,г,д,ж,з,к, 25 де Q блока 3 передается через блок л,н,о,с), а на выходах 18 поддержива- 12 коммутации на вход 17 разрешения ются потенциалы уровня логической еди- блока 14 формирования фаз, останавли- ницы (фиг.5и,м,п). При запуске форми- вал работу блока 14. Количество им- рователя на входе 9 разрешения блока пульсов, генерируемых на выходе 20

4 задается потенциал уровня логичес- 30 блока 13, подсчитывается блоком 3, и, кой единицы (фиг.5а).Тогда на выходе когда это число станет равным числу,

10блока 4 появляется сигнал логичес- заданному на входной шине 6 данных кой единицы, который поступает на блока 3 (на фиг.5 это число равно га). вход 17 разрешения блока 15 формиро- произойдет изменение логических уров- вания. фаз и через блок 12 коммута- 35 ней потенциалов на выходах.10 и 11 ции - на вход 17 .разрешения блока 14 блока 3. В результате блок 13 прекра- формирования фаз (фиг.56 и 5е). В ре- щает работу, а блок 14 вновь начинает зультате блоки 14 и 15 формирования работать. Одновременно блок 4 синхро- фаз начинают вырабатывать последе- низации фиксирует окончание первого вательности импульсов (фиг.5ж,з,и,к, 40 импульса на выходе 11 блока 3 синхро- л,м) синхронно с тактирующими импуль- низации. Периодическое изменение по- сами, вырабатываемыми делителем..2 - тенциалов на выходах 10 и 11 блока 3 частоты на выходе и задаваемыми на и соответственно периодическая работа тактовые входы 16 блоков 14 и 15. Ко- блоков 13 и 14 продолжается до тех личество импульсов, генерируемых на 45 пор, пока количество импульсов на вы- выходе 20 блока 15 подсчитывается бло- ходе 11 блока 3, подсчитываемое .блоком 4 синхронизации. Когда число этих ком 4, не станет равным числу, запи- импульсов сравняется с числом, задан- санному на входной шине 6 данных бло- ным на входные шины 5 данных блока 4 | ка 4 (на фиг.5 это число равно п.). (на фиг.5 это число равно т,), про- 50 После этого происходит переброс логи-г изойдет изменение логических уровней ческих уровней потенциалов на выходах на выходах 10 и 11 блока 4 синхрони- блока 4 и возобновление вьш1еописанно зации (фиг. 56 и 5в). В результате на го цикла работы формирователя. В ка- вход 17 разрешения блока 15 пост упит честве блока 12 коммутации может быть потенциал уровня логического нуля, 55 использован двухвходовой логический запрещающий блоку 15 вырабатывать по-, элемент ИЛИ.

следовательность импульсов, а устано- Блоки 3 и 4 синхронизации работают вившийся на выходе 11 блока 4 и соот- следующим образом. В исходном состоя- ветственно на входе 9 разрешения бло- нии, когда на входе 9 разрешения и

первом адресном входе запоминающего устройства 25 поддерживается потенциал уровня логического нуля, а адресный счетчик 24 установлен в единичное состояние, на втором адресном входе запоминающего устройства 25 поддерживается потенциал высокого логического уровня. При этой комбинации Потенциалов на адресных входах запоминающего устройства 25 в соответствии с таблицей, в которой представлена записанная в запоминающем устройстве 25 информация, на выходах 10 и 11 блока 3 синхронизации поддерживаются потенциалы низкого логического уровня. При установке на входе 9 разрешения потенциала высокого логического уровня соответственно изменяется потенциал на первом адресном входе запоминающего устройства 25, в результате чего на выходе 10 блока 3 синхронизации устанавливается потенциал уровня логической единицы, который сохраняется до тех пор, пока на выходе схемы 23 сравнения не появитс импульс, приводящий к падению потенциала до уровня логического нуля на втором адресном входе запоминающего устройства 25, в результате чего потенциал на выходе 10 блока 3 падает до уровня логического нуля, а потенциал на выходе 11 блока 3 возрастает до уровня логической единицы. При каждом новом появлении импульса на выходе схемы 23 сравнения значения логических уровней на выходах 10 и 11 блока 3 будут изменяться на противоположные . При снижении потенциала

35 выход регистра. Регистр работает в кольцевом режиме до тех пор, пока на входе 17 разрешения поддерживается потенциал уровня логической единицы. При снижении потенциала на входе 17

ходное состояние,

на входе 9 разрешения до уровня логи- 40 до уровня логического нуля регистр ческого нуля блок 3 возвращается в ис- фиксирует на соответствующих выходах

потенциалы, задаваемые на входы дан- .

ньЕХ регистра,

45 Существенным отличием предлагаемого формирователя последовательностей импульсов является исключение возможности одновременной работы блоков 13 и 14 формирования фаз. Однократная 50 помеха, воздействующая на предлагаемый формирователь импульсов в период действия одного из блоков 13 и 4 формирования фаз, приводит к изменению числа импульсов в пачке, вырабатывае- 55 мой в момент воздействия помехи. После окончания действия данного блока формирования фаз правильная работа формирователя импульсов восстанавливается.

0.

1

О

Блоки

15 формирования фаз

работают следующим образом. В исходном состоянии на входе 17 разрешения

блока 13 поддерживаются потенциал уровня логического нуля (фиг.4а), а уровни потенциалов на первом, втором и третьем выходах регистра сдвига повторяют уровни потенциалов соответственно на первом, втором и третьем входах данных регистра сдвига. На первый вход данных регистра задается потенциал уровня логической единицы (имеется в виду положительная логика), а на второй и третий входы данных задаются потенциалы уровня логического нуля (фиг.З). В результате на выходах I9 и 20 блока 13 в исходном состоянии поддерживаются потенциалы уровня логического нуля, а на выходе 18 - потенциал уровня логической единицы. При задании на вход 17 разрешения уровня логической единицы регистр переходит в режим сдвига последовательности импульсов. При этом уровень логической единицы переходит под действием тактовых импульсов, задаваемых на тактовый вход 16 блока 13 (фиг.4б), с первого выхода регистра на второй, а затем со второго на третий. По входу регистра производится запись последовательности импульсов в регистр под действием тактовых импульсов, задаваемых на тактовый вход 16 блока 13. Поэтому с третьего выхода регистра сигнал уровня логической единицы передается на первый

выход регистра. Регистр работает в кольцевом режиме до тех пор, пока на входе 17 разрешения поддерживается потенциал уровня логической единицы. При снижении потенциала на входе 17

до уровня логического нуля регистр фиксирует на соответствующих выходах

7

На фиг.6 показаны временные диаграммы потенциалов, характерные для сбоя в результате действия помехи на счетчик 22 (фиг.2), являющийся наибо- лее чувствительным к помехам элементом блоков 3 и 4 синхронизации.

44U67 Ф о

рмула изобретения

). Формирователь последовательностей импульсов, содержапшй тактовый генератор, выход которого соединен с тактовым входом первого блока формирования фаз и входом делителя частоты, выход которого соединен с такто- 10 вым входом второго блока формирования фаз, отличающийся тем, что, с целью повышения помехоустойчивости и расширения функциональных возможностей, в него введены первый Временные диаграммы (фиг.бб) соот- 15 и второй блоки синхронизации, блок

Временные диаграммы (фиг.ба) со ответств 1от случаю, когда появление импульса помехи совпадает во времени с формированием на выходе 11 блока 3 потенциала уровня логической единицы

44U67 Ф о

рмула изобретения

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

| Устройство для контроля монотонно изменяющегося кода | 1988 |

|

SU1658190A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для декодирования данных | 1988 |

|

SU1629912A1 |

Изобретение может быть использовано для управления микросхемами с зарядовой связью. Цель изобретения - . повышение помехоустойчивости и расширение функциональных возможностей устройства. Формирователь содержит тактовый генератор 1, делитель 2 частоты, блоки 13 и 14 формирования фаз. Введение блоков 3 и 4 синхронизации, блока 12 коммутации, блока 15 формирования фаз и образование функциональных связей обеспечивает кодовое управление количеством импульсов, формируемых в пачках. В описании приведен пример реализации блока 3,4 синхронизации. 1 з.п. ф-лы, 6 ил.

ветствуют случаю, когда появление импульса помехи совпадает во времени с формированием на выходе 10 блока 3 потенциала уровня логической единицы.

На фиг.6 показано, что в момент t действия помехи происходит изменение кода числа, записанного в счетчике 22 в процессе счета (А,Д,Е на фиг.6). На диаграмме Е (фиг.ба) и диаграмме Д (фиг.бб) импульсы обозначены числами, код которых в соответствующий момент времени записан в счетчик 22. В результате на выходе блока 3 формируемого в момент прихода импульса помехи. В формирователе последовательностей импульсов импульсы на выходах блоков 13 и 14 формирования фаз (Б результате воздействия помехи), вырабатываются в разные моменты времени (даже после сбоя), что определяется алгоритмом работы блока 3 синхронизации, а именно отсутствием периодов времени, в течение которых на выходах О и 11 одновременно поддерживаются потенциалы высокого логического уровня. И, если на выходе 10 блока 3 происходит увеличение или уменьшение длительности импульса напряжения уровня логической единицы, то на выходе 1 Г блока 3 происходит точно такое же по длительности соответственно увеличение или уменьшение длительности импульса напряжения : уровня логического нуля (В и Г на фиг.бб), аналогично, если на выходе 11 блока 3 происходит увеличение или уменьшение длительности импульса напряжения уровня логической единицы то на выходе 10 блока 3 происходит в точности такое же увеличение или уменьшение соответственно длительности импульса напряжения уровня логи- ческого нуля (В и Г на фиг.ба).

0

5

0

коммутации, третий блок формирования фаз, причем первый выход первого блока синхронизации соединен с первым входом блока коммутации, выход которого соединен с входом разрешения второго блока формирования фаз, тактовый вход которого соединен с тактовым входом третьего блока формирования фаз, второй выход первого блока синхронизации соединен с входом разрешения первого блока формирования фаз и с первым тактовым входом второго блока синхронизации, второй тактовый вход которого соединен с первым выходом третьего блока формирования фаз,первый и второй тактовые входы первого блока синхронизации .соединены с пер- вьми выходами соответственно второго и первого блоков формирования фаз,

5 первый выход второго блока .синхронизации соединен с вторым входом блока коммутации и с входом разрешения . третьего блока формирования фаз, второй выход второго блока синхронизации

0 соединен с входом разрешения первого блока синхронизации, вход разрешения второго блока синхронизации является входом разрешения формирователя, первый и второй блоки синхронизации име5 ют первую и вторую входные шины данных.

5 вторая группа входов которой соединена с выходами счетчика, тактовый вход которого соединен с вторым выходом коммутатора, вход сброса счетчика соединен с выходом логического элеменJ.

nil

Фаг. 2

/5,/,/

аг.

JUL;;Jli

;rJZ 3- jTW/Afl --

-jirr;

i 2 ЛЛяЛ.

f// ЛЛ,гЛ

Редактор А.Ревин Техред .Дидык

Заказ 6295/56 . Тираж 929Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытиГг 113035, Москва, Ж-35, Раушская наб., д. 4/5

I П,

./;J

--

f// п

ЛЛ,гЛ|ПЛя.

1

/ / 7

,

/ f /7

;-лл,л,..г:

,ПяТ г

/. 6

Составитель Ю.Сибиряк

Корректор М.Максимишинец

| Seguin С.Н., Zimany E.I., Tompsett M.F | |||

| Телескоп | 1920 |

|

SU525A1 |

| SC-II, № 1, p.p | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

Авторы

Даты

1988-11-30—Публикация

1986-11-28—Подача