I Изобретение.относится к вычислительной технике и контрольно-измерительной технике и может быть использовано для проверки работоспособности и контроля логических бло- ков, в частности для контроля логических блоков в стандарте ЭВМ Электроника-60 и СМ-3.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля двух логических блоков с различной структурной организацией.

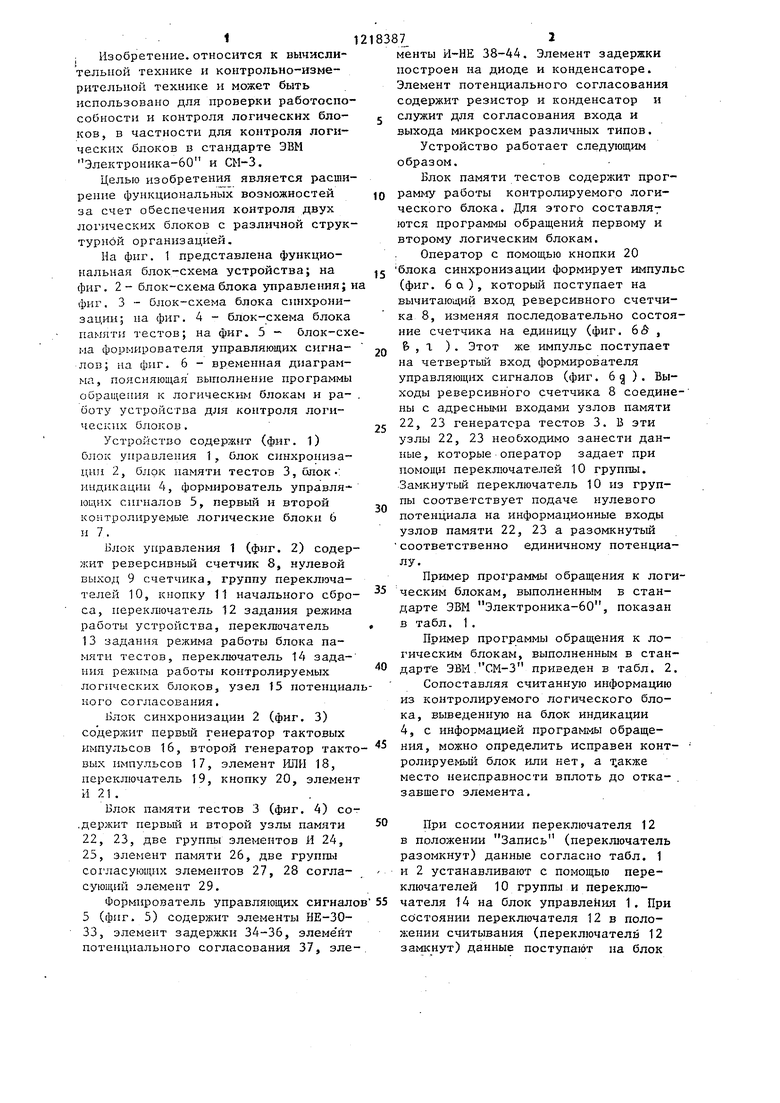

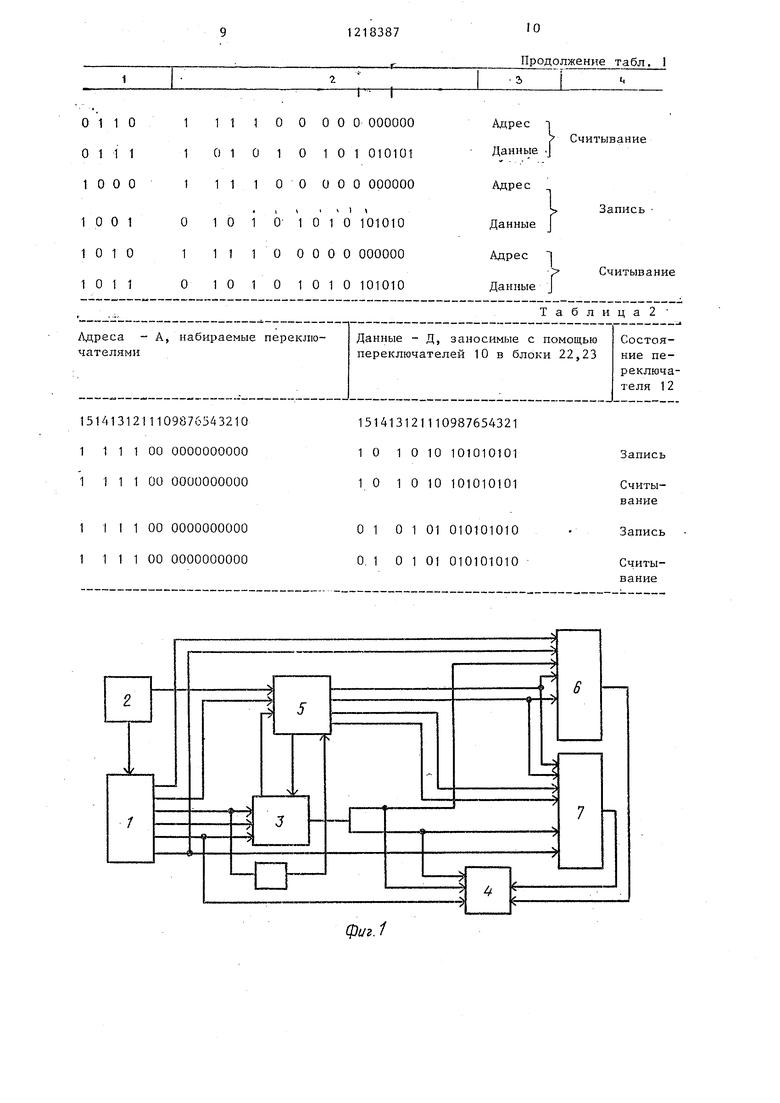

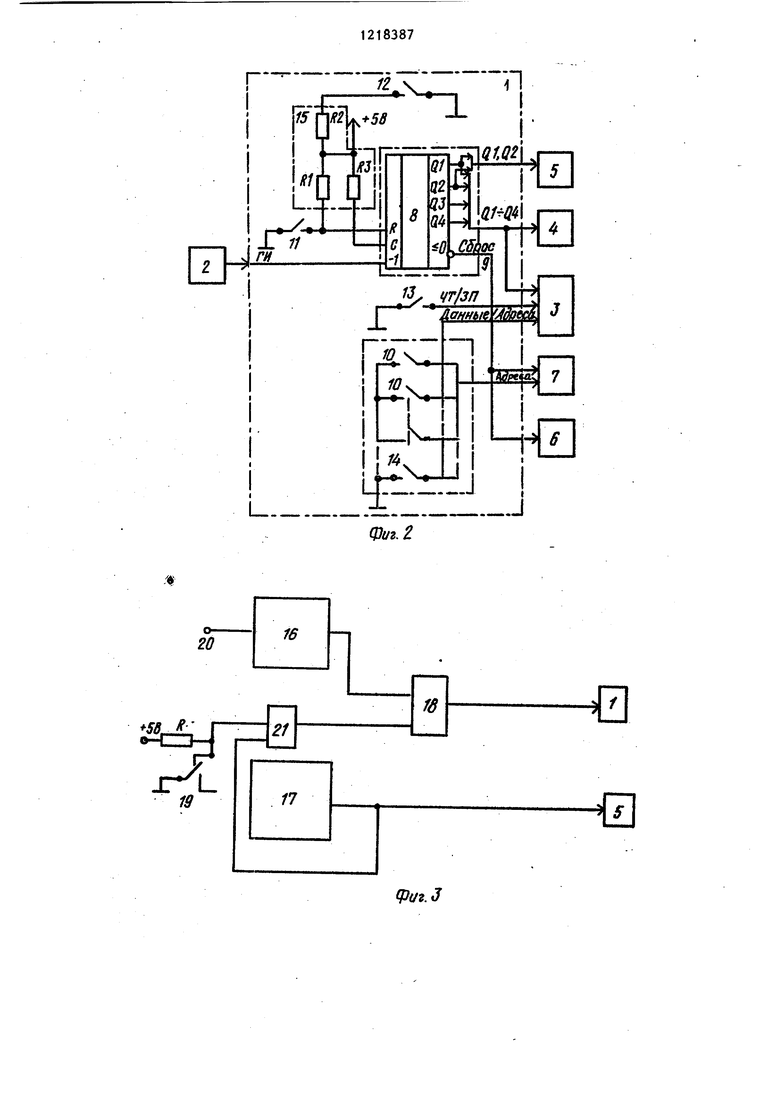

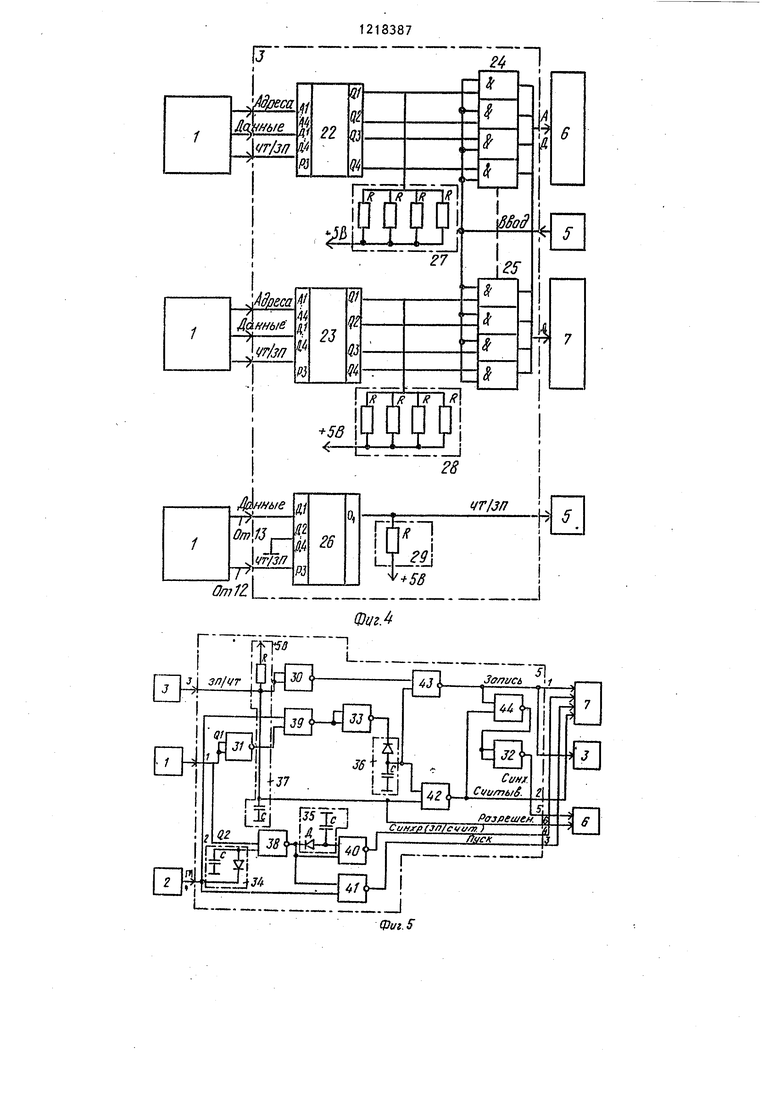

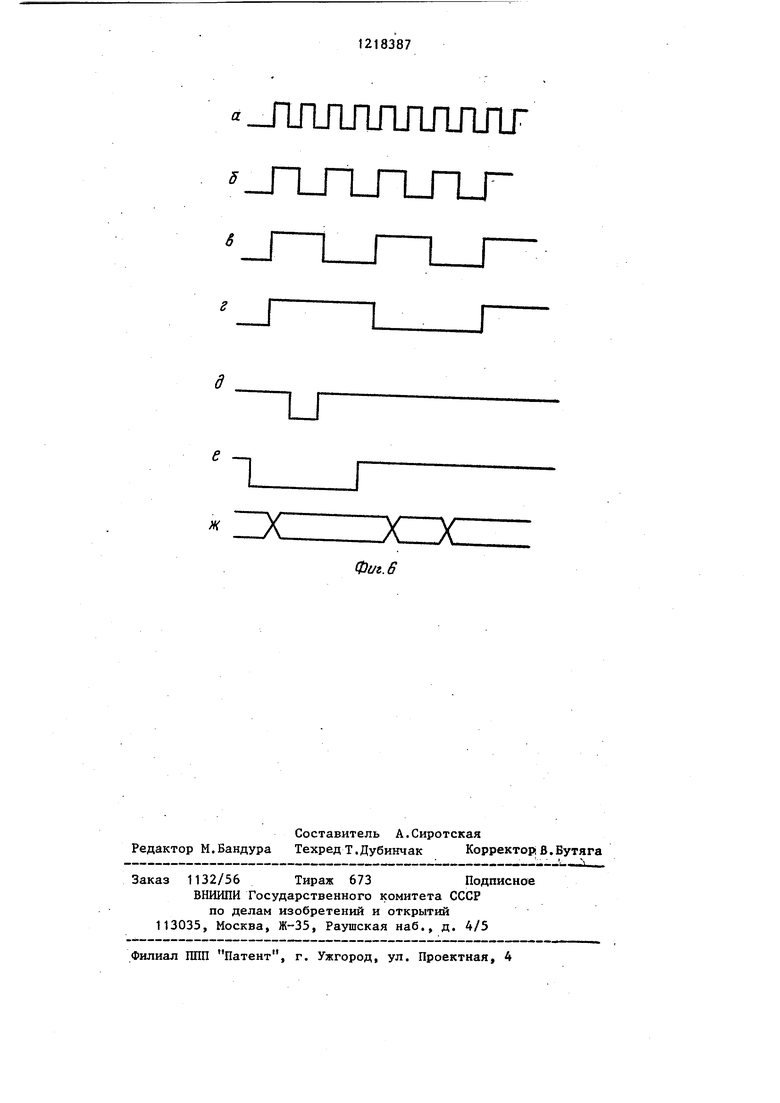

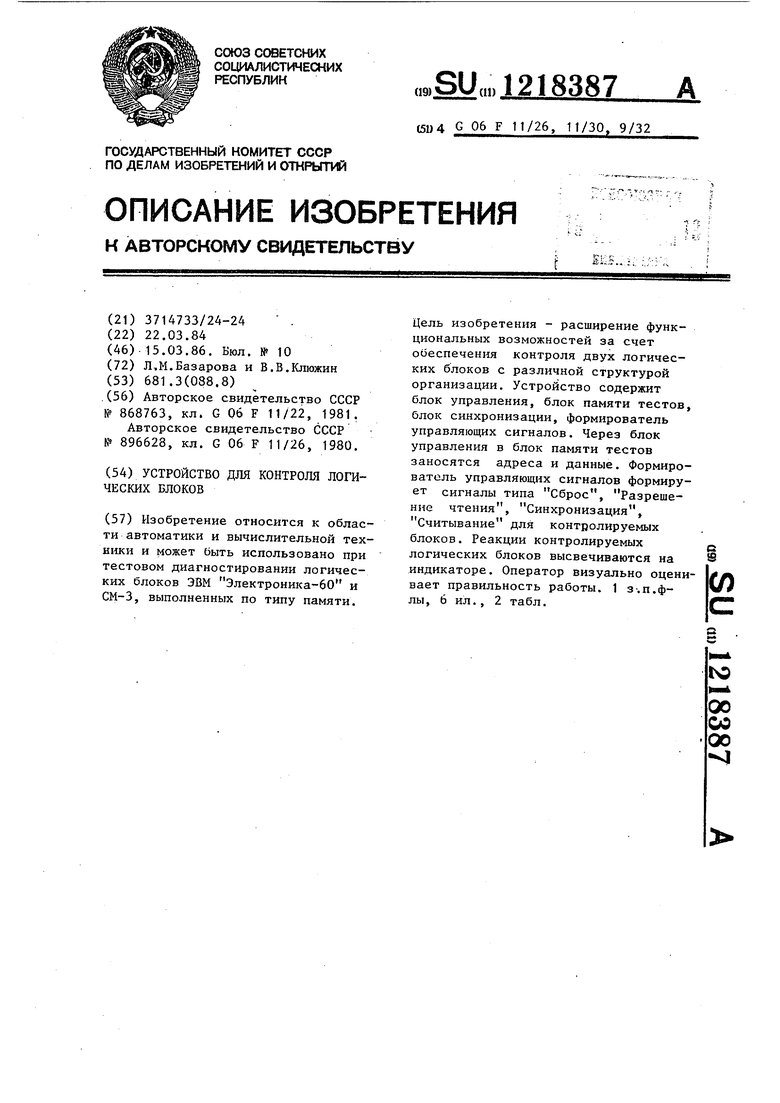

На фиг. 1 представлена функциональная блок-схема устройства; на фиг, 2- блок-схема блока управления; фиг. 3 - блок-схема блока синхронизации; на фиг. 4 - блок-схема блока памяти тестов; на фиг. 5 - блок-схма формирователя управляющих сигна- лов; на фиг. 6 - временная диаграмма, поясняющая выполнение программы обращения к логическим блокам и ра- боту устройства для контроля логических блоков.

Устройство содержит (фиг. 1) блок управления 1, блок синхронизации 2, блок памяти тестов 3, блок-: индикации 4, формирователь управля- ющих си1 налов 5, первый и второй контролируемые логические блоки 6 и 7.

Блок управления 1 (фиг. 2) содер лсит реверсивный счетчик 8, нулевой выход 9 счетчика, группу переключателей 10, кнопку 11 начального сбро са, переключатель 12 задания режима работы устройства, перектпочатель 13 задания режима работы блока памяти тестов, переключатель 14 задания режима работы контролируемых логических блоков, узел 15 потенцианого согласования.

Блок синхронизации 2 (фиг. 3) содержит первый генератор тактовых импульсов 16, второй генератор такт вых импульсов 17, элемент liilH 18, переключатель 19, кнопку 20, элемен И 21 .

Блок памяти тестов 3 (фиг. 4) со .держит первый и второй узлы памяти 22, 23, две группы элементов И 24, 25, элемент памяти 26, две группы со1 ласующих элементов 27, 28 согласующий элемент 29.

Формирователь управляющих сигнал 5 (фиг. 5) содержит элементы НЕ-30- 33, элемент задержки 34-36, элеме йт потенциального согласования 37, эле

0 5

0

5

0

менты И-НЕ 38-44. Элемент задержки построен па диоде и конденсаторе. Элемент потенциального согласования содержит резистор и конденсатор и служит для согласования входа и выхода микросхем различных типов.

Устройство работает следующим образом.

Блок памяти тестов содержит программу работы контролируемого логического блока. Для этого составляв ются программы обращений первому и второму логическим блокам. . Оператор с помощью кнопки 20 блока синхронизации формирует импульс (фиг. 6 о), который поступает на вычитающий вход реверсивного счетчика 8, изменяя последовательно состояние счетчика на единицу (фиг. 6& , & , г ). Этот же импульс поступает на четвертый вход формирователя управляющих сигналов (фиг. 6д ). Выходы реверсивного счетчика 8 соедине- ны с адресными входами узлов памяти 22, 23 генератора тестов 3. В эти узлы 22, 23 необходимо занести данные, которые оператор задает при помощи переключателей 10 группы. Замкнутый переключатель 10 из группы соответствует подаче нулевого потенциала на информационные входы узлов памяти 22, 23 а разомкнутый соответственно единичному потенциалу.

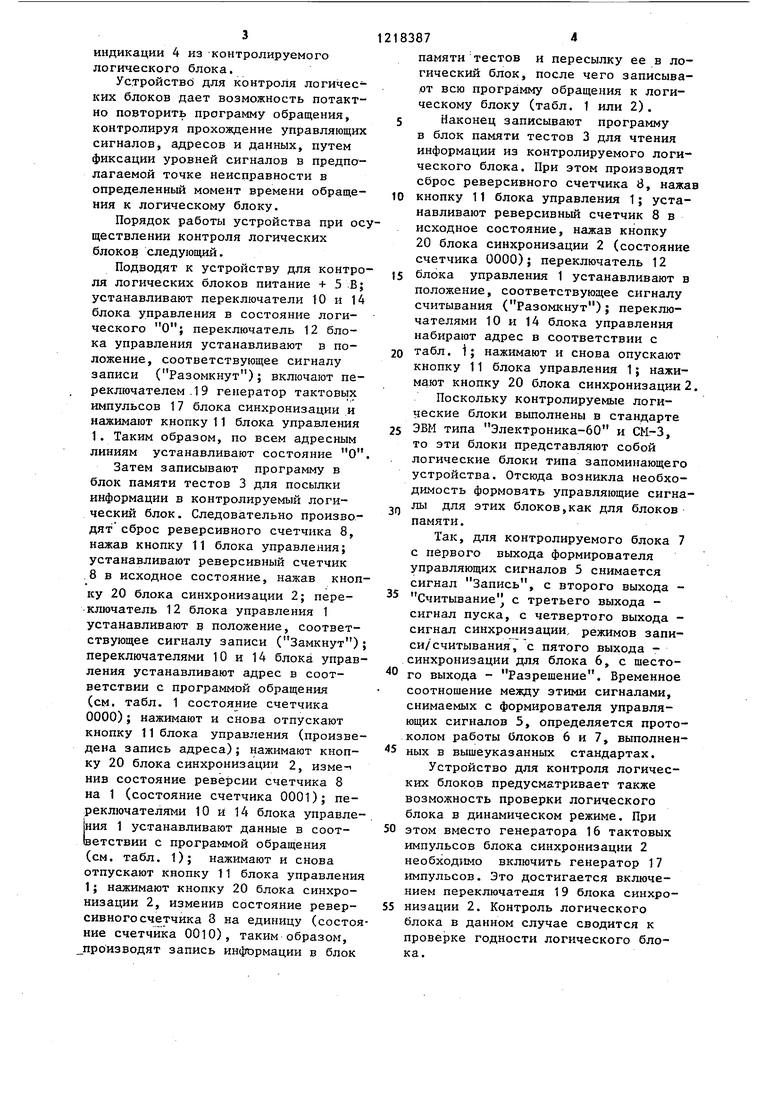

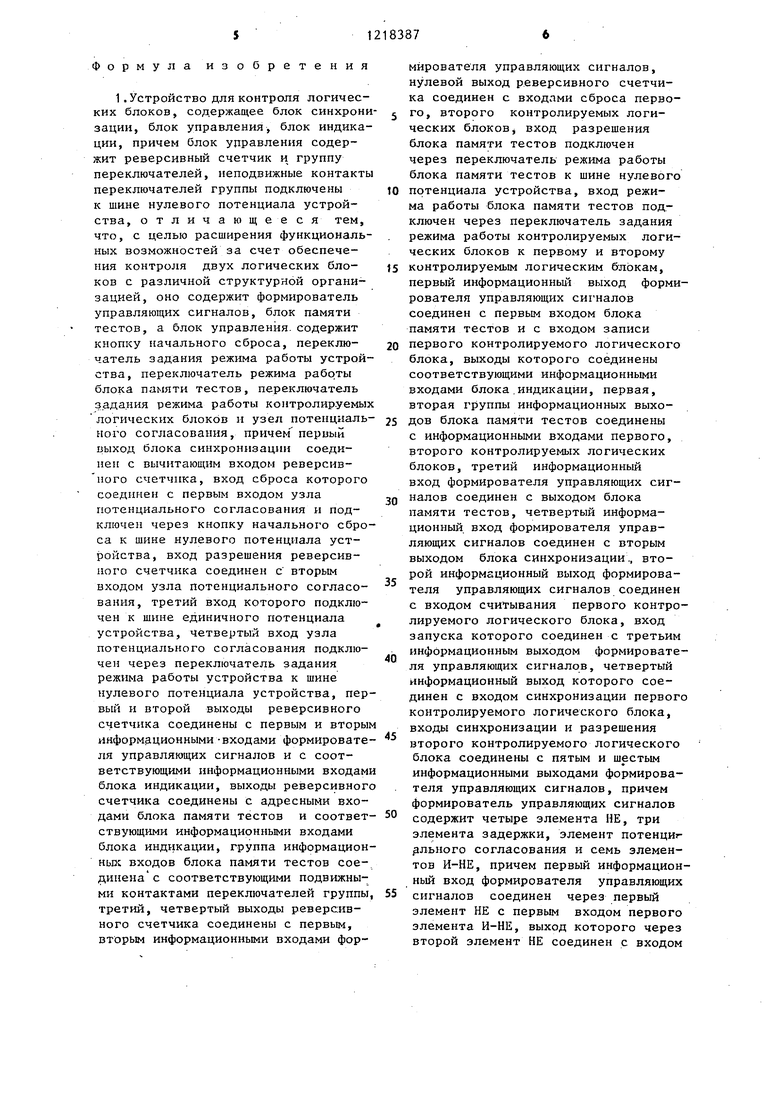

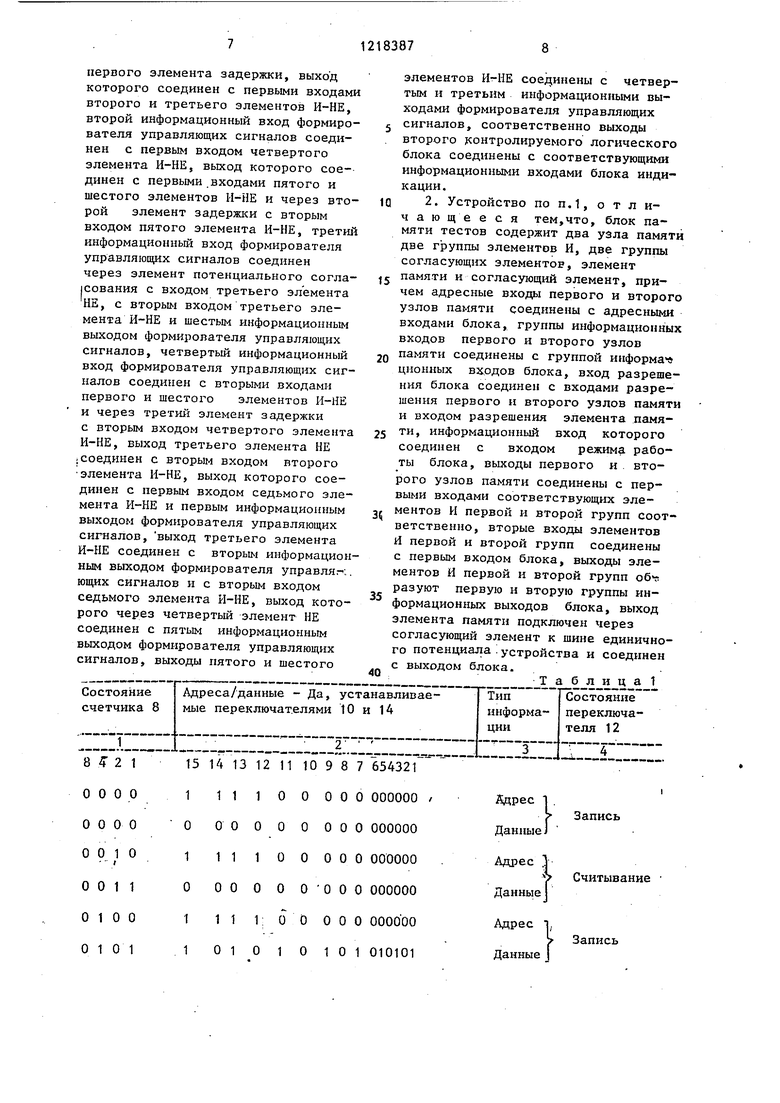

Пример программы обращения к логическим блокам, выполненным в стандарте ЭВМ Электроника-60, показан в табл. 1.

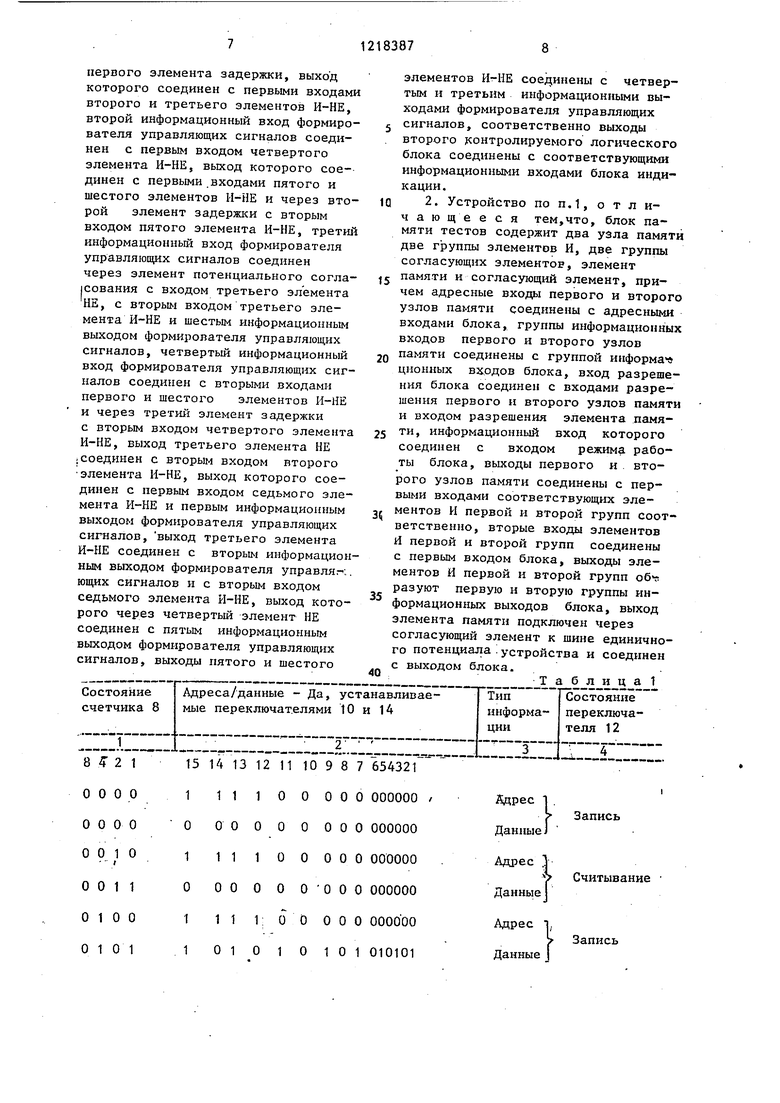

Пример программы обращения к логическим блокам, выполненным в стан- дарт е ЭВМ.СМ-3 приведен в табл. 2.

Сопоставляя считанную информацию из контролируемого логического блока, выведенную на блок индикации 4, с информацией программы обращения, можно определить исправен конт- ролируемый блок или нет, а т.акже место неисправности вплоть до отказавшего элемента.

При состоянии переключателя 12 в положении Запись (переключатель разомкнут) данные согласно табл. 1 и 2 устанавливают с помощью переключателей 10 группы и переключателя 14 на блок управления 1. При состоянии переключателя 12 в положении считывания (переключатели 12 замкнут) данные поступают на блок

3

индикации 4 из -контролируемого логического блока.

Устройство для контроля логических блоков дает возможность потакт- но повторить программу обращения, контролируя прохождение управляющих сигналов, адресов и данных, путем фиксации уровней сигналов в предполагаемой точке неисправности в определенный момент времени обращения к логическому блоку.

Порядок работы устройства при осществлении контроля логических блоков следующий.

Подводят к устройству для контроля логических блоков питание + 5 Bj устанавливают переключатели tO и 14 блока управления в состояние логического переключатель 12 блока управления устанавливают в положение, соответствующее сигналу записи (Разомкнут); включают переключателем . 1 9 генератор тактовых импульсов 17 блока синхронизации и нажимают кнопку 11 блока управления 1. Таким образом, по всем адресным линиям устанавливают состояние О

Затем записывают программу в блок памяти тестов 3 для посылки информации в контролируемый логический блок. Следовательно производят сброс реверсивного счетчика 8, нажав кнопку 11 блока управления; устанавливают реверсивный счетчик .8 в исходное состояние, нажав кнопку 20 блока синхронизации 2; пере- ключатель 12 блока управления 1 устанавливают в положение, соответствующее сигналу записи (Замкнут) переключателями 10 и 14 блока управления устанавливают адрес в соответствии с программой обращения (см. табл. 1 состояние счетчика 0000); нажимают и снова отпускают кнопку 11 блока управления (произведена запись адреса); нажимают кнопку 20 блока синхронизации 2, изме-i нив состояние реверсии счетчика 8 на 1 (состояние счетчика 0001); переключателями 10 и 14 блока управле |ния 1 устанавливают данные в соответствии с программой обращения (см. табл. 1); нажимают и снова отпускают кнопку 11 блока управлени 1; нажимают кнопку 20 блока синхронизации 2, изменив состояние реверсивного счетчика 3 на единицу (состоние счетчика ООЮ), таким образом, производят запись информации в блок

183874

памяти тестов и пересылку ее в логический блок, после чего записыва- |ОТ всю программу обращения к логическому блоку (табл. 1 или 2).

5 Наконец записывают программу в блок памяти тестов 3 для чтения информации из контролируемого логического блока. При этом производят сброс реверсивного счетчика 8, нажав

10 кнопку 11 блока управления 1; устанавливают реверсивный счетчик 8 в исходное состояние, нажав кнопку 20 блока синхрониаации 2 (состояние счетчика 0000); переключатель 12

15 блока управления 1 устанавливают в положение, соответствующее сигналу считывания (Разошснут); переключателями 10 и 14 блока управления набирают адрес в соответствии с

20 табл. 1; нажимают и снова опускают кнопку 11 блока управления 1; нажимают кнопку 20 блока синхронизации 2.

Поскольку контролируемые логические блоки вьшолнены в стандарте

25 ЭВМ типа Электроника-60 и СМ-3, то эти блоки представляют собой логические блоки типа запоминающего устройства. Отсюда возникла необходимость формовать управляющие сигна,- лы для этих блоков,как для блоков памяти.

Так, для контролируемого блока 7 с первого выхода формирователя управляющих сигналов 5 снимается сигнал Запись, с второго выхода Считывание с третьего выхода - сигнал пуска, с четвертого выхода - сигнал синхронизации., режимов записи/считывания, с пятого выхода - синхронизации для блока 6, с шесто го выхода - Разрешение. Временное соотношение между этими сигналами, снимаемых с формирователя управляющих сигналов 5, определяется протоколом работы блоков 6 и 7, выполнен 5 ных в вышеуказанных стандартах.

Устройство для контроля логических блоко.в предусматривает также возможность проверки логического блока в динамическом режиме. При

50 этом вместо генератора 16 тактовых импульсов блока синхронизации 2 необходимо включить генератор 17 импульсов. Это достигается включением переключателя 19 блока синхро55 ниэации 2. Контроль логического блока в данном случае сводится к проверке годности логического блока.

Формула изобретения

1.Устройство для контроля логических блоков, содержащее блок синхрони зации, блок управления, блок индикации, причем блок управления содержит реверсивный счетчик и группу переключателей, неподвижные контакты переключателей группы подключены к шине нулевого потенциала устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля двух логических бло- ков с различной структурной организацией, оно содержит формирователь управляющих сигналов, блок памяти тестов, а блок управления, содержит кнопку начального сброса, переклю- чатель задания режима работы устройства, переключатель режима рабо.ты блока памяти тестов, переключатель задания режима работы контролируемых логических блоков и узел потенциаль- ного согласования, причем первый выход блока синхронизации соединен с вычитающим входом реверсив- ного счетчика, вход сброса которого соединен с первым входом узла потенциального согласования и подключен через кнопку начального сброса к шине нулевого потенциала устройства, вход разрешения реверсивного счетчика соединен с вторым входом узла потенциального согласо- вания, третий вход которого подключен к шине единичного потенциала устройства, четвертый вход узла потенциального согласования подключен через переключатель задания режима работы устройства к шине нулевого потенциала устройства, первый и второй выходы реверсивного счетчика соединены с первым и вторым информационными-входами формировате- ля управляющих сигналов и с соответствующими информационными входами блока индикации, выходы реверсивного счетчика соединены с адресными входами блока памяти тестов и соответ- ствующими информационными входами блока индикации, группа информацион- HbDi входов блока памяти тестов соединена с соответствующими подвижными контактами переключателей группы, третий, четвертый выходы реверсивного счетчика соединены с первым, вторым информационными входами фор

мйрователя управляющих сигналов, нулевой выход реверсивного счетчика соединен с входами сброса первого, второго контролируемых логических блоков, вход разрешения блока памяти тестов подключен через переключатель режима работы блока памяти тестов к шине нулевого потенциала устройства, вход режима работы блока памяти тестов подключен через переключатель задания режима работы контролируемых логических блоков к первому и второму контролируемым логическим блокам, первый информационный выход формирователя управляющих сигналов соединен с первым входом блока памяти тестов и с входом записи первого контролируемого логического блока, выходы которого соединены соответствующими информационными входами блока.индикации, первая, вторая группы информационных выходов блока памяти тестов соединены с информационными входами первого, второго контролируемых логических блоков, третий информационный вход формирователя управляющих сигналов соединен с выходом блока памяти тестов, четвертый информационный вход формирователя управляющих сигналов соединен с вторым выходом блока синхронизации., второй информационный выход формирователя управляющих сигналов соединен с входом считывания первого контролируемого логического блока, вход запуска которого соединен с третьим информационным выходом формирователя управляющих сигналов, четвертый информационньй выход которого соединен с входом синхронизации первого контролируемого логического блока, входы синхронизации и разрешения второго контролируемого логического блока соединены с пятым и шестым информационными выходами формирователя управляющих сигналов, причем формирователь управляющих сигналов содержит четыре элемента НЕ, три элемента задержки, элемент потенцит- эльного согласования и семь элементов И-НЕ, причем первый информационный вход формирователя управляющих сигналов соединен через первый элемент НЕ с первым входом первого элемента И-НЕ, выход которого через второй элемент НЕ соединен с входом

первого элемента задержки, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, второй информационный вход формирователя управляющих сигналов соединен с первым входом четвертого элемента И-НЕ, вькод которого соединен с первыми.входами пятого и шестого элементов И-НЕ и через второй элемент задержки с вторым входом пятого элемента И-НЕ, третий информационный вход формирователя управляющих сигналов соединен через элемент потенциального согла- |сования с входом третьего элемента НЕ, с вторым входом третьего элемента И-НЕ и шестым информационным выходом формирователя управляющих сигналов, четвертый информационный вход формирователя управляющих сигналов соединен с вторыми входами первого и шестого элементов И-НЕ и через третий элемент задержки с вторым входом четвертого элемента И-НЕ, выход третьего элемента НЕ .соединен с вторым входом второго элемента И-НЕ, выход которого соединен с первым входом седьмого элемента И-НЕ и первым информационным выходом формирователя управляющих сигналов, выход третьего элемента И-НЕ соединен с вторым информационным выходом формирователя управляв; ющих сигналов и с вторым входом седьмого элемента И-НЕ, выход которого через четвертый элемент НЕ соединен с пятым информационным выходом формирователя управляющих сигналов, выходы пятого и шестого

14 13 12 11 10 9 8 7 654321 11100000 000000 / 00000000 000000 11 1 00000 000000 00 о о О ООО 000000 11 1; 00 000 ОООО ОО 01010101 010101

элементов И-НЕ соединены с четвертым и третьим информационными выходами формирователя управляющих

J сигналов, соответственно выходы второго контролируемого логического блока соединены с соответствующими информационными входами блока индикации.

Q 2. Устройство по п.1, о т л и- чающееся тем,что, блок памяти тестов содержит два узла памяти две группы элементов И, две группы согласующих элементов, элемент

5 памяти и согласующий элемент, причем адресные входа первого и второго узлов памяти соединены с адресными входами блока, группы информационных входов первого и второго узлов

Q памяти соединены с группой информа ционных входов блока, вход разрешения блока соединен с входами разрешения первого и второго узлов памяти и входом разрешения элемента памя5 ти, информационный вход которого соединен с входом режима работы блока, выходы первого и второго узлов памяти соединены с первыми входами соответствующих элементов И первой и второй групп соответственно, вторые входы элементов И первой и второй групп соединены с первым входом блока, выходы элементов И первой и второй групп об- разуют первую и вторую группы информационных выходов блока, выход элемента памяти подключен через согласующий элемент к шине единичного потенциала устройства и соединен с выходом блока.

Таблица1

5

5

Запись

Считывание

Запись

111100000 000000

101010101 010101

111 1 00000 000000

II.V 1t

01010-1010 101010

111100000 000000

010101010 101010

Адреса - А, набираемые переключателями

1514131211109876543210 1 1 1 1 00 0000000000 1 1 1 1 00 0000000000

1 1 I 1 00 0000000000 1 1 1 1 00 0000000000

фиг.1

Адрес Данные

Адрес

Считывание

Запись

Данные J Адрес j Данные J

Считывание

Таблица2

Данные - Д, заносимые с помощью переключателей 10 в блоки 22,23

151413121110987654321 10 1 О 10 101010101 10 1010 101010101

01 о 1 01 010101010 0. 1 о 1 01 010101010

Г

12

Л

иг.З

fj

1218387

2 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля функционирования логических блоков | 1988 |

|

SU1599860A2 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при тестовом диагностировании логических блоков ЭВМ Электроника-60 и СМ-3, выполненных по типу памяти. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля двух логических блоков с различной структурой организации. Устройство содержит блок управления, блок памяти тестов, блок синхронизации, формирователь управляющих сигналов. Через блок управления в блок памяти тестов заносятся адреса и данные. Формирователь управляющих сигналов формирует сигналы типа Сброс, Разрешение чтения, Синхронизация, Считывание для контполируемых блоков. Реакции контролируемых логических блоков высвечиваются на индикаторе. Оператор визуально оценивает правильность работы. 1 з-.п.ф- лы, 6 ил., 2 табл. i (Л С to 00 со 00

,. ..

71I т I

I flffjflea/efrVi

Cuffjrpfyn/Cft/fn.)(i

ii

ns/cK

I

. 5

« ПЛЛЛГ1ЛЛЛЛГ

ж

их

Редактор

Составитель А.Сиротская М.Бандура Техред Т.Дубинчак Корректор В.Бутяга

Подписное

Заказ 1132/56 Тираж 673

ВНИИПИ Государственного комитета CCOf

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/Ь

Филиал ППП

Патент, г. Ужгород, ул. Проектная, 4

xzx

фиг. 6

Подписное

Авторы

Даты

1986-03-15—Публикация

1984-03-22—Подача