I

Изобретение относится к автоматике и вычислительной технике, а . именно к устройствам для преобразования данных, и может быть использовано в 1ЩФРОВЫХ устройствах управления антенной, работающих в реальном времени, для преобразования углового положения антенны и времени, представленных в двоично-десятично- шестидесятиричной системе счисления (градусы, часы, минуты, секунды в двоичную систему счисления с различной ценой единицы i младшего разряда.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения преобг- разования двоично-десятично-шести- десятиричного.кода в двоичный код с масштабированием.

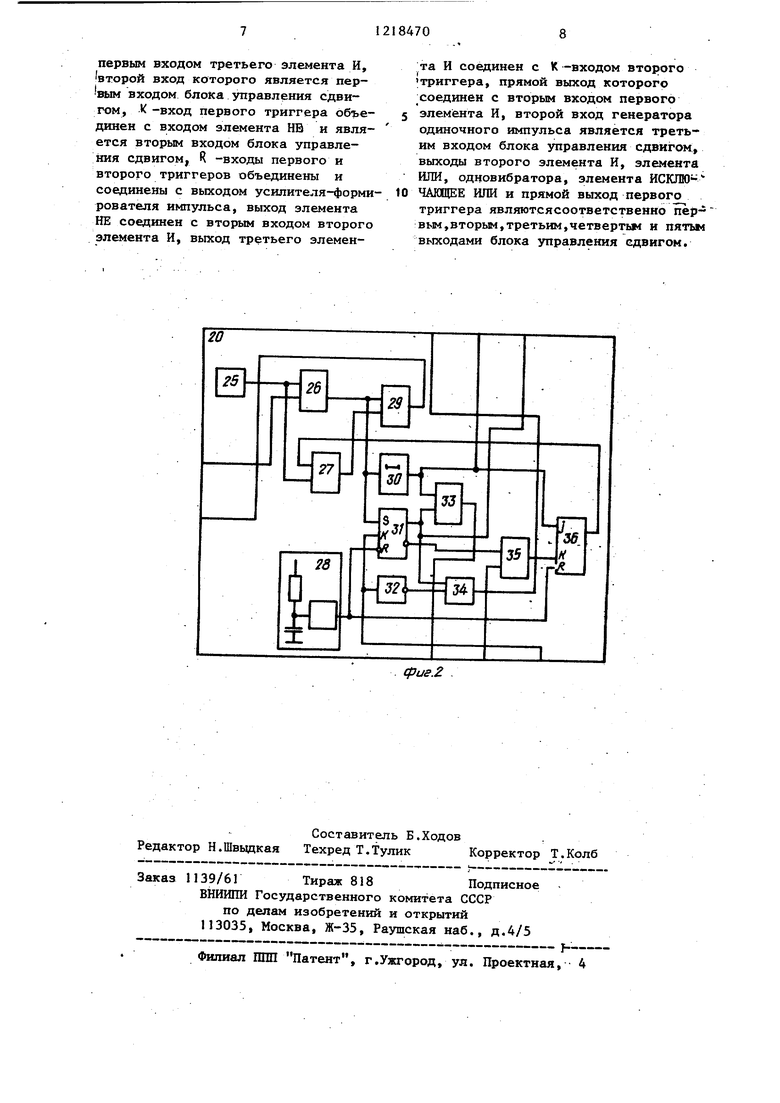

На фиг,1 изображена функциональная схема устройства; на фиг.2 - схема блока управления сдвигом.

Устройство для преобразования кодов содержит первый сдвигающий регистр 1, первый 2, второй 3, третий 4, и четвертый 5 формирователи тетрад, первьй б и второй 7 формирователи триад, первый 8 и второй 9 блоки элементов И, блок 10 элементов ИЛИ, второй сдвигающий регистр 11, блок 12 сумматоров, первый элемент И 13, первый элемент НЕ 14, второй элемент НЕ 15, второй элемент И 16, первый элемент ИЛИ 17, триггер 18, второй элемент ИЛИ 19, блок 20 управления сдвигом, входы 21, 22 устройства, выход 23 устройства, запускающий вход 24 устройства.

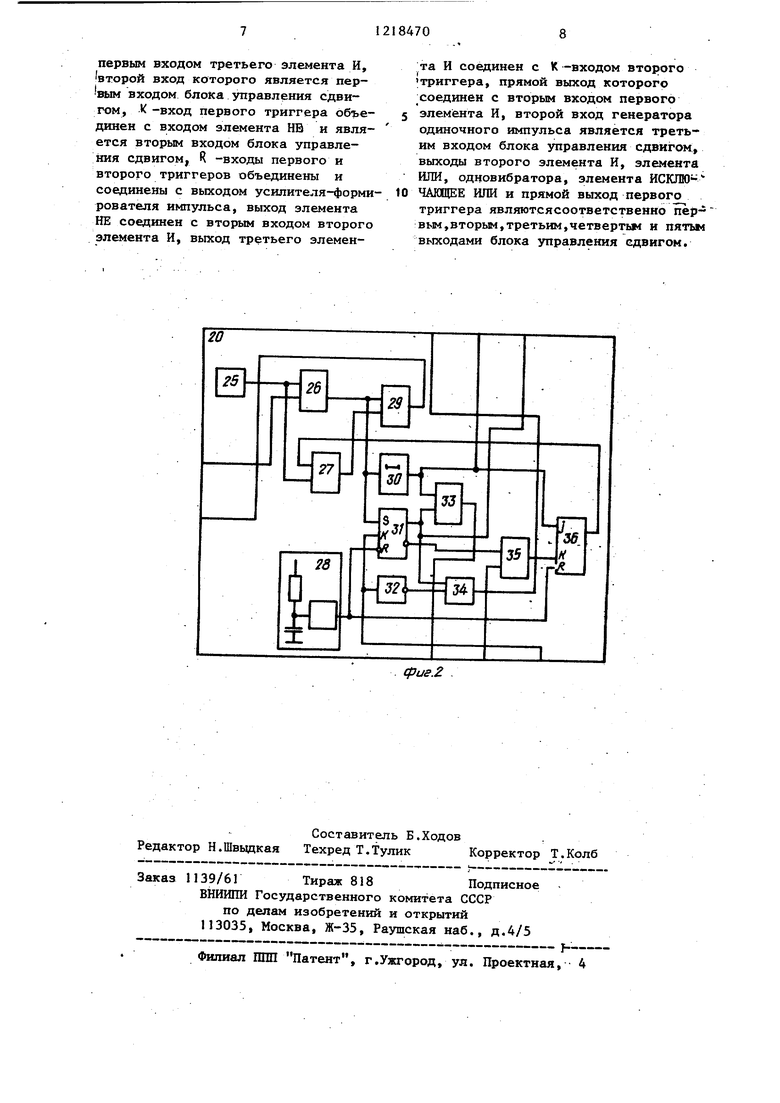

Блок 20 управления сдвигом содержит генератор 25 импульсов, генератор 26 одиночного импульса, первый элемент И 27, усилитель-формирователь 28 импульса, элемент ИЛИ 29, одновибратор 30, первый триггер 31, элемент НЕ 32, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33, второй элемент И 34, третий элемент И 35, второй триггер 36.

Устройство работает следующим образом.

После включения регистры 1 и 11 устанавливаются в исходное состояние блоком 20 управления сдвигом, а на вход первого элемента НЕ 14, соединенного с входом второго элемента ИЛИ 17, с последнего поступает сигнал логической 1. Сле184701

довательно, запрещается работа пep- вого элемента И 13 сигналом с пер- . вого элемента НЕ 14 и разрешается работа второго элемента И 16 5 через элемент ИЛИ 17.

В первом регистре 1 производится сдвиг и преобразование записанного с информационных входов 21 двоично- десятично-шестидесятиричного кода в 10 двоичный с помощью формирователей 2-7 тетрад. Алгоритм работы формирователей 2,3,4,5 тетрад следующий:

4

У, Х.Х, VX Х,;

Xj.x, vx,.x.x,v .x a X, 4 V 5

У X,X,jX,Y X,j Х,

где х, Xj, X , - входные сигналы

в порядке возрастания номера разряда;

УоУч Ь У Ь1ходные сигналы в порядке возрастания но- . .мера разряда.

Алгоритм работы формирователей 6,7 триад следующий:

У,

t X, ,

Xj X, X, Xj X,j Xj X«V X X

где x XX - выходные сигналы в порядке возрастания номера разряда;

Й1)У.Уэ и одныв сигналы в порядке возрастания номера разряда.

Преобразование кода осуществляется путем перезаписи кода, сформированного на выходах формирователей 2-7 триад и тетрад через первый блок 8 элементов И и блок 10 элементов ИЛИ в регистр 1 с помощью тактовых импульсов, поступающих с бло- ка 20 управления сдвигом на вход первого регистра 1.

Запуск устройства осуществля- ется сигналом Пуск с входа 24,

поступающим на блок 20 управления сдвигом, при этом информация

hразрядов) с входов 21 через второй блок 9 элемен тов И и блок 10 элементов ИЛИ записывается в первый регистр 1 с помощью импульса запи- си, поступающего с блока 20 управения Сдвигом на вторые входы второго блока 9 элементов И. Одновременно с помощью этого же импульса

в триггере 18 запоминается сигнал

0необходимости масштабирования информации (логическая 1 при наличии информации о времени и логический О при информации о i координатах), а во второй регистр 11, в(1-3) -и разряд, записьшается сигнал логической 1, с помощью которого осуществляется управление циклами работы устройства,

Первый цикл работы устройства- преобразование двоично-десятично- шестидесятиричиого кода в двоичный и второй - масштабирование кода.

Блок 20 управления сдвигом включает режим Запись в первом регистре 1 и режим Сдвиг - во втором регистре 11, вырабатьюает тактовые импульсы, осуществляющие преобразование информации из двоично-десятично-шестидесятиричногокода в двоичный код в первом регистре 1 и сдвиг информации во втором регистре 11. При зтом полученный двоичный код поступает с младшего разряда первого сдвиговог регистра 1 на информационный вход второго регистра II,а логическая 1 в ( и-З)-ом разряде второго регистра 11 смещается в сторону младшего разряда. При установке после 20-го импульса) младшего разряда .в 1 блок 20 управления сдвигом переключает первый регистр

1в режим сдвига. После перехода информации с младшего разряда регистра II через элемент И 16 и . элемент ИЛИ 17 в старший разряд первого ре гистра 1 блок 20 управления сдвигом вырабатьюает сигнал логического О на вход элемента НЕ 14, тем самым заканчивается первый цикл работы, связанный с преобразованием, разрешается работа элемента И 13 и через элемент ШШ 17 запрещается работа элемента И 16. При этом могут возникнуть следующие ситуации:

триггер 18 - в состоянии I входная информация не требует масштабирования), поэтому работа элемента И 13 запрещена (через элемент НЕ 15), а работа элемента И 16 разрещеиа через элемент ИПИ 17, в этом случае информация без масштабирования через элемент И 16 поступает на первый регистр 1

триггер 18 - в состоянии О (входная информация об углах и тре218470

бует масштабирования), поэтому информация с второго регистра 11 через блок 12 сумматоров, элемейт И 13, элемент ИЛИ 19 в последовательном

5 коде поступает на первый регистр 1.

Преобразованная в двоичный код информация после первого цикла работы находится во втором регистре 1 1 и начинается второй цикл . 10 работы. В случае преобразования временного кода во втором цикле инфор-г мация из второго регистра 11 через элемент И 16 и элемент ИЛИ 19 поступает на первый регистр 1 и при

15 появлении логической 1 на выходе младшего разряда первого регистра 1 блок 20 управления сдвигом прекращав ет вьщачу тактовой частоты и на выходах разрядов первого регистра

20 устанавливается преобразованный двоичный код, который поступает на выход 23 устройства преобразования кодов.

При преобразовании угловых вели25 чин необходимо масштабирование сигналов , поэтому на блок 12 сумматоров поступает информация с первого, третьего, пятого, девятого, двенадцатого, девятнадцатого и двадцать :

3Q второго разрядов второго регистра 11, что обеспечивает получение с выхода блока 12 сумматоров информацию в последовательном коде.

Устройство для преобразования кода преобразует двоично-десятично- шестидесятиричный код в двоичный с точностью до одной угловой секунды, причем формирователь 2 тетрад формирует единицы секунд, формирова-

тель 6 триад - десятки секунд, фор- 40

мирователь 3 тетрад - единицы минут

формирователь 7 триад - десятки минут, формирователь 4 тетрад-еди- ницы градусов (часов), формирователь 5 тетрад - десятки градусов (часов). Число элементов в первом блоке 8 элементов И равно h -1, а во втором блоке 9 элементов И,, блоке 10 элементов ШШ и число разрядов в первом 1 и втором 11 регистрах соответствует числу разрядов выходного кода h

35

45

50

Формула изобретени

55 1.Устройство для преобразования .кодов, содержащее первый сдвигающий регистр, формирователи тетрад и блок управления сдвигом, первый

выход которого соединен с управ-. ляющим входом первого сдвигающего регистра, о тлич ающе еся .тем, что, с целью расширения функциональных возможностей устройства путем обеспечения преобразования двоично-десятично-шестидесятирично го кода в двоичный код с масштабирванием, в него введены триггер, элементы НЕ, элементы ИЛИ, элементы И, блок сумматоров, блоки элементов И, блок элементов ИЖ, два формирователя триад и второй сдвигающий регистр, управляющий вход которого соединен с вторьи выходом блока управления сдвигом, информационный вход объединен с первым входом блока управления сдвигом и соединен с выходом первого разряда первого сдвигающего регистра выходы последующих разрядов которого, кроме последнего, соединены с соответствующими входами первого формирователя тетрад, первого фор- 1ушрователя триад, второго формирователя тетрад, второго формирователя триад, третьего и четвертого формирователей тетрад, выход последнего разряда первого сдвигакмце- го регистра соединен с первым входом первого элемента И первого блока элементов И, первые входы последующих элементов И первого блока элементов И соединены с выходами соответствзпощих формирователей тетрад и триад, первые входы второ го блока элементов И объединены с С-входом триггера и соединены с третьим выходом блока управления сдвигом, четвертый выход которого соединен с вторыми входами элементов И первого блока элементов. И, выходы Первого и второго блоков элементов И соединены с соответствующими входами блока элементов ИЛИ, выходы которого соединены с соответствующими первыми информационными входами первого сдвигающего регистра, первый, третий, . пятый, девятый, двенадцатый, девятнадцатый и двадцать второй выходы второго сдвигающего регистра соединены с соответствующими входами блока сумматоров, выход которого соединен с первым входом первого элемента И, второй вход кото-рого соединен с выходом первого

элемента НЕ, третий вход - с выходом второго элемента НЕ, первьш вход первого элемента ИЛИ объеди- 5 нен с входом первого элемента НЕ и соединен с пятым выходом блока управления сдвигом, второй вход первого элемента ИЛИ объединен с входом второго элемента НЕ и сое0 динен с вькодом триггера, первый вход второго элемента И объединен о вторым входом блока управления сдвигом и соединен с выходом первого разряда второго сдвигающего

5 регистра, второй вход второго эле-, мента И соединен с выходом первого элемента ИЛИ, выход - с первым входом второго элемента ИЛИ, второй вход которого соединен с вько0 дом первого элемента И, выход - с вторым информационным входом первого сдвигающего регистра, вторые входы элементов И второго блока элементов, И и D -вход триггера

5 являются входами устройства, выходы первого, сдвигающего регистра, кроме первого и последнего, явля- (отся выходом устройства, третий вход блока управления сдвигом

0 является запускающим входом устройства.

2. Устройство по П.1, отличающееся тем, что блок управления сдвигом состоит из гене-, ратора Импульсов, генератора одиночного импульса,- первого элемента И, усилителя-формирователя импульса, элемента ИЛИ,одновибратора, вого триггера, элемента НЕ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второго и третьего элементов И и второго триггера, выход генератора импуль сов соединен с первыми выходами генератора одиночного импульса и первого элемента И, выходы которых соединены соответственно с первым и . вторым входами элемента ИЛИ,5 -вход первого триггера объединен с входом одновибратора и соединен с выходом генератора одиночного импульса, 3-вход второго триггера объединен с первым выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом одно-вибратора, второй вход элемента 5 ИСКЛЮЧАЮЩЕЕ ИЛИ объединен с первым входом второго элемента соединен (С прямым выходом первого триггера, ;Инверсный выход которого соединен с

5

0

5

первым входом третьего элемента И, второй вход которого является пер- вым входом блока управления сдвигом, 1 -вход первого триггера объединен с входом элемента НВ и является вторым входом блока управления сдвигом, R -входы первого и второго триггеров объединены и соединены с выходом усилнтеля-форми- рователя импульса, выход элемента НЕ соединен с вторым входом второго элемента И, выход третьего элемента И соединен с К -входом второго триггера, прямой выход которого соединен с вторым входом первого

элемента И, второй вход генератора одиночного импульса является третьим входом блока управления сдвигом, выходы второго элемента И, элемента ИЛИ, одновибратора, элемента ИСКЛЮ

ЧАЩЕЕ ИЛИ и прямой выход первого триггера являютсясоответственно первым, вторым, третьим, четверть и пятым выходами блока управления сдвигом.

Устройство относится к автоматике и вычислительной технике и может найти применение в системах преобразования данных без изменения порядка их следования или объема информации, в частности в устройствах преобразования углового положения антенны и времени, представленных в двоично-десятично-шестидесятиричной системе, счисления,в двоичную систему счисления. Устройство позволяет наряду с преобразованием дво- нчно-десятично-шестидесятиричного кода угловых величин и времени в двоичный код осуществлять и масшта- бирсвание их младших разрядов. В устройство входят первый сдвигающий регистр 1, шесть логических блоков 2-7, два блока 8 и 9 элементов И, блок 10 элементов ИЛИ, второй сдвигающий регистр 11, блок 12 сумматоров , два элемента И 13 и 16, два элемента НЕ 14 и 15, два элемента ИЛИ 17 и 19, триггер 18, блок 20 управлення сдвигом, входы 21 н 22 устройства, в ыход 23 устройства, на котором формируется преобразованный двоичный код, и запускающий вход 24 устройства. 1 з.п.ф-лы, 2 ил. а Ipuf.i

(f}ue.Z

| Преобразователь двоичного кода в двоично-десятичный | 1972 |

|

SU437069A1 |

| Устройство для преобразования кодов | 1972 |

|

SU478299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-07-06—Подача