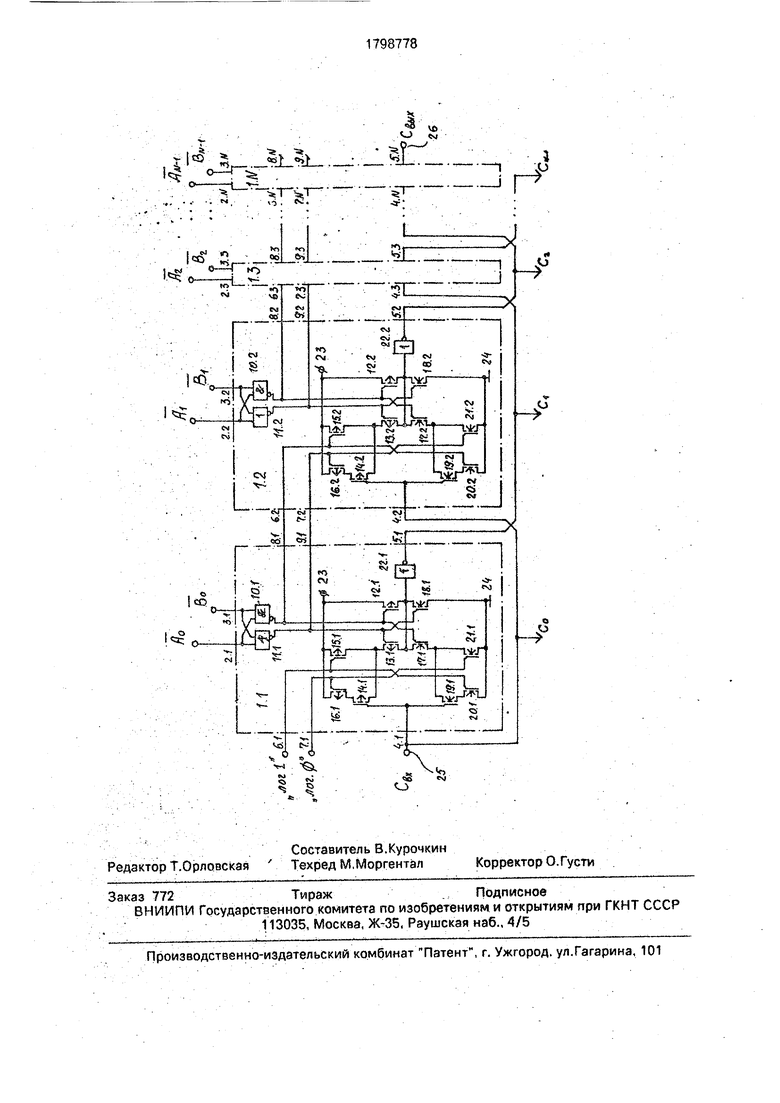

устройства, как Cj,. прямое значение начального переноса устройства как Свх и прямое значение его выходного переноса как Свых.

формирователь переноса работает следующим образом.

Будем считать, что уровень логической Г ( 1) соответствует напряжению шины 23 питания формирователя, а уровень логического О .(О) соответствует напряжению шины 24 нулевого потенциала формирователя. ....

Для удобства выделим следующие два режима работы каждого разряда формирователя:

- режим генерации собственного переноса;

- режим передачи сквозного переноса.

Разряд формирователя переноса работает в режиме генерации собственного переноса при совпадении сигналов на его входах 2 и 3 разрядов операндов; при зтом на его выходах управления 8 и 9 формируются сигналы 00 или 11 и, в случае комбинации 00, открыты первый 12 и второй 13 МДП-транзисторы р-типа, закрыты первый 17 м второй 18 МДП-трзнзисторы п-ти- па, на входе элемента НЕ 22 устанавливается уровень 1, а на выходе 5 переноса данного разряда формирователя - в случае комбинации 11, открыты первый 17 и второй 18 МДП-транзисторы n-типа, закрыты первый 12 и второй 13 МДП-транзисторы р-типа, на входе элемента НЕ 22 устанавливается уровень О, а на выходе 5 переноса данного разряда формирователя - 1.

Разряд формирователя работает в режиме передачи сквозного переноса при несовпадении сигналов на его входах 2 и 3 разрядов операндов; при этом на его первом 8 и втором 9 выходах управления формируются соответственно 1 и О, первый 12 и МДП-траизистор р-типа и второй 18 МДП-транзистор n-типа закрыты, первый 17 МДП-транзистор n-типа и второй 13 МДП- транзистор р-типа открыты, и состояние сигнала на входе элемента НЕ 22 определяется уровнями сигналов на первом 6 и втором 7 входах управления данного разряда формирователя; а также уровнем сигнала на его входе 4 переноса.

Так, если на входах 8 и 7 управления данного разряда формирователя установлена комбинация 00, соответствующая режиму генерации собственного переноса соседнего младшего разряда формирователя, у рассматриваемого разряда формирователя открыты четвертый 15 и пятый 16 МДП-транзисторы р -типа, закрыты четвертый 20 и пятый 21 МДП-транзисторы п-тмпа,

на входе элементе НЕ 22 устанавливается уровень 1, а на выходе 5 переноса данного разряда формирователя - О. Если на входах 6 и 7 управления данного разряда формирователя установлена комбинация 11, также соответствующая режиму генерации собственного переноса соседнего младшего разряда формирователя, у рассматриваемого разряда формирователя открыты

четвертый 20 и пятый 21 МДП-транзисторы п-типа, закрыты четвертый 15 и пятый 16 МДП-транзисторы р-тмпа, на входе элемента НЕ 22 устанавливается уровень О, а на выходе 5 переноса данного разряда формирователя- 1. Если же на первом 6 и втором 7 входах управления данного разряда формирователя установлены состояния 1 и О, соответствующие режиму передачи сквозного переноса соседнего младшего

разряда формирователя, у рассматриваемого разряда формирователя четвертый 15 МДП-транзистор р-типа и пятый 21 МДП- транзистор n-типа закрыты, пятый 16 МДП- траизистор р-типа и четвертый 20

МДП-траизистор n-типа открыты, на вход элемента НЕ 22 через третьи МДП-транзисторы 14 р-типа и 19 n-типа передается двоично-инверсное значение сигнала со входа 4 переноса, и на выходе 5 переноса данного

разряда формирователя устанавливается уровень, соответствующий сигналу на его. входе 4 переноса; сочетание состояний О и 1 на первом 6 и втором 7 входах управления разрядов формирователя запрещено.

Для обеспечения правильности функционирования формирователя у самого младшего его разряда первый 6 и второй 7 входы управления соединены соответственно с 1 и О, а входы 4 переноса у самой младшей

пары его разрядов соединены со входом 25 начального переноса.

Пусть на вход 25 начального переноса формирователя подается прямое значение сигнала входного переноса. Тогда в режиме

передачи сквозного переноса на выходах 5 его разрядов устанавливаются прямые значения поразрядных переносов, и в режиме генерации собственного переноса О на них соответствует комбинации 00й прямых

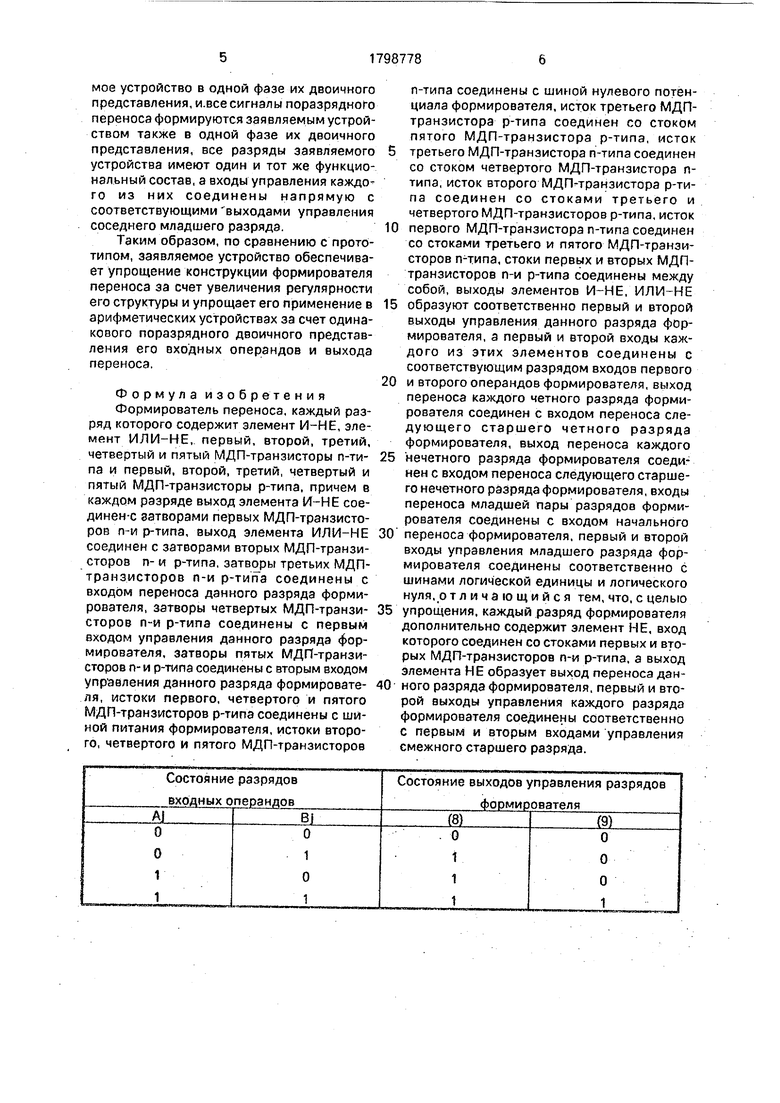

значений сигналов входных операндов, а Т - комбинации 11 этих сигналов и т.д. В таблице отображены возможные состояния на выходах 8 и 9 управления разрядов формирователя, из которой следует, что

они могут быть описаны как:

F{8) AJ V Bj Aj В}, F(9) Aj Bj Aj V BJ .

Из изложенного видно, что все разряды входных операндов подаются на заявлявмое устройство в одной фазе их двоичного представления, и.все сигналы поразрядного переноса формируются заявляемым устройством также в одной фазе их двоичного представления, все разряды заявляемого устройства имеют один и тот же функциональный состав, а входы управления каждого из них соединены напрямую с соответствующими выходами управления соседнего младшего разряда.

Таким образом, по сравнению с прототипом, заявляемое устройство обеспечивает упрощение конструкции формирователя переноса за счет увеличения регулярности его структуры и упрощает его применение в арифметических устройствах за счет одинакового поразрядного двоичного представления его входных операндов и выхода переноса.

Формула изобретения Формирователь переноса, каждый разряд которого содержит элемент И-НЕ, элемент ИЛИ-НЕ, первый, второй, третий, четвертый и пятый МДП-транзисторы п-ти- па и первый, второй, третий, четвертый и пятый МДП-транзисторы р-типа, причем в каждом разряде выход элемента И-НЕ сое- динен-с затворами первых МДП-транзисто- ров n-и р-типа, выход элемента ИЛИ-НЕ соединен с затворами вторых МДП-транзи- сторов п- и р-типа, затворы третьих МДП- транзисторов п-и р-типа соединены с входом переноса данного разряда формирователя, затворы четвертых МДП-транзи- сторов n-и р-типа соединены с первым входом управления данного разряда формирователя, затворы пятых МДП-транзи- сторов п- и р-типа соединены с вторым входом управления данного разряда формирователя, истоки первого, четвертого и пятого МДП-транзисторов р-типа соединены с шиной питания формирователя, истоки второго, четвертого и пятого МДП-транзисторов

n-типа соединены с шиной нулевого потенциала формирователя, исток третьего МДП- транзистора р-типа соединен со стоком пятого МДП-транзистора р-типа, исток

третьего МДП-транзистора n-типа соединен со стоком четвертого МДП-транзистора л- типа, исток второго МДП-транзистора р-типа соединен со стоками третьего и четвертого МДП-трэнзисторов р-типа, исток

первого МДП-транзистора n-типа соединен со стоками третьего и пятого МДП-транзисторов n-типа, стоки первых и вторых МДП- транзисторов n-и р-типа соединены между собой, выходы элементов И-НЕ, ИЛИ-НЕ

образуют соответственно первый и второй выходы управления данного разряда формирователя, а первый и второй входы каждого из этих элементов соединены с соответствующим разрядом входов первого

и второго операндов формирователя, выход переноса каждого четного разряда формирователя соединен с входом переноса следующего старшего четного разряда формирователя, выход переноса каждого

нечетного разряда формирователя соединен с входом переноса следующего старшего нечетного разряда формирователя, входы переноса младшей пары разрядов формирователя соединены с входом начального

переноса формирователя, первый и второй входы управления младшего разряда формирователя соединены соответственно с шинами логической единицы и логического нуля,.от л и ч а ю щи и с я тем, что, с целью

упрощения, каждый разряд формирователя дополнительно содержит элемент НЕ, вход которого соединен со стоками первых и вторых МДП-транзисторов n-и р-типа, а выход элемента НЕ образует выход переноса данного разряда формирователя, первый и второй выходы управления каждого разряда формирователя соединены соответственно с первым и вторым входами управления смежного старшего разряда.

и

о X

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Сумматор | 1986 |

|

SU1406591A1 |

| Блок формирования сквозного переноса в сумматоре | 1979 |

|

SU1042012A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

Авторы

Даты

1993-02-28—Публикация

1991-06-17—Подача