Изобретение относится к электро- связи, в частности к устройствам кор рекции частотньпс характеристик канала связи, и может быть использовано в аппаратуре передачи данных, рабо- таюцей с высокой удельной скоростью, для коррекции межсимвольной интерференции (МСИ).

Цель изобретения - уменьшение времени настройки корректора межсимволь ной интерференции.

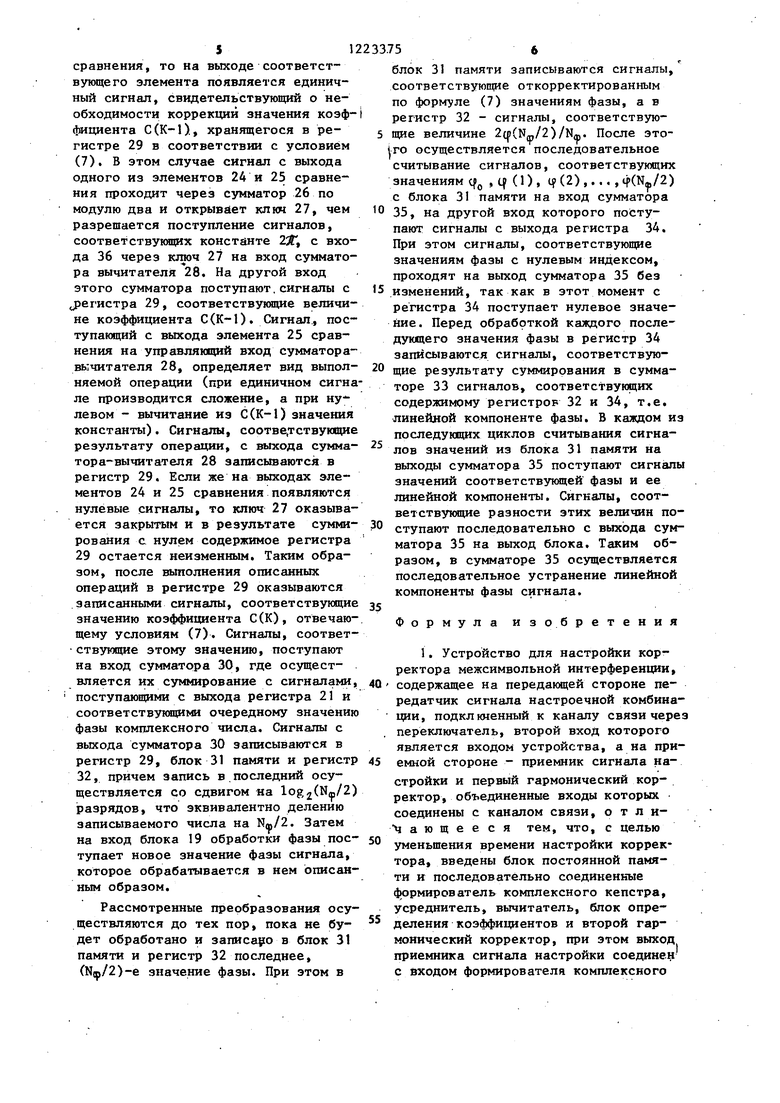

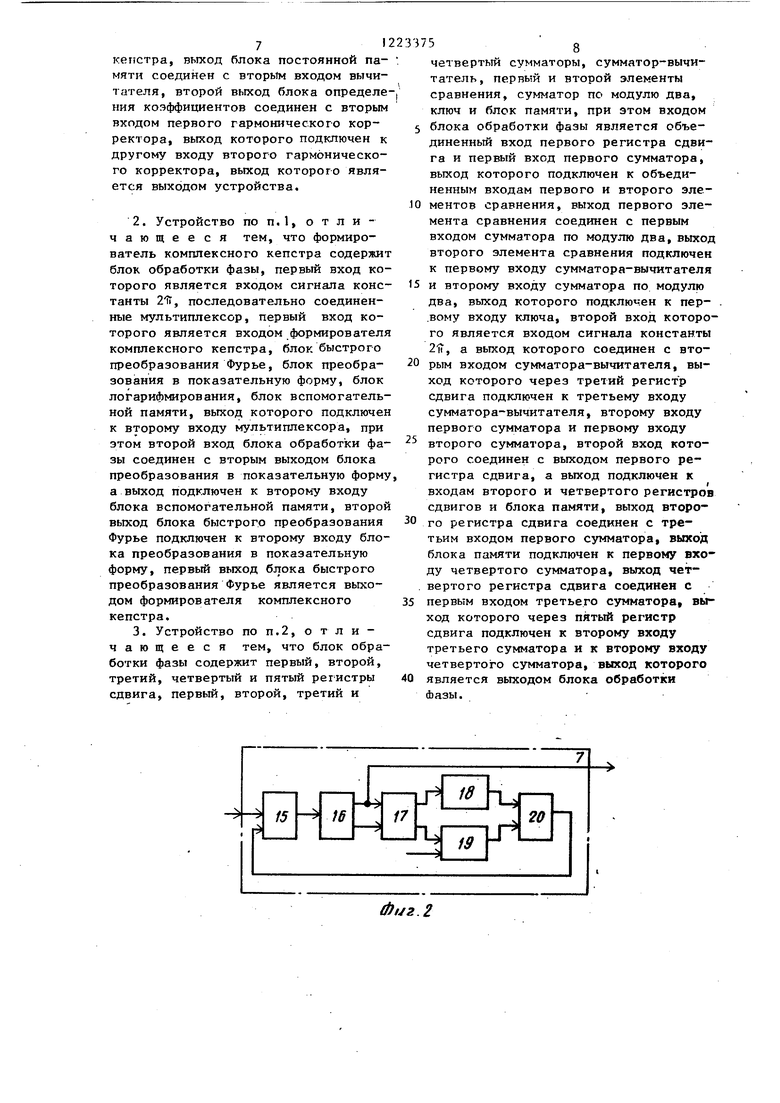

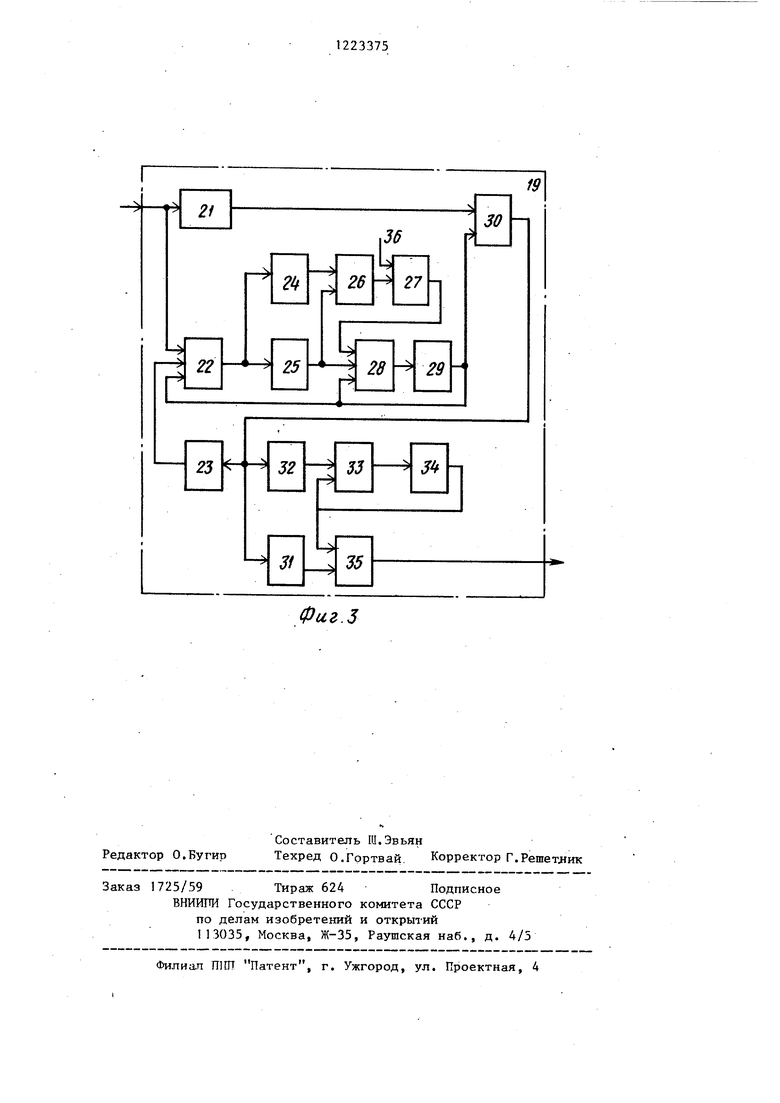

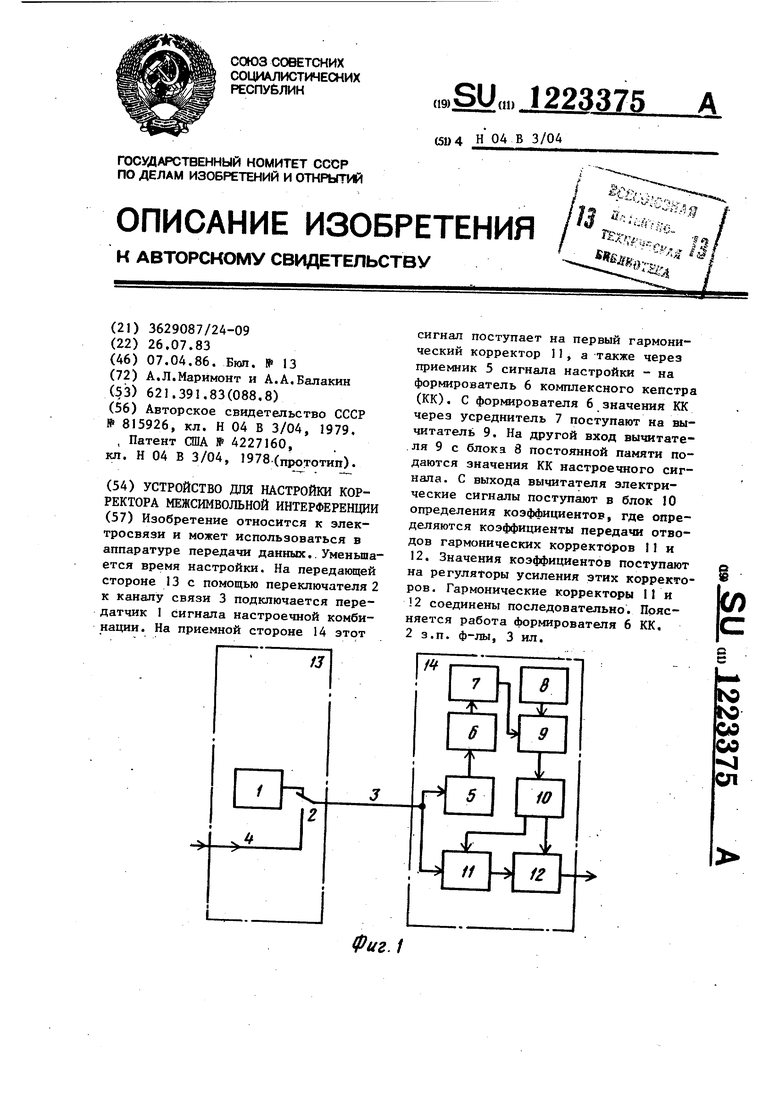

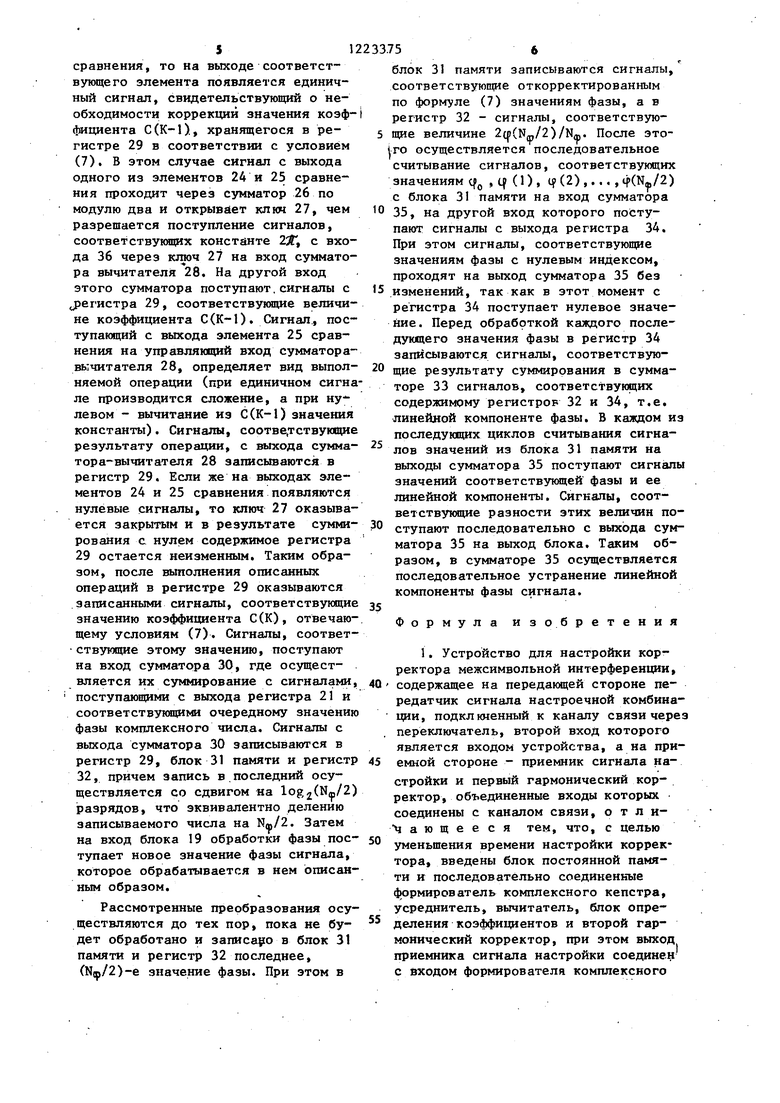

На фиг.1 представлена структурная электрическая схема устройства для . настройки корректора межсимвольной интерференции; на фиг.2 - структур- ная электрическая схема формировате- ji комппексного кепстра; на фиг.З - электрическая структурная схема блока обработки фазы.

Устройство для настройки коррек- тора МСИ содержит передатчик 1 сигнала настроечной комбинации, переключатель 2, подключенный к входу канала 3 связи, вход 4 устройства, .приемник 5 сигнала настройки, формирователь 6 комплексного кепстра (КК), усреднитель 7, блок 8 постоянной памяти, вы читатель 9, блок 10 определения коэффициентов, первый гармонический корректор 11, второй гармонический кор- ректор 12, передающую сторону 13 и приемную сторону 14.

Формирователь 6 КК содержит мультиплексор 15, блок 16 быстрого преобразования Фурье, блок 17 преобразо ванйя в показательную форму, блок 18 логарифмирования, блок 19 обработки фазы, блок 20 вспомогательной памяти

Блок 19 обработки фазы содержит первый регистр 21 сдвига, первый сум матор 22, второй регистр 23 сдвига, первый элемент 24 сравнения, второй элемент 25 сравнения, сумматор 26 по модулю два, ключ 27, сумматор-вычита тель 28, третий регистр 29 сдвига, второй сумматор 30, блок 31 памяти, четвертый регистр 32 сдвига, третий сумматор 33, пятый регистр 34 сдвига четвертый сумматор 35, вход 36 сигнала константы 2 ii .

УстройствЬ для настройки корректора МСИ работает следующим образом.

При необходимости настройки первого и второго гармонических корректо- ров 11 и 12 на передающей стороне 13 переключатель 2 подключает к каналу ,3 связи передатчик 1 сигнала настро- ечной комбинации, чем обеспечивается

передача в канал 3 связи электрического сигнала, соответствующего комбинации настройки устройства.

На приемной стороне 14 этот сигнал поступает в приемник 5 сигнала настройки, где в отсчетные моменты времени осуществляется его квантова- ние по уровню. Электрические сигналы соответствующие квантованному значению сигнала в отсчетные моменты вре- мени (в дальнейшем по тексту - отсчеты сигнала), с выхода приемника 5 сигнала настройки поступают в формирователь 6 КК который на их основе определяет значение КК принятого сигнала, а затем через усреднитель 7 поступают на вход вычитателя 9, на другой вход которого с блока 8 постоянной памяти подаются соответствующие значения КК настроечного сигнала

При этом на выходе вычитателя 9 в соответствии с выражением

г(п) х(п) - d

(п)

(1)

формируются электрические сигналы, соответствующие отсчетам КК импульсной характеристики канала 3 связи, которые поступают в блок 10 определения коэффициентов усиления гармонических корректоров 1 1 и 12.В выражении (,) приняты следующие обозначения-.

.

г(п)

d(n) х(п)

КК последовательности отсчетов входного сигнала;

КК сигнала настройки d(n);

последовательность отсчетов входного си-гнала КК, следующих через Т секунд. Б блоке 10 определения коэффициентов осуществляется преобразование сигналов и определяются значения коэффициентов передачи отводов гармонических корректоров 11 и 12 в со отз(етствии с формулами

Г

(2)

n-fc

(3)

К-П

ТДе Ъ, - коэффициенты передачи отводов первого гармонического корректора 11; С - коэффициенты передачи отводов BTopoi o гармонического корректора 12. Значения коэффициентов передачи отводов, определенные по формулам (2) и (3), поступают на регуляторы усиления отводов этих корректоров. После установки значений всех коэффициентов передачи отводов гармонических корректоров 11 и 12 (настройки устройства) переключатель 2 подключает к входу канала 3 связи вход 4, чем обеспечивается возможность передачи информации.

Формирователь 6 КК, реализованный в соответствии с фиг.2, позволяет вычислить КК за конечный промежуток времени с достаточной точностью следующим образом.

Отсчеты исходного сигнала через мультиплексор 15 записываются/в блок

16быстрого преобразования Фурье, в котором осуществляется определение

значений коэффициентов Фурье входной последовательности, причем каждый из

отсчетов представляется в виде пары значений, являющихся вещественной и мнимой частями комплексного коэффици-. ента Фурье. По окончании вычислений каждый из отсчетов передается в блок

17преобразования в показательную орму, где осуществляется их преобразование из алгебраической в показательную форму, т.е. осуществляется- преобразование пары ансамблей,, соответствующих показательной форме чиса. В результате подобного преобразования на одном выходе блока 17 преобразования в показательную форму (соединенном с блоком 18 логарифмирования) появляются сигналы, отображаюие модуль данного значения коэффициента Фурье, а на другом выходе - сигналы, отображающие его фазу. В блоке 18 логарифмирования осуществляется логарифмирование значений модуя последовательности отсчетов, и игналы, соответствующие значениям огарифма модуля, записываются в сответствующие ячейки блока 20 вспомогательной памяти. Одновременно в блое 19 обработки фазы осуществляется реобразование последовательности значений фазы с целью устранения разывов фазовой кривой.

Сигналы, соответствующие преобразованным значениям фазы, также записываются в блок 20 вспомогательной памяти. Затем отсчеты комплексного 5 логарифма из блока- 20 вспомогательной памяти через мультиплексор 15 переписываются в блоке 16 быстрого преобразования Фурье, где осуществляется операция обратного преобразова0 ния Фурье. По окончании преобразования осуществляется считывание полученных значений отсчетов КК из блока 16 быстрого преобразования Фурье, и сигналы, им соответствующие, посту5 пают с выхода этого блока на выход формирователя 6 комплексного кепстра. Блок 19 обработки фазы (фиг.З) работает следующим образом.

В исходном состоянии все регистры

0 и блок 31 памяти обнулены. На вход блока 19 обработки фазы последовательно, поступают сигналы, соответствующие значениям фаз от счетов, начиная с Р(о) и кончая P(N(p/2). Очеред5 ное значение фазы Р(К) записывается .в регистр 21 и поступает на вход сумматора 22, где из него вычитается предыдущее значение фазы, поступающее на другой вход .сумматора 22 из

0 регистра 23, а также значение поправочного коэффициента С(К-1), поступающее на третий вход сумматора 22 из регистра 29. При этом поправочный коэффициент С(К-1) определяется из J условия

О, Ьри К О

C(k) {

С(К-1)-2Т, при Р(К)-Р(К-1)51Г С (К-1)+2-4-, при P(K-I)-P(K)ir(7). С(К-1) .

в остальных случаях,

с)

где Р(К) - последовательность отсче гов фазы.

В результате на выходе первого

сумматора 22 формируются сигналы,

соответствующие разности

Р(К) - С(К-1) - Cf(P-l)P(K) - Р(К-1),

и поступгиощие в элементы 2А и 25 . сравнения. В элементе 24 сравнения осуществляется сравнение поступивших сигналов с сигналами константы , а в элементе 25 сравнения - с сигнаани константы . Если значение входных сигналов превышает значение константы в элементе 24 сравнения или меньше константы в элементе 25

$1

сравнения, то на выходе соответствующего элемента появляется единичный сигнал, свидетельствующий о необходимости коррекций значения коэффициента С(К-1)., хранящегося в регистре 29 в соответствии с условием (7). В этом случае сигнал с выхода одного из элементов 24 и 25 сравнения проходит через сумматор 26 по модулю два и открывает ключ 27, чем разрешается поступление сигналов, соответствующих константе 23Г, с входа 36 через ключ 27 на вход сумматора вычитателя 28. На другой вход этого сумматора поступают.сигналы с регистра 29, соответствующие величине коэффициента С(К-1), Сигнал, поступающий с выхода элемента 25 сравнения на управляющий вход сумматора

5 изменений, так как в этот момент с регистра 34 поступает нулевое значение. Перед обработкой каящого последующего значения фазы в регистр 34 записываются сигналы, соответствуювычитателя 28, определяет вид выпол- 20 щие результату суммирования в сумма- няемой операции (при единичном сигна- оре 33 сигналов, соответствующих ле производится сложение, а при нулевом - вычитание из С(К-1) значения

содержимому регистров 32 и 34, т.е. линейной компоненте фазы. В каждом и последующих циклов считывания сигналов значений из блока 31 памяти на выходы сумматора 35 поступают сигналы значений соответствующей фазы и ее линейной компоненты. Сигналы, соответствующие разности этих величин по ступают последовательно с выхода сум матора 35 на выход блока. Таким образом, в сумматоре 35 осуществляется последовательное устранение линейной компоненты фазы сигнала.

константы). Сигналы, соотве,тствукяще результату операции, с выхода сумма- тора-вычитателя 28 записываются в регистр 29. Если же на выходах элементов 24 и 25 сравнения появляются нулевые сигналы, то ключ 27 оказывается закрытым и в результате суммирования с нулем содержимое регистра 29 остается неизменным. Таким образом, после выполнения описанных операций в регистре 29 оказываются записанными сигналы, соответствующие значению коэффициента С(К), отвечающему условиям (7). Сигналы, соответ- ствующие этому значению, поступают на вход сумматора 30, где осуществляется их суммирование с сигналам;, поступающими с выхода регистра 21 и соответствукяцими очередному значению фазы комплексного числа. Сигналы с выхода сумматора 30 записываются в регистр 29, блок 31 памяти и регистр 32, причем запись в последний осуществляется со сдвигом яа log2() разрядов, что эквивалентно делению записываемого числа на N«,/2. Затем на вход блока 19 обработки фазы поступает новое значение фазы сигнала, которое обрабатывается в нем описанным образом.

Рассмотренные преобразования осуществляются до тех пор, пока не будет обработано и записало в блок 31 памяти и регистр 32 последнее, (Nep/2)-e значение фазы. При этом в

блок 31 памяти записываются сигналы, соответствующие откорректированным по формуле (7) значениям фазы, а в регистр 32 - сигналы, соответствуюие величине 2q)(Nm/2)/Nm. После это- го осуществляется последовательное считывание сигналов, соответствующих значениям , ty (1), q(2),... ,ip() с блока 31 памяти на вход сумматора

35, на другой вход которого поступают сигналы с выхода регистра 34. При этом сигналы, соответствующие значениям фазы с нулевым индексом, проходят на выход сумматора 35 без

изменений, так как в этот момент с регистра 34 поступает нулевое значение. Перед обработкой каящого последующего значения фазы в регистр 34 записываются сигналы, соответствующие результату суммирования в сумма- оре 33 сигналов, соответствующих

щие результату суммирования в сумма- оре 33 сигналов, соответствующих

содержимому регистров 32 и 34, т.е. линейной компоненте фазы. В каждом из последующих циклов считывания сигналов значений из блока 31 памяти на выходы сумматора 35 поступают сигналы значений соответствующей фазы и ее линейной компоненты. Сигналы, соответствующие разности этих величин поступают последовательно с выхода сумматора 35 на выход блока. Таким образом, в сумматоре 35 осуществляется последовательное устранение линейной компоненты фазы сигнала.

Формула изобретения

1. Устройство для настройки корректора межсимвольной интерференции, содержащее на передающей стороне передатчик сигнала настроечной комбинации, подклиненный к каналу связи через переключатель, второй вход которого является входом устройства, а на приемной стороне - приемник сигнала настройки и первый гармонический корректор, объединенные входы которых соединены с каналом связи, о т л и- ающееся тем, что, с целью уменьшения времени настройки корректора, введены блок постоянной памяти и последовательно соединенные формирователь комплексного кепстра, усреднитель, вычитатель, блок определения коэффициентов и второй гармонический корректор, при этом выход приемника сигнала настройки соединен с входом формирователя комплексного

кепстра, выход блока постоянной па- мятн соединен с вторым входом вычи- тателя, второй выход блока определе ния коэффициентов соединен с вторым входом первого гармонического корректора, выход которого подключен к другому входу второго гармонического корректора, выход которого является выходом устройства,

2.Устройство по п.1, о т л и - чающееся тем, что формирователь комплексного кепстра содержит блок обработки фазы, первый вход которого является входом сигнала константы 21Т, последовательно соединенные мультиплексор, первый вход которого является входом формирователя комплексного кепстра, блок быстрого преобразования Фурье, блок преобразования в показательную форму, блок логарифмирования, блок вспомогательной памяти, выход которого подключен к второму входу мультиплексора, при этом второй вход блока обработки фазы соединен с вторым выходом блока преобразования в показательную форму а выход подключен к второму входу блока вспомогательной памяти, второй выход блока быстрого преобразования Фурье подключен к второму входу блока преобразования в показательную форму, первый выход блока быстрого преобразования Фурье является выходом формирователя комплексного кепстра.

3.Устройство по п.2, о т л и - чающееся тем, что блок обработки фазы содержит первый, второй, третий, четвертый и пятый регистры сдвига, первый, второй, третий и

четвертый сумматоры, сумматор-вычи- татель, первый и второй элементы сравнения, сумматор по модулю два, ключ и блок памяти, при этом входом 5 блока обработки фазы является объединенный вход первого регистра сдвига и первый вход первого сумматора, выход которого подключен к объединенным входам первого и второго эле10 ментов сравнения, выход первого элемента сравнения соединен с первым входом сумматора по модулю два, выход второго элемента сравнения подключен к первому входу сумматора-вычитателя

5 и второму входу сумматора по модулю два, выход которого подключен к пер- . .вому входу ключа, второй вход которого является входом сигнала константы 2, а выход которого соединен с вто0 рым входом сумматора-вычитателя, выход которого через третий регистр сдвига подключен к третьему входу сумматора-вычитателя, второму входу первого сумматора и первому входу

5 второго сумматора, второй вход которого соединен с выходом первого регистра сдвига, а выход подключен к входам второго и четвертого регистров сдвигов и блока памяти, выход второ0 го регистра сдвига соединен с третьим входом первого сумматора, выход блока памяти подключен к первому входу четвертого сумматора, выход четвертого регистра сдвига соединен с

5 первым входом третьего сумматора, выход которого через пятый регистр сдвига подключен к второму входу третьего сумматора и к второму входу четвертого сумматора, выход которого 0 является выходом блока обработки (Ьазы.

Л и г. 2

Фиг.5

Редактор О.Бугир

Составитель Ш.Эвьян

Техред О.Грртвай. Корректор Г.Решетлик

1725/59 . Тираж 624 Подписное ВНИИШ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиап тШ Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| Устройство для измерения относительной задержки импульсных сигналов | 1982 |

|

SU1068886A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Формирователь многочастотного сигнала | 1986 |

|

SU1401554A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Процессор дискретного преобразования Фурье | 1986 |

|

SU1361574A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

Изобретение относится к электросвязи и может использоваться в аппаратуре передачи данных.. Уменьшается время настройки. На передающей стороне 13 с помощью переключателя 2 к каналу связи 3 подключается передатчик 1 сигнала настроечной комбинации. На приемной стороне 14 этот сигнал поступает на первый гармонический корректор 11, а также через приемник 5 сигнала настройки - на формирователь 6 комплексного кеПстра (КК). С формирователя 6 значения КК через усреднитель 7 поступают на вы- читатель 9. На другой вход вычитате- ля 9 с блока 8 постоянной памяти подаются значения КК настроечного сигнала. С выхода вычитателя электрические сигналы поступают в блок 10 определения коэффициентов, где определяются коэффициенты передачи отводов гармоиических корректоров 1 I и 12. Значения коэффициентов поступают на регуляторы усиления этих корректоров. Гармонические корректоры Пи 2 соединены последовательно. Поясняется работа формирователя 6 КК. 2 з.п. ф-лы, 3 ил. ue.f

| Устройство автоматической настройкигАРМОНичЕСКОгО KOPPEKTOPA | 1979 |

|

SU815926A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| , Патент США 4227160, кп | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-07—Публикация

1983-07-26—Подача