Изобретение относится к вычислительной технике и предназначено для построения специализированных уст- .ройств, -работающих в реальном времени .

Цель изобретения - расширение области применения за счет вычисления интеграла частного.

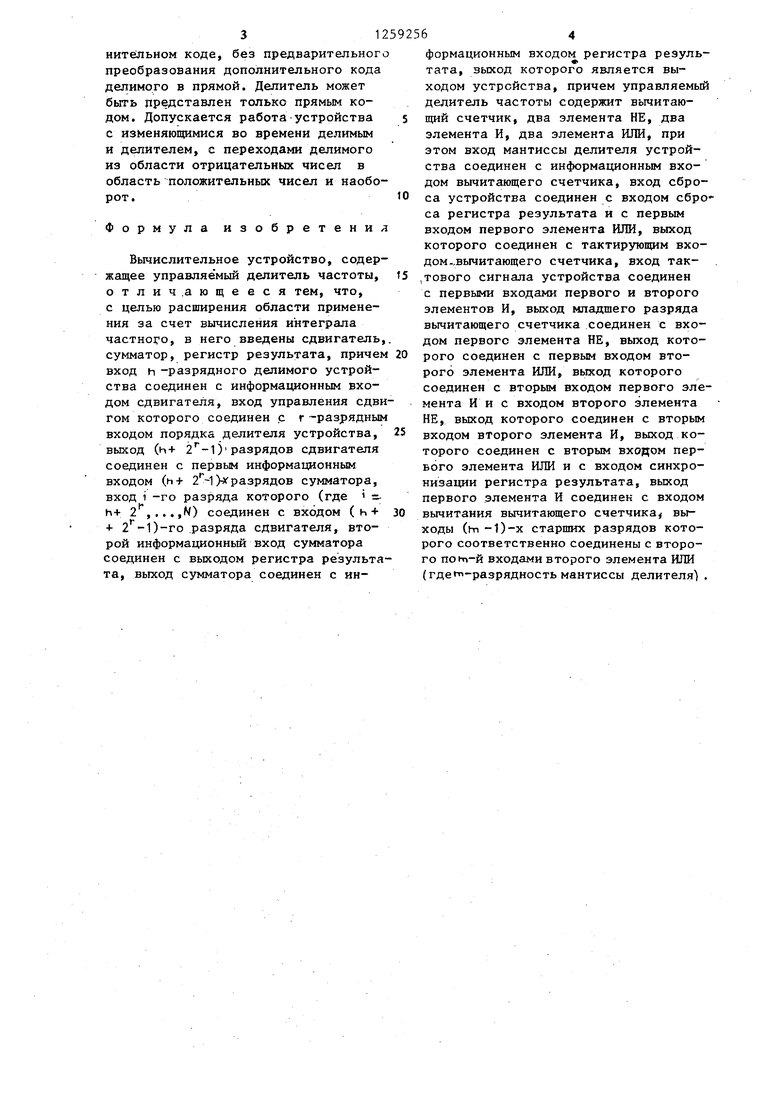

На чертеже представлена функциональная схема .вычислительного устройства.

Устройство содержит сдвигатель 1, су1мматор 2, регистр 3 результата, управляемый делитель 4 частоты, вход 5 делимого, вход 6 порядка делителя вход 7 мантиссы делителя, вход 8 тактового сигнала, вход 9 сигнала сброс и выход 10. Управляемый де- лртель 4 частоты содержит второй и первый элементы НЕ 11 и 12, второй и первый элементы И 13 и 14, первьй и второй элементы ИЛИ 15 и 16 и двоичный вычитающий счетчик 17,

Деление чисел в устройстве осуществляется следующим образом.

На первом этапе выполняется деление делимого.А на 2 , где R - порядок делителя В, Полученная величина Л2 суммируется с содержимым

накапливаемого сумматора с частотой суммирований f мантисса делителя В ; { - тактовая часI)

тота, которая выбирается равной 2 Гц В накапливающем сумматоре формируется код С, изменение которого описывается выражением

t -R к t г Г H J dt-f9.

- W ъ

оо

dt

Вычисляя определенный интеграл в интервале времени , получаем

с--г

к-Р

А

Коэффициент постоянен и может быть учтен при съеме информации за счет соответствующего распределения весов в,выходном двоичном коде либо

R

за счет подачи кода А- 2 на вход накапливающего сумматора со сдай-

К. Р

гом на 2 в сторону младяшх разрядов, В общем случае делимое и делитель могут быть функциями времени

После включения устройства на вх 9 Сброс подается импульсный сиг- нал, а на входах 5-7 присутствуют нулевые коды, при этом регистр 3 результата устанавливается в нулевое

S

0

5

0

5

0

5

0

5

состояние и ka выходах 10 устройства поддерживается нулевой код. При подаче на вход 5 кода делимого, на вход 6 кода порядка делитапя, на вход 7 кода мантиссы делителя., а на вход 9 сигнала Сброс начинается вычислительный процесс. Как д(1пимого поступает на информахщонные входы сд;ви- гателя 1. На управляющие входы сдви- гателя 1 подается код порядка делителя, а на входные каналы - разряды кода делимого. При подаче на управляющие входы сдвигателя кода порядка делителя, например кода 1001, код делимого сдвигается в сторону младших разрядов на величину кода порядка, в данном случае на 9 разрядов j т.е, осуществляется деление кода делимого на 2. Код с выхода сдвигателя 1 поступает на сумматор 2, разрядность N которого должна быть больше I (где t - разрядность кода порядка; н - разрядность кода делимого;,определяется максимальным значением интеграла, которое может быть получено в реальном устройстве. На старшие N-E входов сумматора по первому слагаемому пода- ется сигнал с ()-го выхода сдвигателя 1, Сумматор 2 и регистр 3 результата, замкнутые в кольцо, образуют накапливающий сумматор, Регистр

3срабатьшает по заднему фронту сигнала на синхровходе, который поступает с управляемого делителя 4 частоты. При подаче на с вход вычитающего счетчика 17 иьшульсного сигнала по его заднему фронту Е; счетчик записывается код мантиссы делителя. Тактовые импульсы поступают через элемент И 14, разрешающий единичным сигналом с выхода элемента ИЛИ 16, на вычитающий вход счетчика, обеспечивая изменение кода по заднему фронту счетного импульса в сторону уменьшения. Когда код в счетчике станет равным единице, на выходе элемента И.ПИ 16 появляется нулевой сигнал, запрещающий дальнейший счет счетчика и разрешающий запись в счетчик 1 7 кода мантиссы делит аля. Время счета счетчика 17 пропорционально мантиссе делителя, а частота импульсов на выходе управляемого делителя

4частоты - обратно пропоргдюнальна. При отрицательном делимом, заданном . дополнительным кодом, устройство формирует результат также в дополнительном коде, без предварительного преобразования дополнительного кода делимого в прямой. Делитель может быть представлен только прямым кодом. Допускается работа устройства с изменяющимися во времени делимым и делителем, с переходами делимого из области отрицательных чисел в область положительных чисел и наоборот.

Формула изобретения

Вычислительное устройство, содержащее управляемый делитель частоты, отлич.ающееся тем, что, с целью расширения области применения за счет вычисления интеграла частно 7о, в него введены сдвигатель, сумматор, регистр результата, причем вход h -разрядного делимого устройства соединен с информационным входом сдвигателя, вход управления сдвигом которого соединен с г-разрядным входом порядка делителя устройства, выход (h+ ) разрядов сдвигателя соединен с первым информационньм входом (h+ ) разрядов сумматора, вход i -го разряда которого (где h+ N) соединен с входом ( Ы-

4- )-го .разряда сдвигателя, второй информационный вход сумматора соединен с выходом регистра результата, выход сумматора соединен с информационным входом регистра результата, выход которого является выходом устройства, причем управляемый делитель частоты содержит вычитающий счетчик, два элемента НЕ, два элемента И, два элемента ИЖ, при этом вход мантиссы делителя устройства соединен с информационным входом вычитающего счетчика, вход сброса устройства соединен с входом сбро са регистра результата и с первым входом первого элемента ИЛИ, выход которого соединен с тактирующим входом -.вычитающего счетчика, вход так- ,тового сигнала устройства соединен с первыми входами первого и второго элементов И, выход младшего разряда вычитающего счетчика соединен с входом первого элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и с входом второго элемента НЕ, выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ и с входом синхронизации регистра результата, выход первого элемента И соединен с входом вычитания вычитающего счетчика выходы (in -1)-х старших разрядов которого соответственно соединены с второго nofTi-й входами второго элемента ИЛИ (гдеи -разрядность мантиссы делителя) .

Гг

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

Изобретение относится к области вычислительной техники, предназначено для специализированных вычислителей, работающих в реальном времени, в. частности интерполяторов, и обеспечивает интегрирование частного или выполнение операции деления. Код делимого, проходя через сдвигатель, сдвигается в сторону младших разрядов на величину порядка делителя и поступает на накапливаюпщй сумматор, выполненный на регистре и сумматоре. Частота суммирований в накапливающем сумматоре задается выходным сигналом делителя частоты, управляемого мантиссой делителя. Перед началом вычислений осуществляется сброс устройства в исходное состояние. 1 ил. э ел to сд о

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1982 |

|

SU1064279A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-04-17—Подача