Изобретение относится к вычислительной технике и может быть применено при построении запоминающих устройств ОЗУ) .

Цель изобретения - повышение надежности устройства.

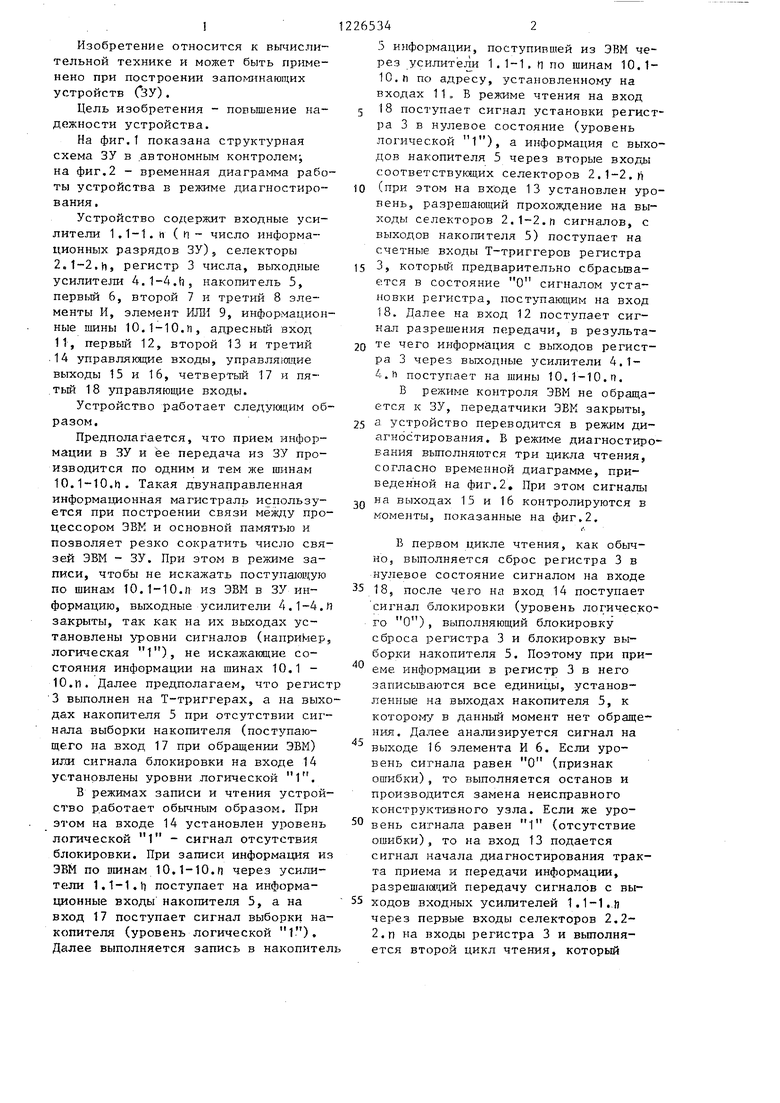

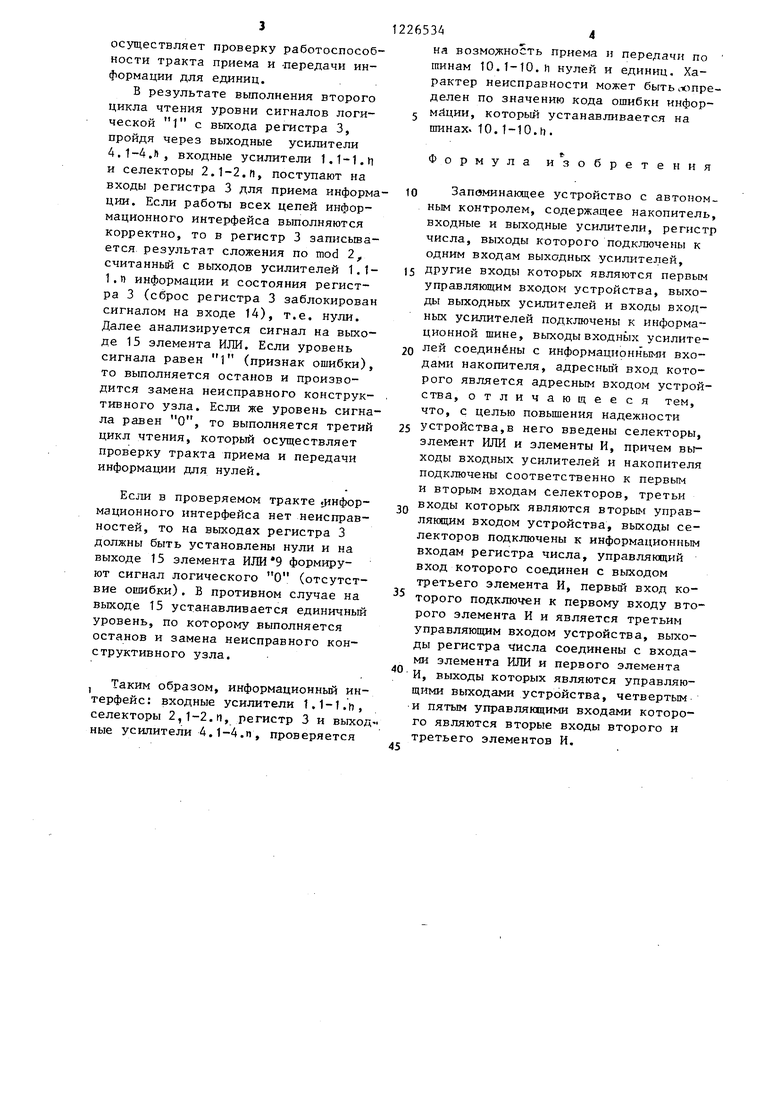

На фиг.1 показана структурная схема ЗУ в .автономным контролем; на фиг.2 - временная диаграмма работы устройства в режиме диагностирования.

Устройство содержит входные усилители 1.1-1.Н (h- число информационных разрядов ЗУ)5 селекторы 2.1-2.и, регистр 3 числа, выходные усилители 4.1-A.fi, накопитель 5, первый 6, второй 7 и третий 8 элементы И, элемент ИЛИ 9, информационные шины 10.1-10.И, адресный вход 11, первьй 12, второй 13 и третий .14 управляющие входы, управлягадие выходы 15 и 16, четвертый 17 и пя- ,тый 18 управляющие входы.

Устройство работает следугацим образом.

Предполагается, что прием информации в ЗУ и ее передача из ЗУ производится по одним и тем же шинам 10.1-10.h. Такая двунаправленная информагз юнная магистраль используется при построении связи между процессором ЭВМ и основной памятью и позволяет резко сократить число связей ЭВМ - ЗУ. При этом в режиме записи, чтобы не искажать поступающую по шинам 10.1-10.П из ЭВМ в ЗУ информацию, выходные усилители 4.1-4.Н закрыты, так как на их выходах установлены уровни сигналов (наприЬзер, логическая 1), не искажагадие состояния информации на шинах 10.1 - 10.п. Далее предполагаем, что регист 3 выполнен на Т-триггерах, а на выходах накопителя 5 при отсутствии сигнала выборки накопителя (поступающего на вход 17 при обращении ЭВМ) и;:си сигнала блокировки на входе 14 установлены уровни логической 1.

В режимах записи и чтения устройство работает обычным образом. При этом на входе 14 установлен уровень логической 1 - сигнал отсутствия блокировки. При записи информация и ЭВМ по пшнам 10.1-10.Ц через усилители 1,1-1.ti поступает на информационные входы накопителя 5, а на вход 17 поступает сигнал выборки накопителя (уровень логической 1). Далее выполняется запись в накопите

5 информации, поступившей из ЭВМ через усилители 1.1-1, П по шинам 10.1- 10.п по адресу, установленному на входах 11„ Б реяшме чтения на вход 18 поступает сигнал установки регистра 3 в нулевое состояние (уровень логической 1), а информация с выходов накопителя 5 через вторые входы соответствующих селекторов 2.1-2. (при этом на входе 13 установлен уровень, разрешающий прохождение на выходы селекторов 2.1-2. сигналов, с выходов накопителя 5) поступает на счетные входы Т-триггеров регистра

3, которьш предварительно сбрасьгоа- ется в состояние О сигналом установки регистра, поступающим на вход 18. Далее на вход 12 поступает сигнал разрешения передачи, в результате чего информация с выходов регистра 3 через выходные усилители 4.1- 4.м поступает на шины 10.1-10.п.

В режиме контроля ЭВМ не обращается к ЗУ, передатчики ЭВМ закрыты, а устройство переводится в режим диагностирования, В режиме диагностирования выпО Лняются три цикла чтения, согласно временной диаграмме, приведенной на фиг.2, При этом сигналы на выходах 15 и 16 контролируются в моменты, показанные на фиг.2.

В первом цикле чтения, как обычно, выполняется сброс регистра 3 в нулевое состояние сигналом на входе

18, после чех о на вход 14 поступает сигнал блокировки (уровень логического О), выполняющий блокировку сброса регистра 3 и блокировку выборки накопителя 5. Поэтому при приеме информации в регистр 3 в него записьшаются все единицы, установенные на выходах накопителя 5, к котором: г в данньй момент нет обращения. Далее анализируется сигнал на ыходе 16 элемента И 6. Если уровень сигнала равен О (признак ошибки), то выполняется останов и производится замена неисправного конструктивного узла. Если же уровень сигнала равен 1 (отсутствие ошибки), то на вход 13 подается сигнал начала диагностирования тракта приема и передачи информации, разрешагаций передачу сигналов с выходов входных усилителей 1.1-1.,li через первые входы селекторов 2.2- 2.П на входы регистра 3 и вьшолня- ется второй цикл чтения, который

осуществляет проверку работоспособности тракта приема и -передачи информации для единиц.

В результате выполнения второго цикла чтения уровни сигналов логической 1 с выхода регистра 3, пройдя через выходные усилители 4.1-4.и, входные усилители 1.1-1.и и селекторы 2.1-2.П, поступают на входы регистра 3 для приема информации. Если работы всех цепей информационного интерфейса выполняются корректно, то в регистр 3 записьша- ется результат сложения по mod 2 считанный с выходов усилителей 1.1- 1.п информации и состояния регистра 3 (сброс регистра 3 заблокирован сигналом на входе 14), т.е. нули. Далее анализируется сигнал на выходе 15 элемента ИЛИ. Если уровень сигнала равен 1 (признак ошибки), то выполняется останов и производится замена неисправного конструктивного узла. Если же уровень сигнала равен О, то выполняется третий цикл чтения, которьй осуществляет проверку тракта приема и передачи информации для нулей.

Если в проверяемом тракте «информационного интерфейса нет неисправностей, то на выходах регистра 3 должны быть установлены нули и на выходе 15 элемента формируют сигнал логического О (отсутствие ошибки). Б противном случае на выходе 15 устанавливается единичный уровень, по которому выполняется останов и замена неисправного конструктивного узла.

J Таким образом, информационный интерфейс: входные усилители 1.1-1.h, селекторы 2,1-2.и, регистр 3 и выхоные усилители 4.1-4.п, проверяется

2265344

на возможность приема и передачи по тинам 10.1-10.h нулей и единиц. Характер неисправности может бытьсюпре- делен по значению кода ошибки инфор- г мйции, который устанавливается на пганах. 10.1-10.И.

Формула изобретения

10 Запоминающее устройство с автономным контролем, содержащее накопитель, входные и выходные усилители, регистр числа, выходы которого подк.пючены к одним входам выходных усилителей,

15 другие входы которых являются первым управляющим входом устройства, выходы выходных усилителей и входы входных усилителей подключены к информационной шине, выходы входных усилите20 лей соединены с информационным1т входами накопителя, адресный вход которого является адресным входом устройства, отличающееся тем, что, с целью повышения надежности

25 устройства,в него введены селекторы, злемент ИЛИ и элементы И, причем выходы входных усилителей и накопителя подключены соответственно к первым и вторым входам селекторов, третьи

,,, входы которых являются вторым управ- лякщим входом устройства, выходы селекторов подключены к информационным входам регистра числа, управляющий вход которого соединен с выходом третьего элемента И, первый вход которого подключен к первому входу второго элемента И и является третьим управляющим входом устройства, выходы регистра числа соединены с входами элемента ИЛИ и первого элемента И, выходы которых являются управляющими выходами устройства, четвертым и пятым управляющими входами которого являются вторые входы второго и третьего элементов И.

35

40.

45

, Второй Третий Первый и,икл и,икл fme l4ifкл чте- паи нт щнтроля сигнала чтений ния

Составитель О.Кулаков Редактор Н.Яцола Техред И.Погюв№1 Корректор. С.Шекмар

Заказ 2140/52 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,-Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие г. Ужгород, ул. Проектная, 4

Фиг. Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1065884A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| Запоминающее устройство с контролем | 1989 |

|

SU1624535A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ПОВЫШЕННОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1992 |

|

RU2039374C1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Запоминающее устройство с исправлением информации в отказавших разрядах | 1986 |

|

SU1317487A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении надежных запоминающих устройств. Целью изобретения является повышение на.дежности устройства. Устройство содержит входные усилители, селекторы, регистр числа, выходные усилители, накопитель, элементы И, элемент ИЛИ, информационные шины. Надежность устройства повышается за счет осуществления режима диагностирования, который осуществляется за три цикла чтения. При отсутствии ошибок в информационном тракте на выходе элемента ИЛИ формируется сигнал логического О. 2 ил. (Л с:

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-23—Публикация

1984-08-31—Подача