Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей двоичных кодов в коды с ограниченным или постоянным весом. I.

Целью изобретения является расширение класса решаемых задач за счет возможности преобразования двоичного код в код с ограниченным весом.

Преобразование двоичных кодов с ограниченным весом (количество единиц в коде может быть от О до. р) соответствует переводу числа из позиционной системы счисления в код веса разрядов которого определяются выражением

)

2

при

(Рп,-р1 ,

П с

h при ,

(1)

твес п-го разряда преобразуемого числа при наличии р единиц,в старших перед ним разрядах;

количество единиц в коде каждого сообщения (характеристике ограничения на вес). ование двоичных кодов с весом соответствует переиз позиционной системЬ веса разрядов которой опследзтощим образом:

О

,(Рш-р)

при при Р5Р -п.

(2)

В преобразователе используется возможность вычисления по (p,+t) весовым коэффициентам разрядов: (f(n,,0), ((, 1), ({i(nj-2, 2), ..., (f(n,-p, р„) для любого п,% р„, соответствующего ряда коэффициентов для n/j, равного п, + 1 ипи , путем простого соответственно сложения шш вычитания смежных коэффициентов из ряда для п,. Эта возможность определена основным свойством фибоначчие- вых систем счисления, которое записывается в виде следующего выражения:

(f(n,p)cf(n, ,p)+(f(n|-1, р+1).

Определение весовых коэффициентов разрядов в процессе преобра зования .начинается со старших разрядов, Заме

ТИМ, что значение

10

«5

1)

20

я, :

40

45

2

tf(n,p)

при

ГП

25

30

35

50

всегда равно 1.

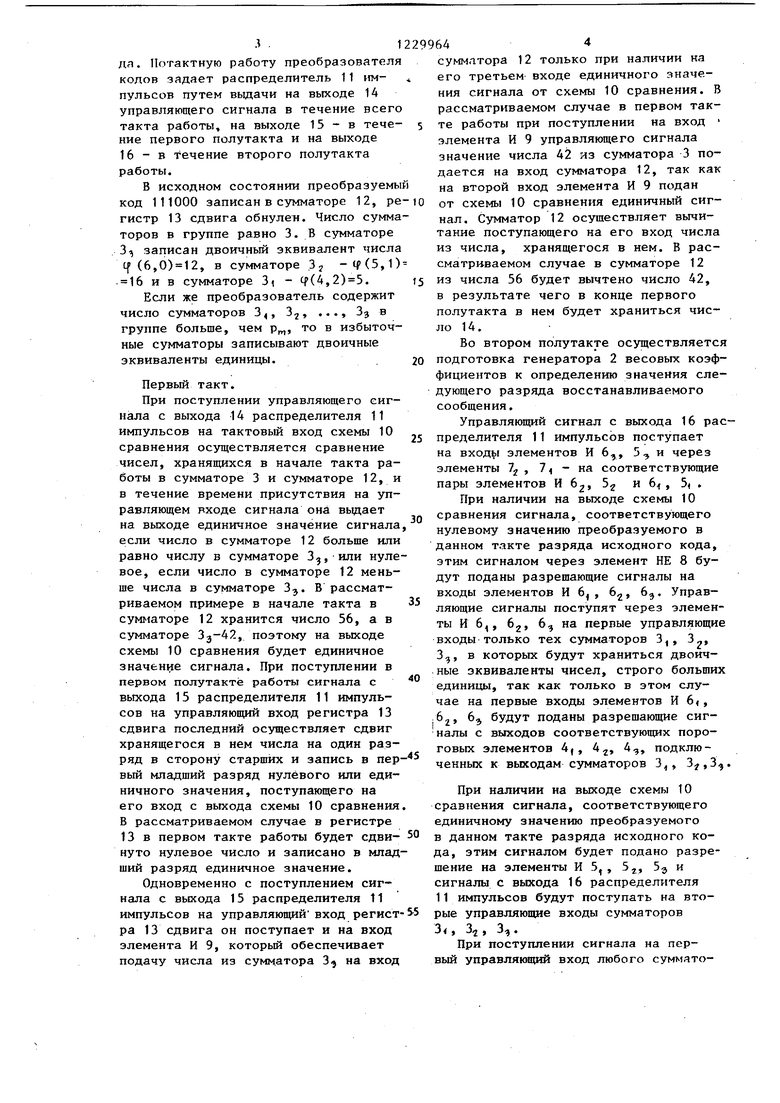

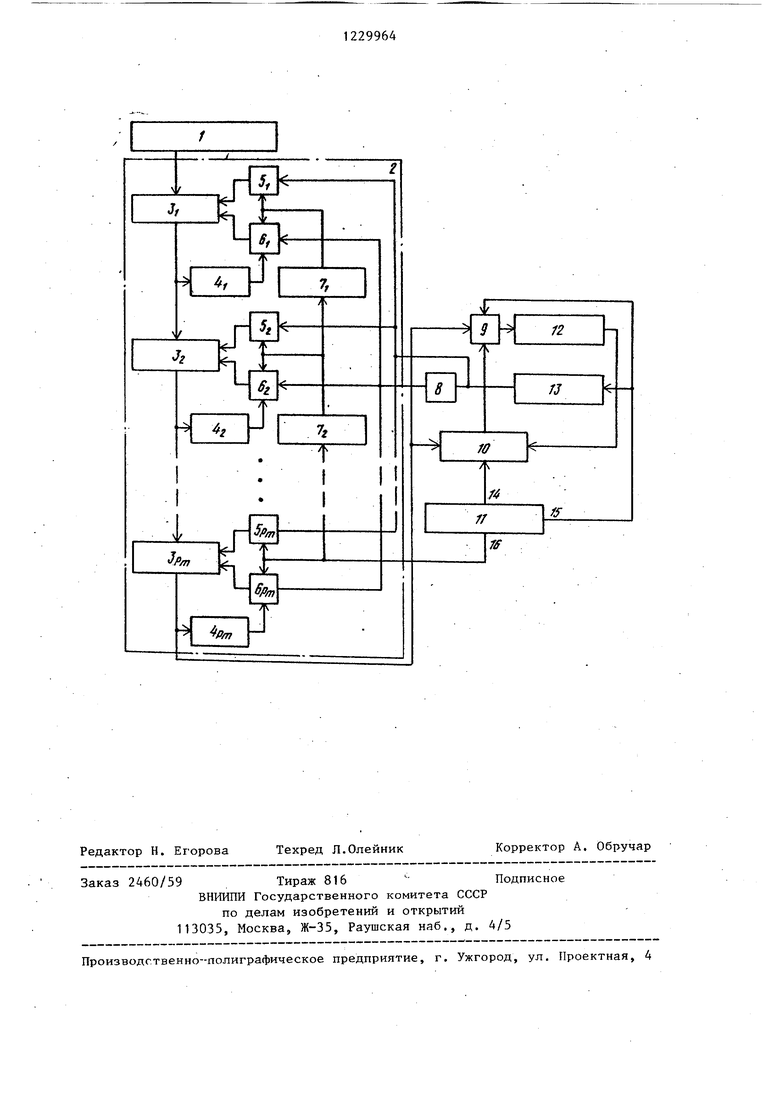

На чертеже представлена структурная схема предлагаемого преобразователя .

Преобразователь содержит регистр 1 весового эквивалента, генератор 2 весовых коэффициентов, включающий в себя группу 3 сумматоров, предназначенных для хранения весовых коэффициентов р, группу А пороговых элементов, первую группу 5 элементов И, вторую группу 6 элементов И, группу 7 элементов задержки, элемент НЕ 8, элемент И 9, схему 10 сравнения, распределитель 11 импульсов, сумматор 12 и регистр 13 сдвига.

В зависимости от числа разрядов в преобразуемом коде (п ), типа ограничения на вес кодов и значения параметра ограничения р осуществляется вычисление значений следующих весовых коэффициентов

.Cf(, ), (р(, ),

..,м (п. О);

в первый сумматор 3 .записывают двоичный эквивалент числа ср(п„-рп,+ 1, ), во второй сумматор 3 - двоичный эквив алент ff(, ) и т.д. В последнем сумматоре 3 записан двоичный эквивалент числа сл(п„, 0), которое является весовым коэффициентом первого старшего разряда преобразуемого кода. В регистре 1 двоичный эквивалент 1 соответствует весу любого разряда при так как всегда (:f(x, ) 1.

Для случая, когда осз ществляется преобразование кода 111000 (56) в код с ограниченньв4 весом, число разрядов в котором равно 7 (п,), а максимально допустимый вес равен 3 (), устройство работает следующим образом. Преобразование осуществляется за число тактов, равное числу разрядов в исходном коде, в рассматриваемом случае за 7 тактов. Каждый такт рабо ты состоит из двух полутактов. Первый полутакт основной (рабочий), в течение которого осуществляется преобразование очередного разряда исходного кода в код с ограниченным весом, а 55 второй полутакт вспомогательный, в течение которого осуществляется вычисление двоичного эквивалента весом .следующего разряда преобразуемого ко

да. Потактную работу преобразователя кодов задает распределитель 11 им- пульсов путем вьщачи на выходе 14 управляющего сигнала в течение всего такта работы, на выходе 15 - в тече- ние первого полутакта и на выходе 16 - в течение второго полутакта работы.

В исходном состоянии преобразуемы код 111000 записан в сумматоре 12, ре гистр 13 сдвига обнулен. Число сумматоров в группе равно 3. В сумматоре З записан двоичный эквивалент числа tf (6,0) 12, в сумматоре 3 -tf(5,1) 16 и в сумматоре 3i - Ч (4,2)5.

Если же преобразователь содержит число сумматоров 3,, 32, ..., Зз в группе больше, чем р, то в избыточные сумматоры записывают двоичные эквиваленты единицы.

Первый такт.

При поступлении управляющего сих- нала с выхода 14 распределителя 11 импульсов на тактовый вход схемы 10 сравнения осуществляется сравнение чисел, хранящихся в начале такта работы в сумматоре 3 и сумматоре 12, и в течение времени присутствия на управляющем входе сигнала она выдает на выходе единичное значение сигнала если число в сумматоре 12 больше шти равно числу в сумматоре 3, или нулевое, если число в сумматоре 12 меньше числа в сумматоре 3. В рассматриваемом примере в начале такта в сумматоре 12 хранится число 56, а в сумматоре Зд-42, поэтому на выходе схемы 10 сравнения будет единичное значение сигнала. При поступлении в первом полутакте работы сигнала с выхода 15 распределителя 11 импульсов на управляюпщй вход регистра 13 сдвига последний осуществляет сдвиг хранящегося в нем числа на один разряд в сторону старших и запись в пер вый младший разряд нулевого или единичного значения, поступающего на его вход с выхода схемы 10 сравнения В рассматриваемом случае в регистре 13 в первом такте работы будет сдви- нуто нулевое число и записано в младший разряд единичное значение.

Одновременно с поступлением сигнала с выхода 15 распределителя 11 импульсов на управляющий вход регист- ра 13 сдвига он поступает и на вход элемента И 9, которьй обеспечивает подачу числа из сумматора 3 на вход

25

5

ю 15

20

3550

30

45

сумматора 12 только при наличии на его третьем входе единичного значения сигнала от схемы 10 сравнения. В рассматриваемом случае в первом такте работы при поступлении на вход элемента И 9 управляющего сигнала значение числа 42 из сумматора 3 подается на вход сумматора 12, так как на второй вход элемента И 9 подан от схемы 10 сравнения единичный сигнал. Сумматор 12 осуществляет вычитание поступающего на его вход числа из числа, хранящегося в нем. В рассматриваемом случае в сумматоре 12 из числа 56 будет вычтено число 42, в результате чего в конце первого полутакта в нем будет храниться число 1 4 .

Во втором полутакте осуществляется подготовка генератора 2 весовых коэффициентов к определению значения следующего разряда восстанавливаемого сообщения.

Управляющий сигнал с выхода 16 распределителя 11 импульсов поступает на входы элементов И 6,, 5 и через элементы 7 , 7, - на соответствующие пары элементов И 62, 5 и 6 , 3 .

При наличии на выходе схемы 10 сравнения сигнала, соответствующего нулевому значению преобразуемого в данном такте разряда исходного кода, этим сигналом через элемент НЕ 8 будут поданы разрешающие сигналы на входы элементов И 6, 6, 6. Управляющие сигналы поступят через элементы И 6,, 6, 6, на первые управляющие входы только тех сумматоров 3,, 3-, 3, в которых будут храниться двоичные эквиваленты чисел, строго больших единицы, так как только в этом случае на первые входы элементов И 6«, 6, 6 будут поданы разрешающие сиг- налы с выходов соответствующих пороговых элементов 4,, 42, 4,, подключенных к выходам сумматоров 3,, 3,3.

При наличии на выходе схемы 10 сравнения сигнала, соответствующего единичному значению преобразуемого в данном такте разряда исходного кода, этим сигналом будет подано разрешение на элементы И 5, , 5, 5 и сигналы с выхода 16 распределителя 11 импульсов будут поступать на вторые управляющие входы сумматоров 3, 3 , 3,.

При поступлении сигнала на первый управляющий вход любого сумматоpa 3(, 3, 33 OH осуществляет вычитание из хранящегося в нем числа числа поданного на его информационный вход с выхода предьщущего сумматора или регистра 1, а при поступлении сигна- ла на второй управляющий вход сумматор осуществляет сброс хранящегося в нем числа и запоминание числа, поданного на его информационный вход.

В рассматриваемом случае первый старший разряд исходного кода, обрабатываемый в первом такте, имеет единичное значение. Следовательно, управляющий сигнал с выхода 16 распределителя 11 импульсов последователь- но, начиная с сумматора Зд, поступит на вторые управляющие входы всех сумматоров 3, 3, , 3 , и они произведут запись двоичных эквивалентов следуницих чисел: в сумматор 3-, - 16 Ц(5,1), в сумматор Ц(4,2) и в сумматор (3,3).На этом работа устройства на данном такте заканчивается.

Второй такт.

Работа преобразователя кодов в этом такте отличается тем, что с выхода схемы 10 сравнения будет выдаваться сигнал, соответствующий нуле- вому значению 6-го разряда исходного кода, который обрабатывается во втором такте.

Первый полутакт.

При поступлении сигнала с выхода 14 распределителя 11 импульсов схема 10 сравнения выдает на элемент И 9 нулевой сигнал, в результате чего содержимое сумматора 12 остается без изменения, т.е. сохраняется число 42.

Второй полутакт.

Управляющга сигнал с выхода 16 распределителя 11 импульсов поступит через элементы И 6, 6 на первые управляющие входы только сумматоров 3 и Зг. В сумматоре 3 (в остальных, если сумматоров больше 3) хранится двоичный эквивалент единицы, поэтому пороговый элемент 4, не выдает больще разрешающего сигнала на элемент И 6 и сумматор 3, отключается от управления по первому входу. В сумматорах 3,j и Зд будет проведено вычитание поданных на их входы чисел из хранящихся в них. В результате этого будут получены двоичные эквиваленты следующих чисел: в сумматоре 16-5(4,1) и в сумматоре 3 - (3,2). В сумматоре 3 J сохранится двоичный эквивалент единицы, которому можно поставить в соответствие весовой коэффициент ,3) 1.

Работа устройства последующих тактов аналогична первому, если обрабатывается единичный разряд исходного кода, или второму, если обрабатывается нулевой разряд.

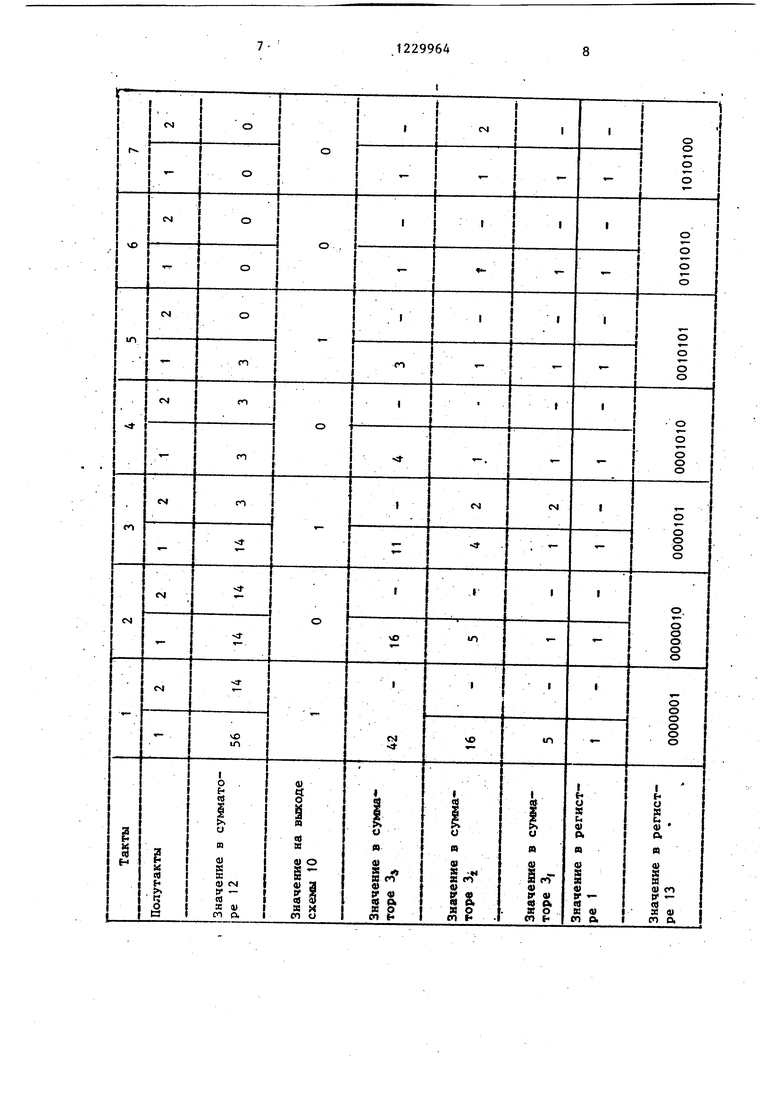

Изменение содержимого всех сумматоров 12, 3,, 32, Зз при преобразовании данного кода (111000) в полный двоичный код представлено в таблице. Конечный результате преобразования получен в регистре 13 на 7-ом такте и равен 1010100.

Изобретение позволяет также преобразовать полные двоичные коды в коды с постоянным весом. Отличие здесь только в том, что значения весовых коэффициентов для записи в сумматоры цепочки в исходном состоянии осуществляют по формуле (2).

Редактор Н. Егорова Заказ 2460/59

Техред Л.Олейник

Кор Под

Тираж 816 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А. Обручар Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода с постоянным весом в двоичный код | 1982 |

|

SU1020815A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1972 |

|

SU436345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-10-10—Подача