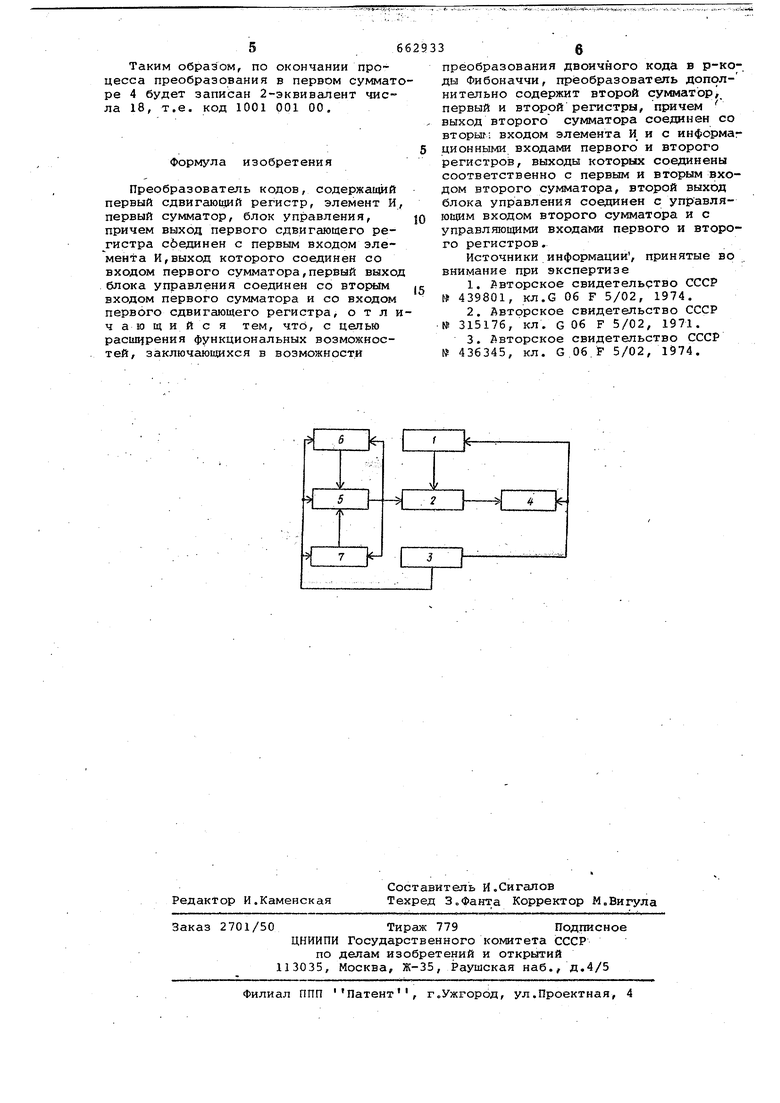

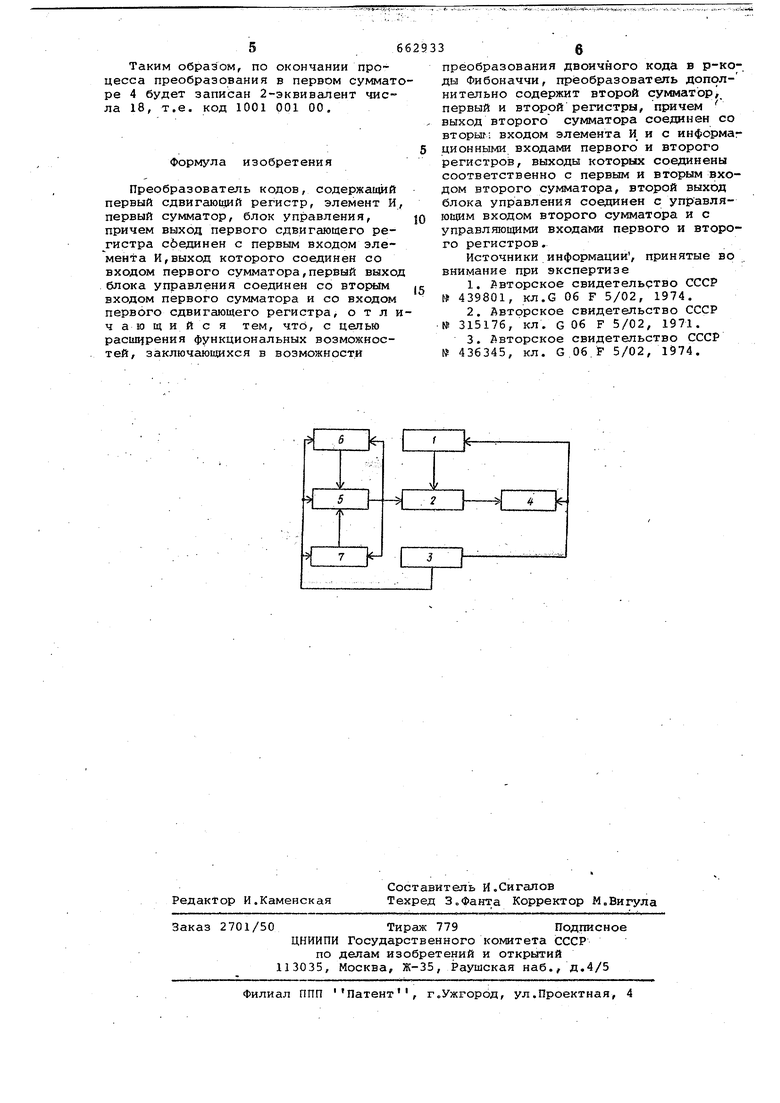

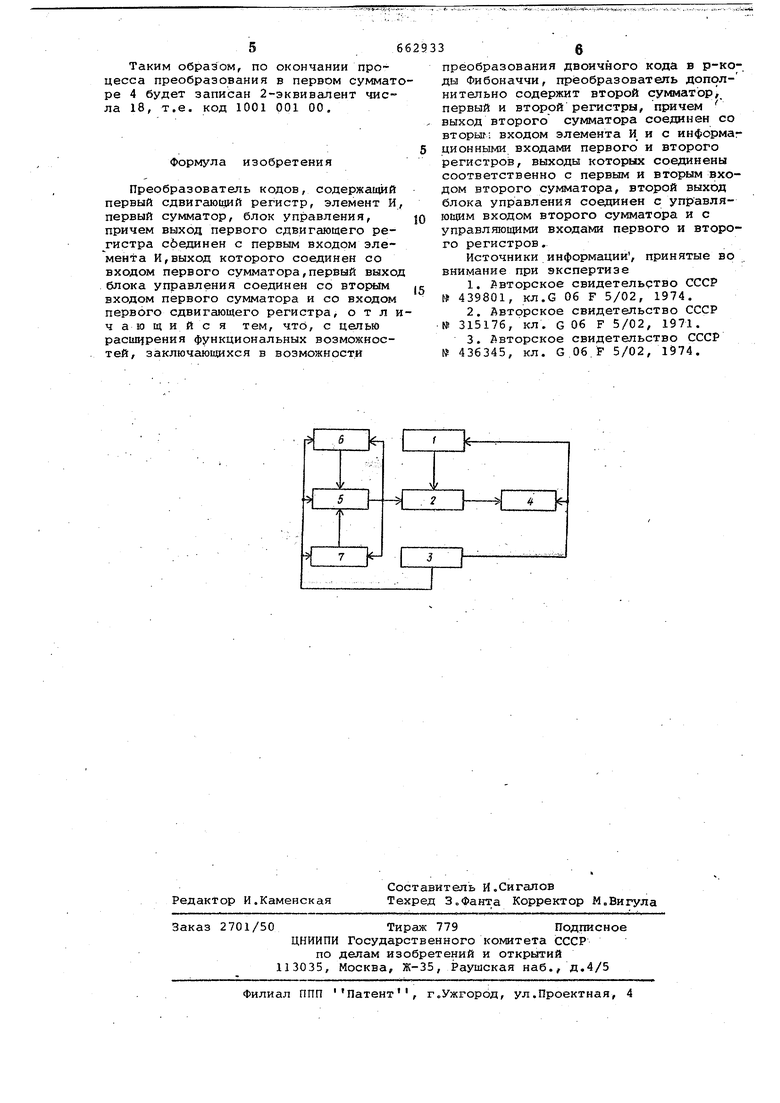

Изобретение относится к вычисли.тельной технике и может быть исполь зовано для преобразования двоичного кода в р-код Фибоначчи. Известны устройства для преобразования двоичного кода в код с другим основанием, использующие принци суммирования кодовых эквивалентов на накапливающем сумматоре 1,(2. Наиболее близким тexничecки з реш нием к данному изобретениюявляется преобразователь кодов, содержащий первый сдвигающий регистр, элемент И .первый сумматор, блок управления,, причем выходпервого сдвигающего регистра соединен -с первым входом . элемента И, выход которого соединен со входом первого сумматора., первый выход блока управления сое 1инен со вторым входом первого сумматора и со входом первого сдвигающего регист ра 3. Недостатком такого устройства является невозможность преобразования двоичного кода в р-код Фибоначчи. Целью изобретения является расширение функциональных возможностей., заключающихся в преобразовании двоичного кода в р-код Фибоначчи. 2 - Пост авленная цель достигается тем, что преобразователь дополнительно сод ержит второй сумматор, первый и второй регистры, причем выход второго сумматора соединен со вторым входом элемента И и с информационными входами первого и второго регистров, выходы которых соединены соответственно в первым и вторым входом второго сумматора, второй выход блока управления соединен с управляющим входом второго сумиатора ,и с уп авлшощими входами первого и второго регистров. Функциональная схема предлагаемого устройства приведена на чертеже. Устройство содержит первый сдвигающий регистр 1, предназначенный для хранения и последовательного, сдвига в сторону младших разрядов исходного преобразуемого.двоичного кода; элемент И 2, блок управления 3,. осуществляющий управление работой преобразователя; первый сумматор 4, в котором происходит накопление рэквивалентов весов двоичных разрядов; второй сумматор 5,,, пред назначенный для генерации р-эквивалентов весов двоичных разрядов, первый регистр р-кодов Фибоначчи б и .второй регистр р-кодов Фибоначчи 7, предназ наченные для хранения р-эквивалентрв весов двоичных разрядов на каждом такте преобразования. Устройство работает следующим образом. В исходном состоянии, код, подлежащий преобразованию, записывается в первый сдвиганнций регистр 1. В первы регистр р-кода Фибоначчи б и во Bfoрой регистр р-кода Фибоначчи 7 заносятся р-эквивалентны числа О. Во второй сумматор 5 заносится р-эквивалент веса первого разряда-двоичног кода (число 1). Первый сумматор 4 на ходится в нулевом состоянии. Каждый такт преобразования состои из двух псхлутактов. На Первом полутакте происходит сложение на етором сумматоре 5 содержимого первого регистра р-кодрв Фибоначчи б и второго регистра р-кодов .Фибоначчи 7. На втором полутакте происходит перезапись содержимого второго сумматора 5 в первый регистр р-кодов Фибоначчи б и во второй регистр р-кодов Фибоначчи 7. При .этом на первый вход элемента И 2 из первого регистра сдвига 1 посту пает содержимое младшего разряда преобразуемого двоичного кода. Если значение его равняется р-эквивалент веса младшего раз ряда- двоичного кбда не поступает на первый сумматор 4. Если значение младшего разряда преобразуемого двоичного кода равно , то через элемент И 2 в первый сумматор 4 записывается р-эквивалент веса младшего разряда двоичного кода. На следующем первом полутакте происходит сложение содержимого первого регистра р-кодов Фибоначчи б и второго регистра р-кодов Фибоначчи 7. При этом во втором сумматоре 5 находится .р-эквивалент-веса второго разряда двоичного кода (число 2), на следующем втором полутакте данный эквивалент поступит или не поступит, в зависимости от содержимого второго разряда исходного двоичного кода, на первый сумматор 4. На следующих полутактах преобразователь функционирует аналогичным образом. Процесс преобразования продолжается до тех пор, пока не произойдет полного сдвига содержимого первого сдвигающего регистра 1, т,е, . пока не поступит на первый вход элемента И 2 содержимое последнего старшего разряда преобразуемого двоичного кода. При этом в первом сумматоре 4 будет находиться р-эквивалент исходного двоичного числа. Примером функционирования данного преобразователя может служить преобразование двоичного кода числа 18 в 2кЬд Фибоначчи.

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь двоичного кода в код с постоянным весом | 1984 |

|

SU1229964A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Преобразователь кода с постоянным весом в двоичный код | 1982 |

|

SU1020815A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

100000100 2О 0. 1. О О . 100010000 2-00 010 10010 о 100 200001

1000 10000

000

о о

о . о 1

о о

о о 0 ,000001000 0 -00 о 0.01000 0 000001000 Таким образом, по окончании процесса преобразования в первом суммат ре 4 будет записан 2-эквивалент числа 18, т.е. код 1001 001 00. Формула изобретения Преобразователь кодов, содержа 1№1й первый сдвигающий регистр, элемент И первый сумматор, блок управления, причем выход первого сдвигающего регистра сбединен с первым входом элемента И,выход которого соединен со входом первого сумматора,первый выхо блока управления соединен со вторым входом первого сумматора и со входом первого сдвигающего регистра, отл чающийся тем, что, с целью расширения функциональных возможностей, заключающихся в возможности преобразования двоичного кода в р-коды Фибоначчи, преобразователь дополнительно содержит второй сумматор/ первый и второй регистры, причем выход второго сумматора соединен со вторып входом элемента И и с информаг ционными входами первого и второго регистрО1В, выходы которых соединены соответственно с первым и вторым входом второго сумматора, второй выход блока управления соединен с управляющим входом второго сумматора и с управляющими входами первого и второго регистров. Источники информации , принятые во внимание при экспертизе 1. iBTopCKoe свидетельство СССР № 439801, кл.С 06 F 5/02, 1974. 2.Авторское свидетельство СССР № 315176, кл. G Об F 5/02, 1971. 3.Авторское свидетельство СССР № 436345, кл. G 06.F 5/02, 1974.

Авторы

Даты

1979-05-15—Публикация

1976-08-02—Подача