Изобретение относится к вычислительной технике и цифровой автоматике,

Цель изобретения - упрощение регистра сдвига за счет уменьшения числа входов синхронизации.

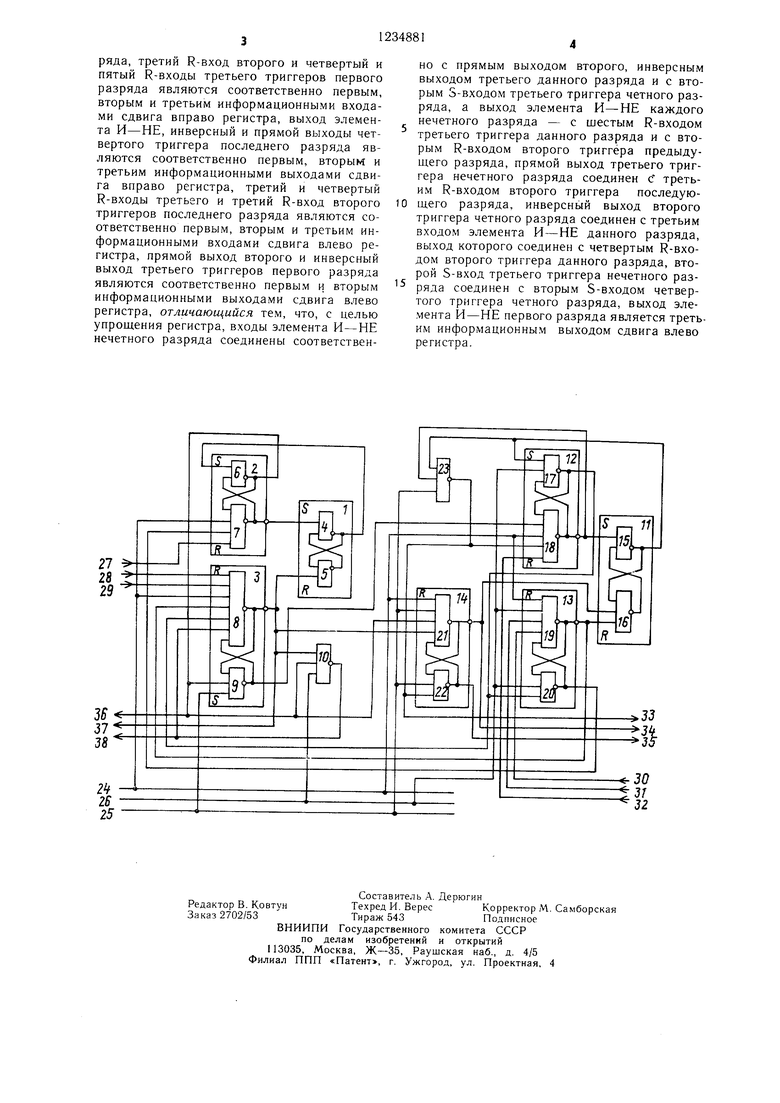

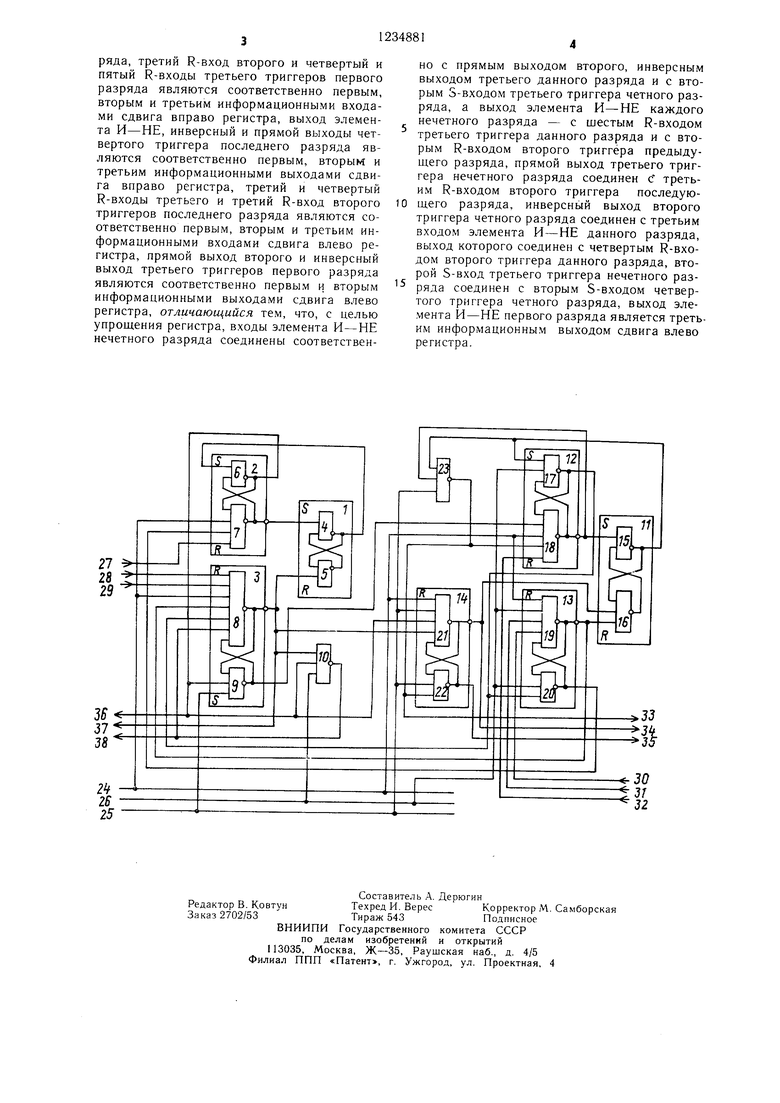

На чертеже изображены два соседних разряда реверсивного регистра сдвига, нечетный и четный.

Регистр содержит в нечетном (2К-1)-м разряде три RS-триггера 1, 2 и 3, состоящих соответственно из элементов И-НЕ 4 и 5, 6 и 7, 8 и 9, и-элемент И-НЕ 10, а в четно1М 2К-М разряде - четыре RS-триггера 11 -14, состоящих соответственно из элементов И-НЕ 15 и 16, 17 и 18, 19 и 20, 21 и 22, элемент И-НЕ 23. На чертеже показаны также вход синхронизации 24, управляющие входы сдвига вправо 25 и влево 26, первый, второй и третий информационные входы сдвига вправо 27, 28 и 29 и влево - 30, 31 и 32, первый, второй и третий информационные выходы сдвига вправо 33, 34 и 35 и влево 36, 37 и 38.

Состояния каждого из разрядов определяются состоянием первых триггеров данных разрядов.

Регистр работает следующим образом.

Для сдвига информации вправо, т. е. от младших разрядов к старшим, на управляющие входы 25 и 26 подаются соответственно « и «О. Входному коду «1 соответствует значение «1 на входе 29 и значение «О хотя бы на одном из входов 27 и 28. Входному коду «О соответствует значение «О на входе 29 и значение на каждом из входов 27 и 28. При записи кода «1 в нечетный разряд при положительном значении синхросигнала на входе 24 последовательно срабатывают элементы 7, 4 и 5, а при отрицательном значении синхросигнала - элементы 7, 6 и 9. При записи кода «О в нечетный разряд при положительном значении синхросигнала последовательно срабатывают элементы 8, 5 и 4, а при отрицательном значении синхросигнала - элементы 6 и 8, затем 9. При записи кода «1 в четный разряд при положительном значении синхросигнала последовательно срабатывают элементы 18, 15, 16, а при отрицательном значении синхросигнала - элементы 18, 23, 22. При записи кода «О в четный разряд при положительном значении синхросигнала последовательно срабатывают элементы 21, 16, 15, а при отрицательном значении синхросигнала - элементы 21 и 23, 22.

Для сдвига информации влево на управляющие входы 25 и 26 подаются соответственно «О и «1. Входные сигналы, подаваемые в этом режиме на входы 30, 31 и 32, аналогичны сигналам, подаваемым на входы 27, 28 и 29 при сдвиге влево. При записи кода «1 в нечетный (четный) разряд при положительном значении синхросигнала по- с; едовательно срабатывают элементы 7, 4, 5 (18, 15, 16,), а при отрицательном значении

синхросигнала - элементы 7, 6, 10 (18, 17, 20). При записи кода «О в нечетный (четный) разряд при положительном значении синхросигнала последовательно срабатывают элементы 8, 5, 4 (19, 1 6, 15), а при отрицательном значении синхросигнала - элементы 6 и 8, 10 (17 и 19, 20).

Минимальный период следования синхросигнала составляет 6г, где т - среднее время задержки на элементе И-НЕ. Число входов

синхронизации равно 5 на пару соседних разрядов.

Для изменения направления сдвига при непрерывной работе регистра («на ходу) значение сигналов на управляющих входах 25. и 26 должно изменяться на противоположное по спаду синхросигнала за время, не превышающее 2т.

20

Формула изобретения

Реверсивный регистр сдвига, содержащий в каждом нечетном разряде три RS-триггера и элемент И-НЕ и в каждом четном разряде - четыре RS-триггера и элемент

И-НЕ, причем в каждом разряде прямой выход первого триггера соединен с первым S-входом второго триггера, прямой выход которого соединен с первым S-входом третьего триггера, инверсные выходы второго и третьего триггеров соединены соответственно с первыми S- и R-входами первого триггера, в каждом четном разряде инверсный выход четвертого триггера соединен с вторым R-входом первого триггера, прямой выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с

первым З-входом четвертого триггера, в каждом разряде первые R-входы всех триггеров, кроме первых, являются входом синхронизации регистра, вторые S- и R-входы четвертого триггера и второй вход элемента И - НЕ четного разряда являются управляющим входом сдвига вправо регистра, второй S-вход второго и вторые S- и R-входы третьего триггеров четного разряда являются управляющим входом сдвига влево регистра, прямой выход второго и инверсный выход третьего триггеров каждого нечетного разряда соединены соответственно с третьим и четвертым R-входами четвертого триггера последующего разряда и третьего триггера предыдущего разрядов, прямой выход второго триггера, инверсный и прямой выходы третьего триггера четного разряда соединены соответственно с вторым и третьим R-входами третьего и вторым R-входом второго триггеров предыдущего разряда, а выход элемента И-НЕ, инверсный и прямой выходы четвертого триггера

каждого четного разряда, кроме последнего, соединены соответственно с третьим R-входом второго и с четвертым и пятым R-входами третьего триггеров последующего разряда, третий R-вход второго и четвертый и пятый R-входы третьего триггеров первого разряда являются соответственно первым, вторым и третьим информационными входами сдвига вправо регистра, выход элемента И-НЕ, инверсный и прямой выходы четвертого триггера последнего разряда являются соответственно первым, вторым и третьим информационными выходами сдвига вправо регистра, третий и четвертый R-входы третьего и третий R-вход второго триггеров последнего разряда являются соответственно первым, вторым и третьим информационными входами сдвига влево регистра, прямой выход второго и инверсный выход третьего триггеров первого разряда являются соответственно первым и вторым информационными выходами сдвига влево регистра, отличающийся тем, что, с целью упрощения регистра, входы элемента И-НЕ нечетного разряда соединены соответственно с прямым выходом второго, инверсным выходом третьего данного разряда и с вторым S-входом третьего триггера четного разряда, а выход элемента И-НЕ каждого нечетного разряда - с шестым R-входом третьего триггера данного разряда и с вторым R-входом второго триггера предыдущего разряда, прямой выход третьего триггера нечетного разряда соединен с третьим R-входом второго триггера последующего разряда, инверсный выход второго триггера четного разряда соединен с третьим входом элемента И-НЕ данного разряда, выход которого соединен с четвертым R-входом второго триггера данного разряда, второй S-вход третьего триггера нечетного разряда соединен с вторым S-входом четвертого триггера четного разряда, выход элемента И-НЕ первого разряда является третьим информационным выходом сдвига влево регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2021 |

|

RU2759002C1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

Изобретение относится к вычислительной технике и цифровой автоматике. Целью изобретения является упрощение реверсивного регистра сдвига за счет уменьшения числа входов синхронизации. Для этого нечетные и четные разряды регистра выполнены по-разному. Нечетный разряд состоит из трех RS-триггеров и одного элемента И-НЕ, а четный - из четырех RS-триггеров и одного элемента И-НЕ. Каждый из RS- триггеров состоит из двух элементов И-НЕ. 1 ил. N3 00 42 СХ) 00

32

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Реверсивный регистр сдвига | 1979 |

|

SU780047A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-05-30—Публикация

1982-12-29—Подача