Изобретение относится к автоматике и вычислительной технике и может быть использовано в средствах идентификации аналоговых сигналов, поступающих на вход устройства от различных объектов управления, а также в средствах контроля, диагностирования и отладки систем.

Целью изобретения является расширение области применения устройства.

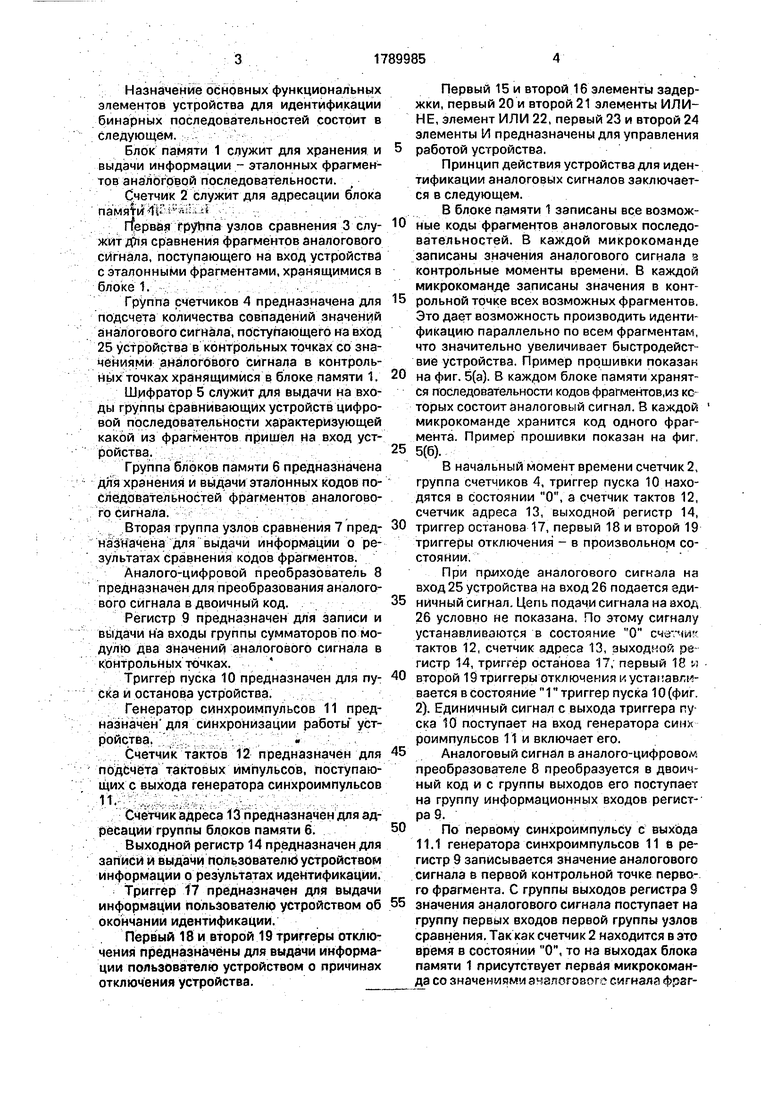

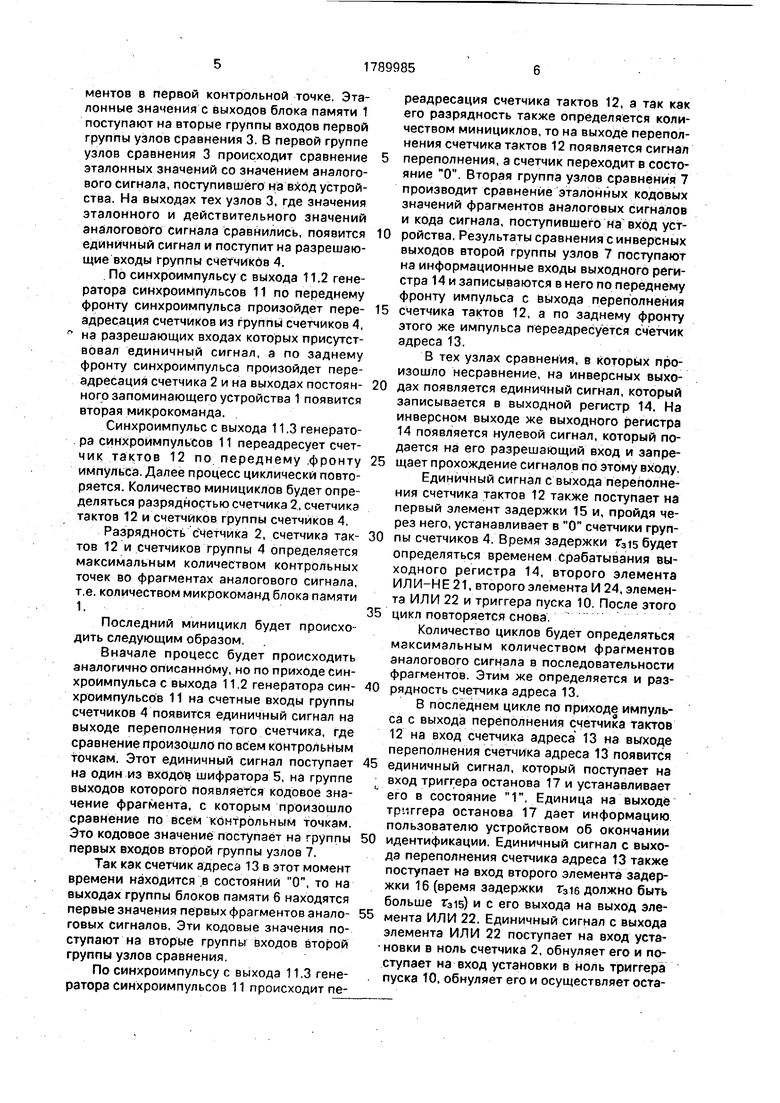

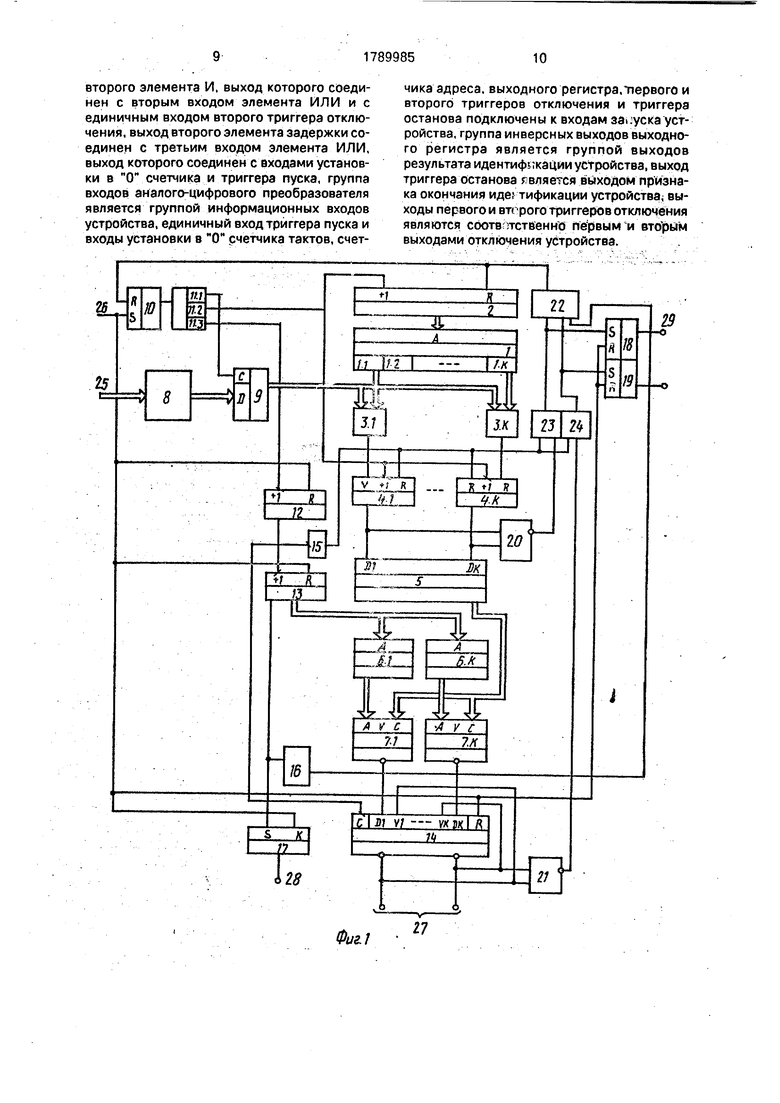

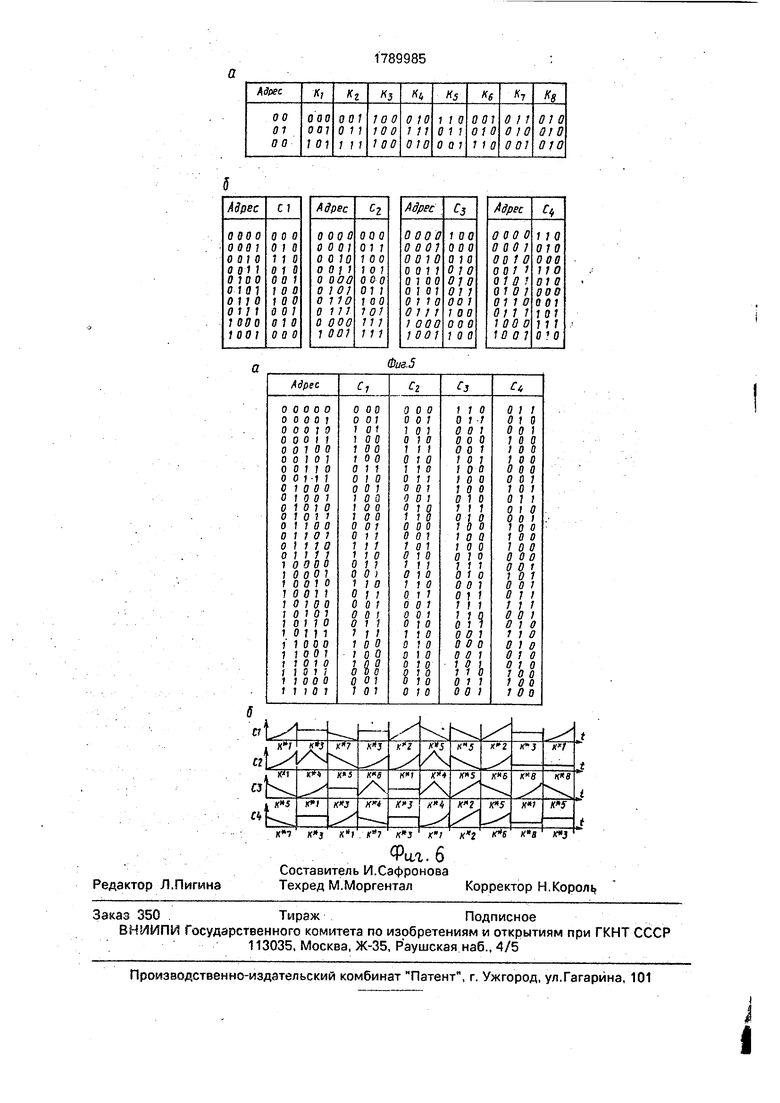

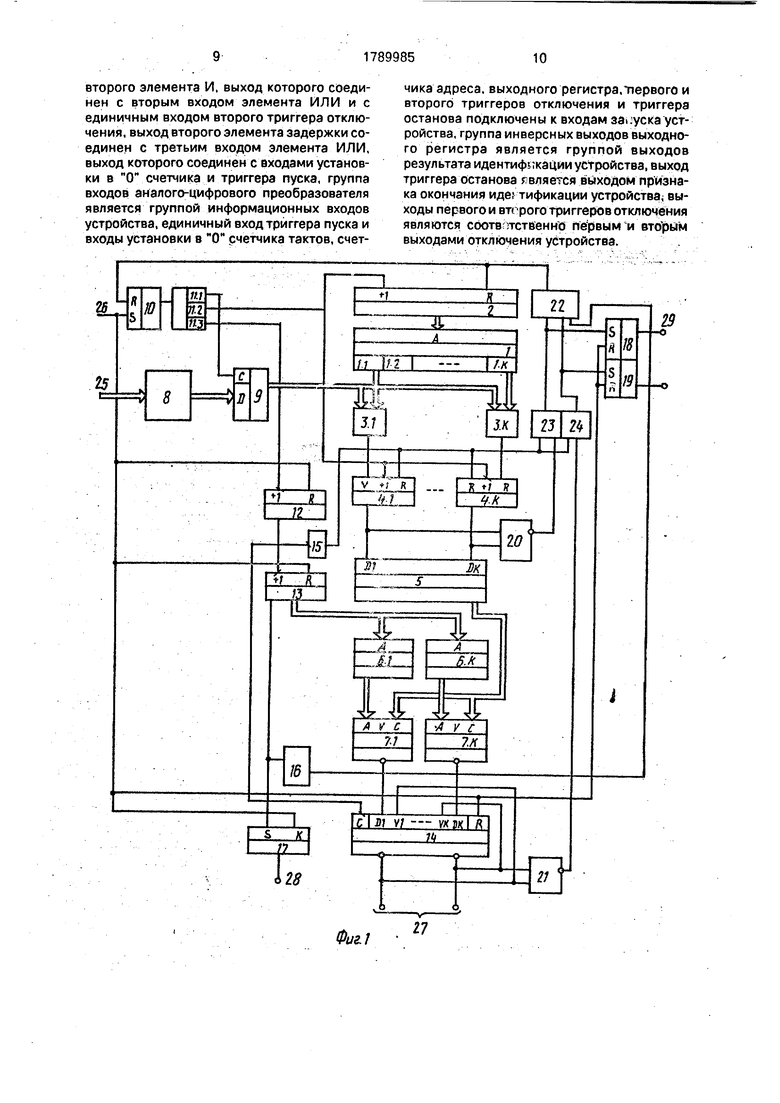

На фиг. 1 представлена функциональная схема устройства для идентификации аналоговых сигналов; на фиг. 2, 3, 4 - временные диаграммы функционирования устройства; на фиг. 5,6- примеры кодирования блоков памяти предлагаемого устройства и прототипа.

УстройствЪ для идентификации знало: говых сигналов содержит блок памяти 1, счетчик 2, первую группу узлов сравнения 3, группу Счетчиков 4, шифратор 5, группу памяти 6, вторую группу узлов сравнения устройств 7, аналого-цифровой преобразователь 8, регистр 9, триггер пуска 10, генератор синхроимпульсов 11, счетчик тактов 12, счетчик адреса 13, выходной регистр 14, первый 15 и второй 16 элементы задержки, триггер останова 17, первый 18 и второй 19 триггеры отключения, первый 20 и второй 21 элементы ИЛИ-НЕ, элемент ИЛИ 22, первый 23 и второй 24 элементы И, информационный вход 25, вход пуска 26, выход результата идентификации 27, выход останова 28, первый 29 и второй 30 выходы отключения.

Х|

00

ю ю

00

ел

Назначение основных функциональных элементов устройства для идентификации бинарных последовательностей состоит в следующем.

Блок памяти 1 служит для хранения и выдачи информации - эталонных фрагментов аналоговой последовательности.

Счетчик 2 служит для адресации блока

па мят а Ьа ,-/:. .... .

Н|ервая группа узлов сравнения 3 служит Для сравнения фрагментов аналогового сигнала, поступающего на вход устройства с эталонными фрагментами, хранящимися в блоке 1. .. -. г . . : /

Группа счетчиков 4 предназначена для подсчета количества совпадений значений аналогового сигнала, поступающего на вход 25 устройства в контрольных точках со значениями аналогового сигнала в контрольных точках хранящимися в блоке памяти 1.

Шифратор 5 служит для выдачи на входы группы сравнивающих устройств цифровой последовательности характеризующей какой из фрагментов пришел на вход устройства, j Ч

Группа блоков памяти 6 предназначена для хранений и выдачи эталонных кодов последовательностей фрагментов аналогового сигнала..

Вторая группа узлов сравнения 7 предназначена для выдачи информации о результатах сравнения кодов фрагментов.

Аналого-цифровой преобразователь 8 предназначен для преобразования аналогового сигнала в двоичный код.

Регистр 9 предназначен для записи и выдачи на входы группы сумматоров по модулю два значений аналогового сигнала в контрольных точках.

Триггер пуска 10 предназначен для пуска и останова устройства.

Генератор синхроимпульсов 11 предназначен для синхронизации работы устройства. ;:Г;1 ;Г-... ......

Счетчик тактов 12 предназначен для подсчёта тактовых импульсов, поступающих с выхода генератора синхроимпульсов .,::}..;;;Л. ;

Счетчик адреса 13 предназначен для адресации группы блоков памяти 6.

Выходной регистр 14 предназначен для записи и выдачи пользователю устройством информации о результатах идентификации.

Триггер 17 предназначен дли выдачи информации пользователю устройством об окончании идентификации.

Первый 18 и второй 19 триггеры отключения предназначены для выдачи информации пользователю устройством о причинах отключения устройства.

Первый 15 и второй 16 элементы задержки, первый 20 и второй 21 элементы ИЛИ- НЕ, элемент ИЛИ 22, первый 23 и второй 24 элементы И предназначены для управления

работой устройства.

Принцип действия устройства для идентификации аналоговых сигналов заключается в следующем.

В блоке памяти 1 записаны все возможные коды фрагментов аналоговых последовательностей. В каждой микрокоманде записаны значения аналогового сигнала в контрольные моменты времени. В каждой микрокоманде записаны значения в конт5 рольной точке всех возможных фрагментов. Это дает возможность производить идентификацию параллельно по всем фрагментам, что значительно увеличивает быстродействие устройства. Пример прошивки показан

0 на фиг. 5(а). В каждом блоке памяти хранятся последовательности кодов фрагментов.из которых состоит аналоговый сигнал. В каждой микрокоманде хранится код одного фрагмента. Пример прошивки показан на фиг,

5 5(6).

В начальный момент времени счетчик 2, группа счетчиков 4, триггер пуска 10 находятся в состоянии О, а счетчик тактов 12, счетчик адреса 13, выходной регистр 14,

0 триггер останова 17, первый 18 и второй 19 триггеры отключения - в произвольно состоянии.

При приходе аналогового сигнала на вход 25 устройства на вход 26 подается зди5 ничный сигнал. Цепь подачи сигнала на вход 26 условно не показана, По этому сигналу устанавливаются в состояние О счегчик тактов 12, счетчик адреса 13, выходной регистр 14, триггер останова 17, первый 18 м

0 второй 19 триггеры отключения к устанавливается в состояние 1 триггер пуска 10 (фиг. 2). Единичный сигнал с выхода триггера пуска 10 поступает на вход генератора синх роимпульсов 11 и включает его.

5 Аналоговый сигнал в аналого-цифровом преобразователе 8 преобразуется в двоичный код и с группы выходов его поступает на группу информационных входов регистра 9.

0 По первому синхроимпульсу с выхода 11.1 генератора синхроимпульсов 11 в регистр 9 записывается значение аналогового сигнала в первой контрольной точке первого фрагмента. С группы выходов регистра 9

5 значения аналогового сигнала поступает на группу первых входов первой группы узлов сравнения. Так как счетчик 2 находится в это время в состоянии О, то на выходах блока памяти 1 присутствует первая микрокоманда со значениями аналогового сигнала фрагментов в первой контрольной точке. Эталонные значения с выходов блока памяти 1 поступают на вторые группы входов первой группы узлов сравнения 3. В первой группе узлов сравнения 3 происходит сравнение 5 эталонных значений со значением аналогового сигнала, поступившего на вход устройства. На выходах тех узлов 3, где значения эталонного и действительного значений аналогового сигнала сравнились, появится 10 единичный сигнал и поступит на разрешающие входы группы счетчиков А.

По синхроимпульсу с выхода 11.2 генератора синхроимпульсов 11 по переднему фронту синхроимпульса произойдет пере- 15 адресация счетчиков из группы счетчиков 4, на разрешающих входах которых присутствовал единичный сигнал, а по заднему фронту синхроимпульса произойдет переадресация счетчика 2 и на выходах постоям- 20 ногр запоминающего устройства 1 появится вторая микрокоманда.

Синхроимпульс с выхода 11.3 генератора синхроимпульсов 11 переадресует счетчик тактов 12 по переднему .фронту 25 импульса. Далее процесс циклически повторяется. Количество минициклов будет определяться разрядностью счетчика 2, счетчика тактов 12 и счетчиков группы счетчиков 4,

Разрядность счетчика 2, счетчика так- 30 тов 12 и счетчиков группы 4 определяется максимальным количеством контрольных точек во фрагментах аналогового сигнала, т.е. количеством микрокоманд блока памяти 1.35

Последний миницикл будет происходить следующим образом,

Вначале процесс будет происходить аналогично описанному, но по приходе синхроимпульса с выхода 11.2 генератора син- 40 хроимпульсов 11 на счетные входы группы счетчиков 4 появится единичный сигнал на выходе переполнения того счетчика, где сравнение произошло по всем контрольным точкам. Этот единичный сигнал поступает 45 на один из входов шифратора 5, на группе выходов которого появляется кодовое значение фрагмента, с которым произошло сравнение по всем контрольным точкам. Это кодовое значение поступает на группы 50 первых входов второй группы узлов 7.

Так как счетчик адреса 13 в этот момент времени находится в состояний О, то на выходах группы блоков памяти 6 находятся первые значения первых фрагментов знало- 55 говых сигналов, Эти кодовые значения поступают на вторые группы входов второй группы узлов сравнения.

По синхроимпульсу с выхода 11.3 генератора синхроимпульсов 11 происходит переадресация счетчика тактов 12, а так как его разрядность также определяется количеством минициклов, то на выходе переполнения счетчика тактов 12 появляется сигнал переполнения, а счетчик переходит в состояние О. Вторая группа узлов сравнения 7 производит сравнение эталонных кодовых значений фрагментов аналоговых сигналов и кода сигнала, поступившего на вход устройства. Результаты сравнения с инверсных выходов второй группы узлов 7 поступают на информационные входы выходного регистра 14 и записываются в него по переднему фронту импульса с выхода переполнения счетчика тактов 12, а по заднему фронту этого же импульса переадресуется счетчик адреса 13.

В тех узлах сравнения, в которых произошло несравнение, на инверсных выходах появляется единичный сигнал, который записывается в выходной регистр 14. На инверсном выходе же выходного регистра 14 появляется нулевой сигнал, который подается на его разрешающий вход и запрещает прохождение сигналов по этому входу.

Единичный сигнал с выхода переполнения счетчика тактов 12 также поступает на первый элемент задержки 15 и, пройдя через него, устанавливает в О счетчики группы счетчиков 4. Время задержки r3is будет определяться временем срабатывания выходного регистра 14, второго элемента ИЛИ-НЕ 21, второго элемента И 24, элемента ИЛИ 22 и триггера пуска 10. После этого цикл повторяется снова.

Количество циклов будет определяться максимальным количеством фрагментов аналогового сигнала в последовательности фрагментов. Этим же определяется и разрядность счетчика адреса 13.

В последнем цикле по приходе импульса с выхода переполнения счетчика тактов 12 на вход счетчика адреса 13 на выходе переполнения счетчика адреса 13 появится единичный сигнал, который поступает на вход триггера останова 17 и устанавливает его в состояние 1. Единица на выходе триггера останова 17 дает информацию пользователю устройством об окончании идентификации. Единичный сигнал с выхода переполнения счетчика адреса 13 также поступает на вход второго элемента задержки 16 (время задержки Г316 должно быть больше г315) и с его выхода на выход элемента ИЛИ 22. Единичный сигнал с выхода элемента ИЛИ 22 поступает на вход установки в ноль счетчика 2, обнуляет его и поступает на вход установки в ноль триггера пуска 10, обнуляет его и осуществляет останов устройства. Информация о результатах идентификации снимается с инверсных выходов выходного регистра 14 и поступает на выход 27 устройства. В том случае, если во время работы устройства по окончании ми- ницикла ни на одном из выходов переполнения группы счетчиков 4 на появился единичный сигнал (фиг, 2), что свидетельствует о том, что фрагмент, прошедший на вход устройства, не сравнился ни с одним из хранящихся в постоянном запоминающем устройстве 1, то на выходе первого элемента ИЛИ-НЕ 20 появится единичный сигнал, который поступит на вход первого элемента И 23. С выхода первого элемента задержки 15 поступает на второй вход первого элемента И 23 единичный сигнал и на выходе его появится единичный сигнал, который устанавлизает первый триггер отключения 18 в состояние 1 и, пройдя через элемент ИЛИ 22, обнуляет счетчик 2, и триггер пуска 10 производит останов устройства,

- - Случай, когда происходит несравнение кодов фрагментов, показан на фиг. 4.

В данном устройстве временные характеристики генератора синхроимпульсов выбираются следующим образом. Временной

интервал между первым синхроимпульсом и вторым должно быть больше суммарного времени срабатывания регистра 9 Тд и первой группы узлов сравнения Зз1. Временной интервал между вторым и третьим синхроимпульсами должен быть больше суммарного времени срабатывания группы счетчиков 4Т41, шифратора 5 т$ и второй группы узлов сравнения 7 т/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналогового сигнала | 1990 |

|

SU1797097A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Устройство для идентификации бинарных сигналов | 1989 |

|

SU1730611A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в средствах идентификации аналоговых сигналов, поступающих на вход устройства от различных объектов управления, а также в средствах контроля, диагностирования и отладки систем. Цель изобретения - расширение области применения устройства. Поставленная цель достигается путем дополнительного введения в известное устройство для идентификации аналоговых сигналов шифратора, группы блоков памяти, второй группы узлов сравнения, первого и второго элементов задержки, первого и второго триггеров отключения, первого и второго элементов ЙЛИ-НЕ, первого и второго элементов И, элемента ИЛИ, а также соответствующих связей между ними. Положительный эффект от использования заявляемого решения заключается в значительном выигрыше в объеме памяти. Кроме того, заявляемое устройство существенно расширяет область применения прототипа нэ класс систем, йсполТзую щйх более сложные сигналы. 6 ил. in С

Формула изоб р ё тения Устройство для идентификации аналоговых сигналов, содержащее блок постоянной памяти, счетчик, первую группу узлов сравнения, группу счетчиков, триггер пуска, генератор синхроимпульсов, аналого-циф- ровой преобразователь, регистр, счетчик тактов, счетчик адреса, выходной регистр, триггер останова,, причем группа выходов счетчика соединена с группой входов постоянного запоминающего устройства, группы выходов которого соединены с первыми группами входов.узлов сравнения первой группы, выходы которых соединены с разрешающими входами счетчиков группы, выходы аналого-цифрового преобразователя соединены с группой информационных входов регистра, группа выходов которого соединена с вторыми группами входов узлов сравнения первой группы, выход триггера пуска соединен с входом запуска генератора синхроимпульсов, первый выход которого соединен с синхровходом регистра, второй выход генератора синхроимпульсов соединен со счетным входом счетчика и со счетными входами счетчиков группы, трети# выход генератора синхроимпульсов соединен со счетным входом счетчика тактов, выход переполнения которого соединён со счётным входом счетчика адреса и синхровходом выходного регистра, выход перепол- нения счетчика адреса соединен с единичным входом триггера останова, инверсные выходы выходного регистра соединены с разрешающими входами выходного регистра, отличающееся тем, что, с

целью расширения области применения, устройство содержит шифратор, группу блоков памяти, вторую группу узлов сравнения, первый и второй элементы задержки, первый и второй триггеры отключения, первый и второй элементы ИЛИ-НЕ, первый и второй элементы И, элемент ИЛИ, причем выходы переполнения счетчиков группы соединены с входами шифратора, группа выходов которого соединена с первыми группами входов узлов сравнения второй группы, группа выходов счетчика адреса соединена с группами входов блоков памяти группы, группы выходов которых соединены с вторыми группами входов узлов сравнения второй группы, инверсные выходы которых соединены с информационными входами выходного регистра, выход переполнения счетчика тактов соединен с входом первого элемента задержки, выход которого соединен с входами установки в О счетчиков группы, выход переполнения счетчика адреса соединен с входом второго элемента задержки, выходы переполнения счетчиков группы соединены с входами первого элемента ИЛИ-НЕ, инверсные выходы выходного регистра соединены с входами второго элемента ИЛИ-НЕ, выход первого элемента задержки соединен с первыми

входами первого и второго элементов И, выход первого элемента ИЛИ-НЕ соединен с вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ и единичным входом первого триггера отключения, выход второго элемента ИЛИ-НЕ соединен с вторым входом

второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и с единичным входом второго триггера отключения, выход второго элемента задержки соединен с третьим входом элемента ИЛИ, выход которого соединен с входами установки в О счетчика и триггера пуска, группа входов ан а лого-Цифрового преобразователя является группой информационных входов устройства, единичный вход триггера пуска и входы установки в 0й счетчика тактов, счетФиг.1

чика адреса, выходного регистра. первого и второго триггеров отключения и триггера останова подключены к входам запуска устройства, группа инверсных выходов выходного регистра является группой выходов результата идентификации устройства, выход триггера останова шляется выходом признака окончания идег тификации устройства; выходы первого и второго триггеров отключения являются соответственно первым и вторым выходами отключения устройства.

27

3866Ш

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-01-23—Публикация

1991-02-25—Подача