t1

Изобретение относится к автоматике и вычислительной технике и может использоваться для определения интеграла по времени от величины, заданной в виде меняющейся во времени частоты следования импульсов.

Цель изобретения - повьшение точности за счет уменьшения погрешности интегрирования входной импульсной последовательности. .

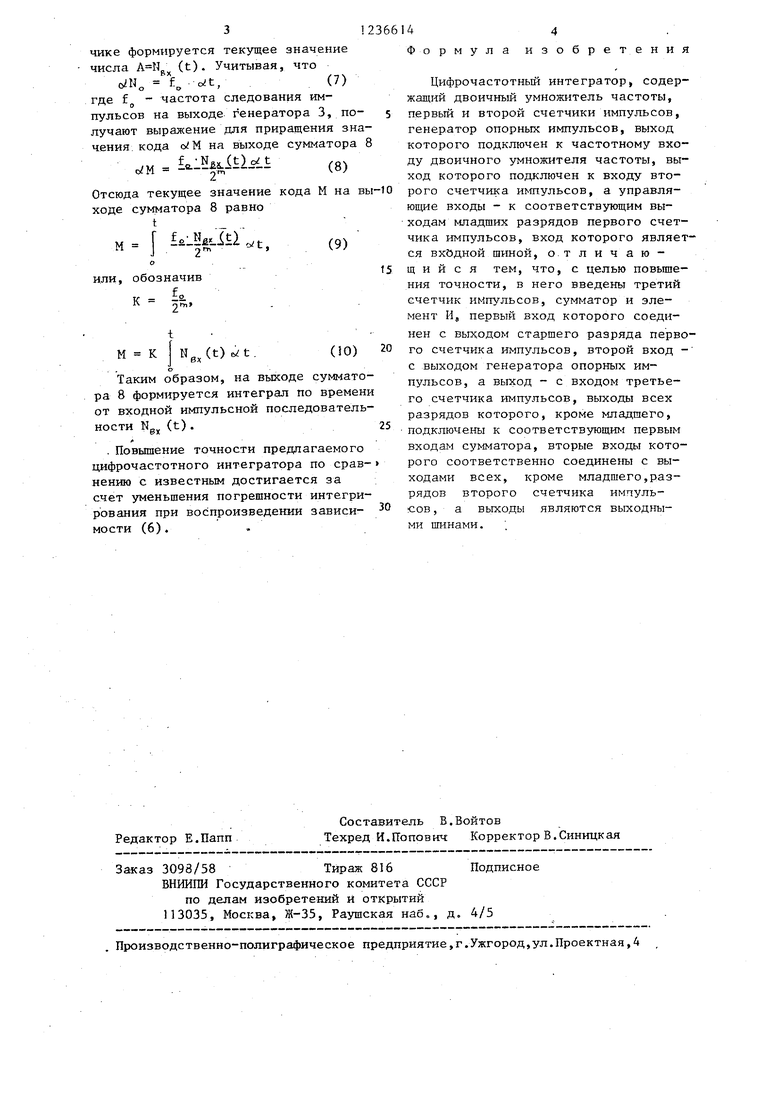

На чертеже представлена структурная электрическая схема устройства.

Цифрочастотный интегратор содер- жит входную шину 1, двоичный умножитель 2 частоты, генератор 3 опорных импульсов, первый 4, второй 5 и третий 6 счетчики импульсов, элемент И 7, сумматор 8, выходные шины 9.

В цифрочастотном интеграторе выход генератора 3 подключен к частот- ному входу двоичного умножителя 2 частоты, выход которого подключен к входу второго счетчика 5, входная

ы

%а.,, +а 2 +. . .а, 2° ) .,,

ц - -; (1}

„1т,- 1

где га - разрядность счетчика 4; а - значащая цифра i-ro (i

152,..,,m-l) разряда числа в счетчике 4, принимающая значение О или 1. Приращение dN импульсной последовательности N на выходе элемента И 7, вызываемое приращением импульсной последовательности N , описывается выражением

, ,, а, (2) где а - значащая цифра старшего разряда в счетчике 4,

ч 2: + fiNoIa i.2lLi2tt 2.2i;l± ia 2:i

Окончательно

,м - А ,

(5)

или

М .

N,

(6)

-.т-7

2 Vn

двоичное число в счетчике 4;

- количество импульсов импульс-

ной последовательности с выхода генератора 3;

4 J

шина 1 является входом перво-го счетчика 4, выход старшего разряда которого подключен к первому входу элемента И 7, второй вход которого соединен с выходом генератора 3. Выходы мл;адших разрядов первого счетчика 4 подключеШ) к соответствующим управляющим входам двоичного умножителя 2 частоты, выход элемента И 7 подключен к входу третьего счетчика 6, выходы всех, кроме младшего, разрядов счетчиков 6 и 5 подключены к соответствующим первым и вторым входам сумматора 8, выходы которого являются выходными шинами 9.

Цифрочастотный интегратор работает следующим образом.

Приращение oi 11 импульсной последовательности NJ,, на выходе генератора 3 вызывает на выходе двоичного умножителя 2 приращение cJ N его выходной импульсной последовательности N, причем

30

нимающая значение (11 ff

Р мпульсные последовательности N и N подаются соответственно на счетчики 5 и 6. Учитывая, что мпадщие разряды этих счетчиков не подключе- ны к входам сумматора, записывают выражение, определяющее приращение о М значения кода М на выходе сумматора, вызываемое приращениями c.N и cvLNj импульсных последовательностей N и Nj на входах счетчиков 5 и 6. о/М + N, ; (3)

(4)

М - значение кода на выходе сумматора 8.

Выражения (5) и (6) аналогичнь выражен:иям, описывающим работу примененного в известном устройстве двоичного умножителя частоты сщ-раз- рядным счетчиком-делителем.

При подаче на входную шину пифро- частотного интегратора импульсной последовательности Np(t)5 являющейся функцией от времени, в счетчике формируется текущее значение числа (t). Учитывая, что

X -ч ч

f , (7)

где f - частота следования импульсов на выходе генератора 3, по- лучают выражение для приращения значения кода на выходе сумматора 8

„ . (8)

Отсюда текущее значение кода М на выходе сумматора 8 равно

t

„. f .-|j,,

М

(9)

или, обозначив

К -2Л ТП1

К

I

Вх

(t)t

(Ю)

Таким образом, на выходе сумматора 8 формируется интеграл по времени от входной импульсной последовательности Ng (t).

j . Повышение точности предлагаемого

цифрочастотного интегратора по сравнению с известньм достигается за счет уменьшения погрешности интегрирования при воспроизведении зависимости (6) .

Редактор Е.Папп

Составитель В.Войтов Техред И.Попович Корректор В.Синицкая

Заказ 3098/58Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

12366144

Формула изобретения

5

Ю

15

20

5

0

Цифрочастотный интегратор, содержащий двоичный умножитель частоты, первый и второй счетчики импульсов, генератор опорных импульсов, выход которого подключен к частотному входу двоичного умножителя частоты, выход которого подключен к входу второго счетчика импульсов, а управляющие входы - к соответствующим выходам младших разрядов первого счетчика импульсов, вход которого является входной шиной, о-тличаю- щ и и с я тем, что, с целью повышения точности, в него введены третий счетчик импульсов, сумматор и элемент И, первый вход которого соединен с выходом старшего разряда первого счетчика импульсов, второй вход - с выходом генератора опорных импульсов, а выход - с входом третьего счетчика импульсов, выходы всех разрядов которого, кроме младшего, подключены к соответствующш- первым входам сумматора, вторые входь которого соответственно соединены с выходами всех, кроме младшего,разрядов второго счетчика импульсов , а выходы являются выходными шинами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Цифрочастотное вычислительное устройство | 1984 |

|

SU1196863A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Число-импульсный функциональный преобразователь | 1985 |

|

SU1256021A2 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU388277A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для интегрирования величины, заданной меняющейся : во времени частотой следования импульсов i Целью изобретения являетh-1 ся повыйение точности за счет уменьшения погрешности интегрирования входной импульсной последовательности. Приращение импульсной последовательности на выходе генератора 3 опорных импульсов вызывает соответствующее приращение импульсных последовательностей на выходе управляемого первым счетчиком 4 импульсов двоичного умножителя 2 частоты и на выходе элемента И 7, откуда эти последовательности поступают соответственно на счетчики 5 и 6 импульсов. Выходы всех разрядов счетчиков 5 и 6, кроме младших, подключены соответственно к входам сумматора 8, на выходе которого формируется код, соответствующий интегралу по времени от входной импульсной последовательности, поступающей по входной шине 1 на вход счетчика 4 импульсов. 1 ил. с S (Л Kvd СА Од Од Ji 9

| Гутников B.C | |||

| Интегральная электроника в измерительньк устройствах | |||

| -Л., 1980, с.238-240 | |||

| Дискретный интегратор | 1959 |

|

SU124158A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

Авторы

Даты

1986-06-07—Публикация

1984-12-18—Подача