Изобретение относится к. вычислительной технике, в частности к регистровым запоминающим устройствам.

Целью изобретения является расширение o6;iacTH применения устройства за счет осуществления независимого считывания нескольких информагционнь1х слов при одновременной записи других информационных

слов. :,. ,

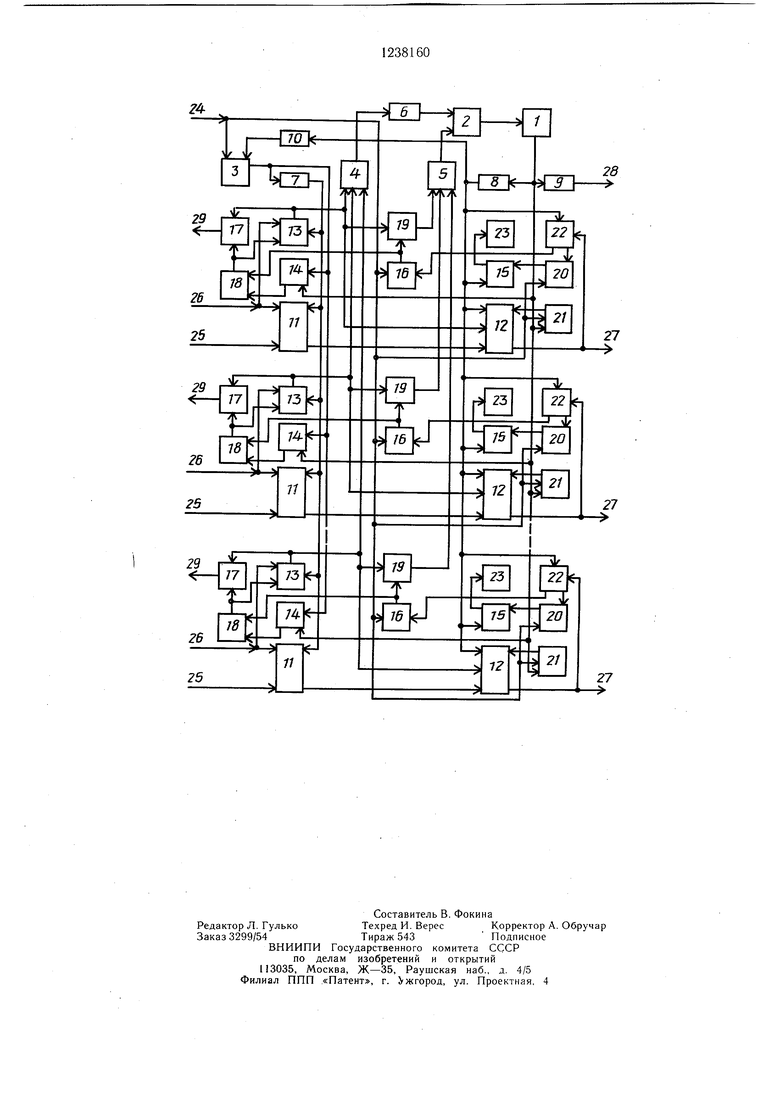

На чертеже представлена электрическая структурная схема предложенного устройства.

Устройство содержит формирователь 1 сигнала записи, первый 2, второй 3 и третий 4 элементы ИЛИ, элемент И 5, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 элементы задержки, первую группу регистров 11 слова, вторую труппу регистров 12 слова, первую группу триггеров 13, вторую группу триггеров 14, третью группу триггеров 15, счетчики 16 импульсов, первую группу элементов ИЛИ 17, вторую группу элементов ИЛИ 18, третью группу элементов ИЛИ 19, четвертую группу элементов ИЛИ 20 и пятую группу элементов ИЛИ 21, группу блоков 22 контроля и группу блоков 23 индикации, при этом на чертеже обозначены: установочный 24, информационные 25 и тактовые 26 входы и информационные 27, тактовый 28 и индикаторные 29 выходы устройства.

Число регистров 11 слова, число регистров 12 слова, число триггеров 13, число триггеров 14, число триггеров 15, число счетчиков 16 импульсов, число элементов ИЛИ 17, число элементов ИЛИ 18, число элементов ИЛИ 20, число элементов ИЛИ 19, число элементов ИЛИ 21, число блоков 22 контроля группы и число блоков 23 индикации группы равно каждое числу информационных входов 25 устройства.

Устройство функционирует следуюш,им образом.

Перед началом функционирования по переднему фронту прямоугольного импульса сигнала сброса, формируемого с помощью формирователя сигнала сброса от кнопки управления и поступающего на установочный вход 24 буферного запоминающего устройства, из устройства, в состав которого (например оперативная память) может входить буферное запоминающее устройство (длительность импульса сигнала сброса выбирается из расчета, чтобы за время этой длительности в буферном запоминающем устройстве до конца прошел весь процесс первоначальной у1,тановки элементов), устанавливаются в нулевое положение все разряды всех счетчиков 16 импульсов, через соответствующие элементы ИЛИ 21 устанавливаются в нулевое положение все разряды всех регистров 12 слова и через соответствующие элементы ИЛИ 20 устанавливаются в нулевое положение все триггеры 15, а также через элементы ИЛИ 3 уста5

5

навливаются в нулевое положение все триггеры 14 и через элемент 7 задержки (несколько последовательно соединенных элементов 7 или элементов ИЛИ), с временем с задержки, больщим времени установки в нулевое положение любого триггера 14 плюс время задержки любого элемента ИЛИ 18 плюс время задержки на разблокировку первого входа установки любого триггера 13 и плюс время задержки на установ- 0 ку в нулевое положение любого счетчика 16 импульсов, устанавливаются в нулевое положение все триггеры 13 и все разряды всех регистров 11 слова.

Установка элементов устройства в нулевое положение облегчает также проведение ремонтных работ в этом устройстве.

После установки элементов буферного . запоминающего устройства в исходное положение начинается процесс-передачи информации в это устройство. Информация в виде 0 параллельной серии информационных слов, представленных каждое параллельным двоичным кодом, поступает через информационные входы 25 устройства на регистры 11 слова, в каждый из которых записывается одно информационное слово по переднему фронту соответствующего этому информационному слову прямоугольного импульса сигнала записи, поступающего в устройство через соответствующий тактовый вход 26 устройства.

Записываемая в любой регистр 11 слова информация через время задержки этого регистра 11 слова появляется на его информационном выходе.

По переднему фронту этого же импульса сигнала записи соответствующей с регистром И слова триггер 13 выставляет на своем выходе уровень логической единицы, который через соответствующий элемент ИЛИ 17 поступает на соответствующий индикаторный выход 29 устройства, запрещая передачу в этот занятый регистр 11 0 слова информационного слова. По каждому информационному входу 25 устройства информационное слово записывается в соответствующий с этим информационным входом 25 регистр 11 слова независимо от наличия или отсутствия информации на соседних с ним информационных входах 25 устройства.

Таким образом, при записи в буферное устройство параллельной серии информационных слов возможны два случая; либо во все регистры 11 слова одновременно записывается по одному информационному слову, либо во все регистры 11 слова записывается по одному информационному слову со смещением во времени относительно друг друга.

5 При записи информационных слов одновременно во все регистры слова одновременно все триггеры 13 выставляют на своих выходах уровни логической единицы, каж0

5

5

0

дый из которых поступает на соответствующий ему вход элемента ИЛИ 4 и через соответствующий ему элемент ИЛИ 19 на соответствующий ему вход элемента И 5, а также поступает на вход управления соответствующего регистра 12 слова, разрещая запись в тот регистр 12 слова информационного слова, присутствующего на информационном выходе соответствующего с ним регистра II слова. Передний фронт уровня логической единицы с выхода элемента И 5 через элемент ИЛИ 2 поступает на вход запуска формирователя 1 сигнала раньще, чем передний фронт уровня логической единицы с выхода элемента ИЛИ 4, через элемент 6 задержки и через элемент ИЛИ 2 на этот же вход запуска формирователя 1 сигнала записи. По переднему фронту уровня логической единицы формирователь 1 сигнала записи формирует одиночный прямоугольный импульс сигнала записи, длительность которого выбирается минимальной с учетом времен задержек элементов, из которых изготовлено буферное запоминающее устройство, и с учетом длительности каждого сигнала записи, поступающих на тактовые входы 26 устройства, таким образом, чтобы была обеспечена работоспособность устройства.

По переднему фронту этого сформированного импульса сигнала записи все триггеры 14 выставляют на своем выходе каждый уровень логической единицы, который через соответствующий элемент ИЛИ 18 блокирует первый вход установки соответствующего с ним триггера 13 (второй вход установки этого триггера 13 не блокируется), и через соответствующий с ним элемент 17 подтверждает сигнал занятости соответствующего с ним регистра 11 слова или запрещает прием информации в этот регистр 11 слова, если на одноименный информационный вход 25 не поступила информация. По переднему фронту импульса этого же сигнала записи через соответствующий элемент ИЛИ 21 устанавливаются в нулевое положение все разряды всех регистров 12 слова (такая установка всех разрядов всех регистров 12 слова производится каждый раз перед записью в эти регистры 12 слова новых информационных слов). После этого через элемент 8 задержки (линия задержки или несколько последовательно соединенных элементов И или ИЛИ) с временем задержки, больщим времени задержки на переключение любого триггера 14 плюс время задержки любого элемента ИЛИ 18 плюс время задержки на блокировку первого входа установки любого триггера 13, а также времени задержки на установку в нулевое положение через соответствующий элемент ИЛИ 21 любого регистра 12 слова, а также больщей длительности импульса этого же сигнала записи по переднему фронту импульса этого

5

же сигнала записи в каждый регистр 12 слова (если на его входе управления присутствует уровень логической единицы) записывается информационное слово (если оно присутствует на информационном выходе соответствующего регистра II слова), которое через время задержки этого регистра 12 слова появляется на его информационном выходе, к все триггеры 15 выставляют на своих выходах уровни логической единицы, 0 каждый из которых поступает на вход соответствующего блока 23 индикации группы, например элемента индикации с согласующим резистором, включая его по своему переднему фронту.

Импульс этого же сигнала записи поступает также на вход управления каждого блока 22 контроля группы, например схему свертки по модулю два с клапанирующими элементами И на информационном входе и выходах этого блока 22 контроля и с элементом Q задержки на его входе управления, который через время задержки, больщее длительности импульса этого же сигнала записи плюс время задержки любого регистра 12 слова, формирует контрольные разряды и сравнивает их с контрольными разрядами в 5 информационном слове, появившемся на информационном выходе соответствующего регистра 12 слова. При совпадении этих контрольных разрядов (в информационном слове нет искажения и оно прищло вовремя на соответствующий информационный вход 25 устройства) на первом выходе этого блока 22 контроля появляется прямоугольный импульс с длительностью, равной длительности импульса сигнала записи, по переднему фронту импульса на выходе (первом) этого блока 22 контроля через соответствующий элемент ИЛИ 20 сбрасывается соответствующий триггер 15, в результате чего выключается соответствующий блок 23 индикации. Если же прямоугольный импульс появился на втором выходе этого же блока 0 22 контроля (ошибка в информационном слове или отсутствие информационного слова, появивщегося на выходе соответствующего регистра 12 слова, т.е. контрольные разряды не совпали), то соответствующий триггер 15 не сбрасывается (соответствующий 5 блок 23 индикации не выключается), а соответствующий счетчик 16 импульсов по переднему фронту этого импульса прибавляет единицу к содержимому (к содержащемуся в нем числу).

По импульсу этого же сигнала записи через элемент 10 задержки (линия задержки или несколько последовательно соединенных элементов И или ИЛИ) с временем задержки, больщим времени задержки любого 5 блока 22 контроля группы от переднего фронта импульса этого же сигнала записи, поступившего на его вход управления, до появления на каком-либо из его выходов импульса плюс время задержки любого элемента ИЛИ 20 плюс время задержки на переключение любого триггера 15, а также большим времени задержки любого блока 22 контроля плюс время задержки любого счетчика 16 импульсов от момента появления на его входе сложения переднего фронта импульса до появления на его выходе уровня логической единицы (при прибавлении единицы к максимально допустимому заложенному в счетчике 16 импульсов числу сбоев в информационном слове) и через элемент ИЛИ 3, устанавливаются в нулевое положение все триггеры 14 и через элемент 7 задержки устанавливаются в нулевое положение все триггеры 13 и все разряды регист- ров 11 слова (буферное запоминающее устройство подготовлено для принятия следующей параллельной серии информационных слов по информационным входам 25, за исключением тех информационных входов 25, соответствующие счетчики 16 импульсов которых выставили на своих выходах уровни логической единицы).

Импульс этого же сигнала записи через элемент 9 задержки (линия задержки или несколько последовательно соединенных элементов И или элементов ИЛИ) с временем задержки, большим времени задержки элемента 8 задержки плюс время задержки регистра 12 слова, поступает на тактовый выход 28 устройства, сопровождая передачу с информационных выходов 27 устрой- ства двоичного кода одновременно всех информационных слов одной параллельной серии.

При записи в буферное запоминающее устройство параллельной серии информационных слов со смещением во времени от- носительно друг друга (что практически и наблюдается) в любой из регистров 11 слова может быть записано информационное слово раньше, чем в любые другие регистры 11 слова будут записаны остальные информационные слова. Соответственно и триггер 13, соответствующий регистру 11 слова, раньше других триггеров 13 выставит на своем выходе уровень логической единицы. Этот уровень логической единицы поступит через соответствующий элемент ИЛИ 19 на элемент И 5, а также поступит через элемент ИЛИ 4 на вход элемента 6 задержки (линия задержки или несколько последовательно соединенных элементов И или элементов ИЛИ), длительностью времени задержки которого плюс время за- держки на переключение любого триггера 13 плюс время задержки элемента ИЛИ 4 плюс время задержки элемента ИЛИ 2 плюс время задержки на формирование формирователем 1 сигнала записи импульса сигнала записи плюс время задержки на пере- ключение любого триггера 14 плюс время задержки любого элемента ИЛИ 18 и плюс время задержки на блокировку первого

входа установки любого триггера 13 определяется допустимый предел рассогласования во времени относительно друг друга передних фронтов импульсов сигналов записи (по тактовым входам 26 устройства) соответствующих каждое слову в одной и той же параллельной серии информационных слов.

Таким образом, от момента появления переднего фронта, опережающего. сигнал записи на каком-либо тактовом входе 26 устройства, до момента блокировки первого входа установки всех триггеров 13 в остальные свободные регистры 11 слова в этом втором случае могут быть в различные моменты времени в указанном допустимом пределе записаны соответствующие информационные слова одной параллельной серии. При этом уровни логической единицы с выходов остальных триггеров 13 также поступают на соответствующие входы элемента ИЛИ 4 и на соответствующие входы элемента И 5. На выходе элемента ИЛИ 4 уже присутствует уровень логической единицы, соответствующий опережающему сигналу записи, а на выходе элемента И 5 уровень логической единицы появится только тогда, когда на всех его входах будут присутствовать уровни логической единицы.

Таким образом, здесь (в этом втором случае) возможны две ситуации: либо на все входы элемента И 5 пришли уровни логической единицы в пределах допустимого отрезка времени раньще (могут приходить в различные моменты времени), а следовательно, на выходе элемента И 5 появится уровень логической единицы раньше, чем появится уровень логической единицы на выходе элемента 6 задержки, либо на выходе элемента 6 задержки уровень логической единицы появится раньше, чем появится уровень логической единицы на выходе элемента И 5. Одновременное появление уровней логической единицы на выходе элемента 6 задержки и на выходе элемента И 5 можно рассматривать как первую ситуацию.

При первой ситуации во втором случае информация во все регистры 12 слова начнет переписываться из соответствующего регистра 11 слова после заполнения последнего свободного регистра 11 слова. Процесс записи информации в регистры 11 слова и в регистры 12 слова протекает описанным в первом случае способом (когда все информационньш входы 25 одновременно приходят все информационные слова одной параллельной серии).

При второй ситуации во втором случае переменный разброс поступающих в буферное запоминающее устройство информационных слов одной параллельной серии оказывается больше допустимой величины. В этой ситуации формирователь 1 сигнала записи сформирует импульс сигнала записи еще до поступления всех информационных слов одной параллельной серии в буферное запоми

нающее устройство, т.е. в некоторый регистр 11 слова или в некоторые регистры 11 слова, а следовательно, в соответствующий или соответствующие регистры 12 слова могут быть не записаны информацион- ные слова. В блоках 23 индикации группы, соответствующих регистрам 12 слова, будет включена индикация, которая не выключается и по которой можно определить по какому из информационных входов 25 устройства пришло информационное слово с за- позданием или вовсе не прищло. При этом соответствующие счетчики 16 импульсов суммируют каждый число опозданий или искаженных информационных слов по одноименных с каждым информационных входах 25 устройства. Если же по какому- либо из информационных входов 25 устройства это число искажений и опозданий достигнет допустимой величины, заложенной в соответствующей с этим информационным входом 25 устройства счетчике 16 импульсов, то на выходе этого счетчика 16 импульсов появится уровень логической единицы, по переднему фронту которого через соответствующий элемент ИЛИ 19 на соответствующем входе элемента И 5 выставляется уровень логической единицы, исключая таким образом этот информационный вход 25 из процесса записи информации в буферное запоминающее устройство и блокируя его, подтверждая на соответствующем индикаторном выходе 29 через соответствующие элементы ИЛИ 18 и ИЛИ 17 уровень логической единицы, который также через элемент ИЛИ 18 подтверждает блокировку первого входа установки соответствующего триггера 13, запрещая в дальнейшем переключение его по первому входу установки.

Прекращение приема информационных слов по информационному входу 25 устройства, на который информационное слово поступает с опозданием свыше допустимой величины числа опозданий и искажений - систематически или случайно во времени, не позволяет значительно увеличивать длительность времени приема информации в буферное запоминающее устройство за счет ожидания возможного поступления информационного слова от внешнего устройства, которое подключено к этому информационному входу 25 и в котором возможна неисправность.

Возможна ситуация, когда информационное слово может начать записываться в какой-либо регистр 11 слова во время блокировки первого входа установки соответствующего регистра 11 слова триггера 13, т. е. передний фронт импульса сигнала записи, поступающий на соответствующий вход 26 устройства, и передний фронт уровня логической единицы сигнала блокировки первого входа установки триггера 13, появившейся на выходе соответствующего элемента ИЛИ 18, приходят на этот триг

5

5

г 0 0

0

5

0

5

5

0

гер 13 одновременно (т.е. в буферное запоминающее устройство по соответствующему информационному входу 25 начался процесс передачи информационного слова во время блокировки этого информационного входа 25, так как уровень логической единицы на соответствующем индикаторном выходе 29 устройства еще не успел появиться). В этой ситуации триггер 13 сможет либо выставить на своем выходе уровень логической единицы, либо на его выходе останется уровень логического нуля. Если триггер 13 выставил на своем выходе уровень логической единицы, то информационное слово, вписанное в соответствующий регистр 11 слова, перепишется в соответствующий регистр 12 слова. Если же на выходе этого триггера 13 остался уровень логического нуля, то информационное слово, вписываемое в регистр 1 слова, не перепишется в дальнейшем в соответствующий регистр 12 слова и будет потеряно (но процесс приема этого информационного слова в буферное запоминающее устройство не прерывается).

Таким образом, предлагаемое буферное запоминающее устройство осуществляет прием параллельной серии информационных слов с допустимым рассогласованием во времени между информационными словами одной параллельной серии, при этом по каждому информационному входу 25 производится независимая запись информационного слова, а также устройство после приема этой параллельной серии информационных слов осуществляет ее выдачу, при этом по всем информационным выходам 27 производится одновременная выдача этой параллельной серии информационных слов. Кроме того, устройство подсчитывает независимо друг от друга по каждому информационному входу 25 количество ошибочных и рассогласованных во времени свыше допустимой величины (как систематических, так и случайных) информационных слов из различных параллельных серий, если это количество превысит заранее заданную допустимую для данного информационного входа 25 величину, то прием информационных слов различных параллельных серий в буферное запоминающее устройство по данному информационному входу прекращается (причем остается включенной соответствующая сигнализация по данному информационному входу 25).

Предлагаемое буферное запоминающее устройство может быть использовано для выравнивания во времени параллельной серии информационных слов, например для выравнивания во времени параллельной серии одинаковых информационных слов (результатов вычислений), поступающих от одинаковых процессоров (от каждого процессора одно информационное слово в каж- жой параллельной серии), которые одновременно по командам обсчитывают одинаковые задачи (для большей надежности функционирования всего вычислительного комплекса, в состав которого входят эти процессоры) . Выравненная во времени параллельная серия одинаковых информационных слов поступает в дальнейшем на блок коррекции, который сравнивает- между собой эти информационные слова одной и той же параллельной серии, т.е. корректирует и исправляет результаты вычислений. Временное рассогласование информационных слов одной параллельной серии в приведенном примере может происходить из-за разброса времен задержки элементов, из которых изготовлены процессоры.

Формула изобретения

Буферное запоминаюш,ее устройство, содержащее формирователь сигнала записи, первый и второй элементы ИЛИ, первый элемент задержки, первую группу регистров слова и первую группу триггеров, отличающееся тем, что, с целью расширения области применения устройства за счет осуществления независимого считывания нескольких информационных слов при одновременной записи других информационных слов, в него введены третий элемент ИЛИ, элемент И, второй, третий, четвертый и пятый элементы задержки, вторая группа регистров слова, вторая и третья группы триггеров, группы элементов ИЛИ, группа счетчиков импульсов, группа блоков контроля и группа блоков индикации, причем выход первого элемента ИЛИ соединен с входом запуска формирователя сигнала записи, выход элемента И соединен с первым входом первого элемента ИЛИ, выход третьего элемента ИЛИ соединен с входом первого элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ, первый вход второго элемента ИЛИ соединен с входом установки каждого счетчика импульсов группы, с первым входом каждого элемента ИЛИ четвертой группы, с входом каждого элемента ИЛИ пятой группы- и является установочным входом устройства, выход второго элемента ИЛИ соединен с первым входом установки каждого триггера второй группы и с входом второго элемента задержки, выход которого соединен с вторым входом установки каждого триггера первой группы и с входом установки каждого регистра слова первой группы, выход формирователя сигнала записи соединен с входом третьего и четвертого элементов задержки, с вторым входом установки каждого триггера второй группы и с первым

5

0

5

0

0

5

0

5

входом каждого элемента ИЛИ пятой группы, выход четвертого элемента задержки является тактовым выходом устройства, выход третьего элемента задержки соединен с входом пятого элемента задержки, с входом управления каждого блока контроля группы, с первым входом установки каждого триггера третьей группы и с тактовым входом .каждого регистра слова второй группы, выход пятого элемента задержки соединен с вторым входом второго элемента ИЛИ, выходы элементов ИЛИ четвертой группы соединены с вторым входом установки соответствующих триггеров третьей группы, выходы которых соединены с входами соответствующих блоков индикации группы, выходы элементов ИЛИ пятой группы соединены с входами установки соответствующих регистров слова второй группы, информационные выходы которых соединены с информационными входами соответствующих блоков контроля группы и являются соответствующими информационными выходами устройства, первые выходы блоков контроля группы соединены с входами сложения соответствующих счетчиков импульсов группы, выходы которых соединены с вторыми входами соответствующих элементов ИЛИ третьей группы и с первыми входами соответствующих элементов ИЛИ второй группы, вторые выходы блоков контроля группь соединены с вторыми входами соответствующих элементов ИЛИ четвертой группы, выходы триггеров второй группы соединены с вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с вторыми входами соответствующих элементов ИЛИ первой группы и с входами управления соответствующих триггеров первой группы, первые входы установки которых соединены с тактовыми входами соответствующих регистров слова первой группы и являются соответствующими тактовыми входами устройства, информационные входы регистров слова первой группы являются соответствующими информационными входами устройства, информационные выходы регистров слова первой группы соединены с информационными входами соответствующих регистров слова второй группы, выходы триггеров первой группы соединены с первыми входами соответствующих элементов ИЛИ первой группы, с соответствующим входом третьего элемента ИЛИ, с первыми входами соответствующих элементов ИЛИ третьей группы и с входами управления соответствующих регистров слова второй группы, выходы элементов ИЛИ третьей группы соединены с соответствующими входами элемента И, выходы элементов ИЛИ первой группы являются соответствующими индикаторными выходами устройства.

f4

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1474742A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1272357A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236555A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1288757A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Буферное запоминающее устройство | 1984 |

|

SU1203595A1 |

| Запоминающее устройство | 1985 |

|

SU1288759A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

Изобретение относится к вычислительной технике, в частности к регистровым запоминающим устройствам. Целью изобретения является расширение области применения за счет осуществления независимого считывания нескольких информационных слов при одновременной записи других информационных слов. Устройство содержит три элемента ИЛИ, элемент И, пять элементов задержки, две группы регистров слова, три группы триггеров, группы элементов ИЛИ, группу счетчиков импульсов, группу блоков контроля и группу блоков индикации. Устройство может быть использовано для выравнивания во времени параллельной серии информационных слов, например для выравнивания во времени параллельной серии информационных слов (результатов вычислений), поступающих от одинаковых процессоров (от каждого процессора одно информационное слово в каждой параллельной серии), которые одновременно по командам обсчитывают одинаковые задачи (для большей надежности функционирования всего вычислительного комплекса, в состав которого входят эти процессоры). Выравненная во времени параллельная серия одинаковых информационных слов поступает в дальнейшем на блок коррекции, который сравнивает между собой эти информационные слова одной и той же параллельной серии, т. е. корректирует и исправляет результаты вычислений. Временное рассогласование информационных слов одной параллельной серии может происходить из-за разброса времен задержки элементов, из которых изготовлены процессоры. I ил. (Л с N3 СлЭ СХ) о:

| Буферное запоминающее устройство | 1982 |

|

SU1030855A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1109798A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-15—Подача