ts3

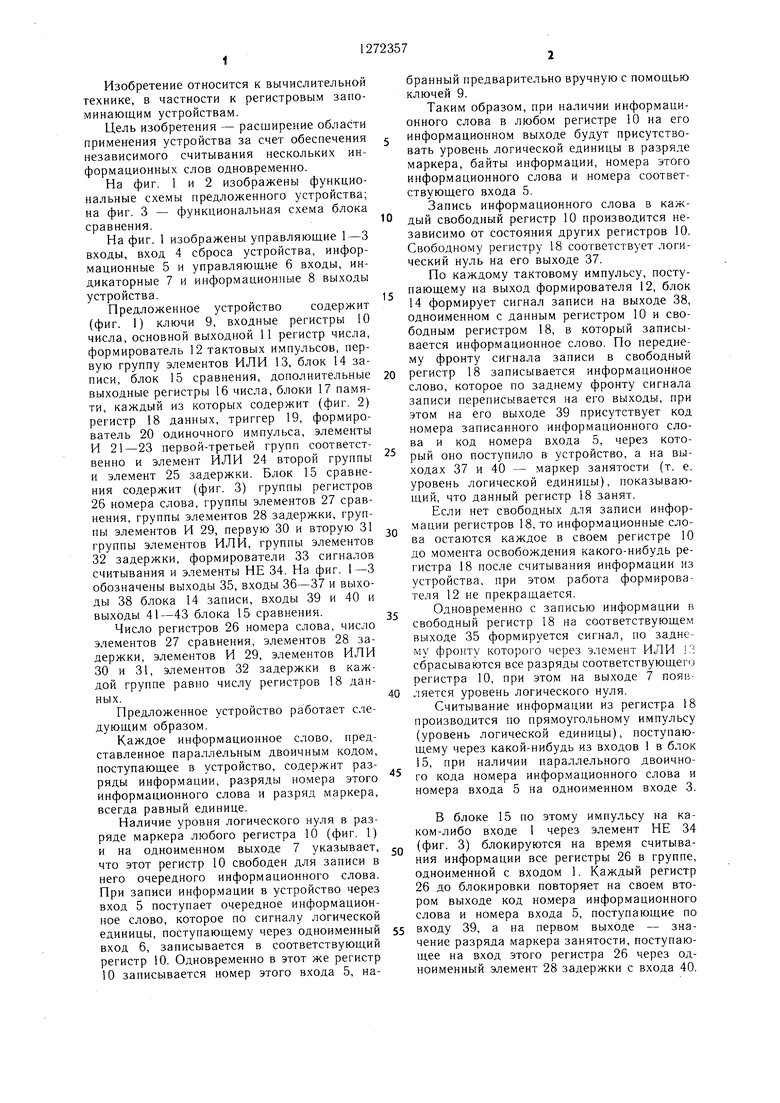

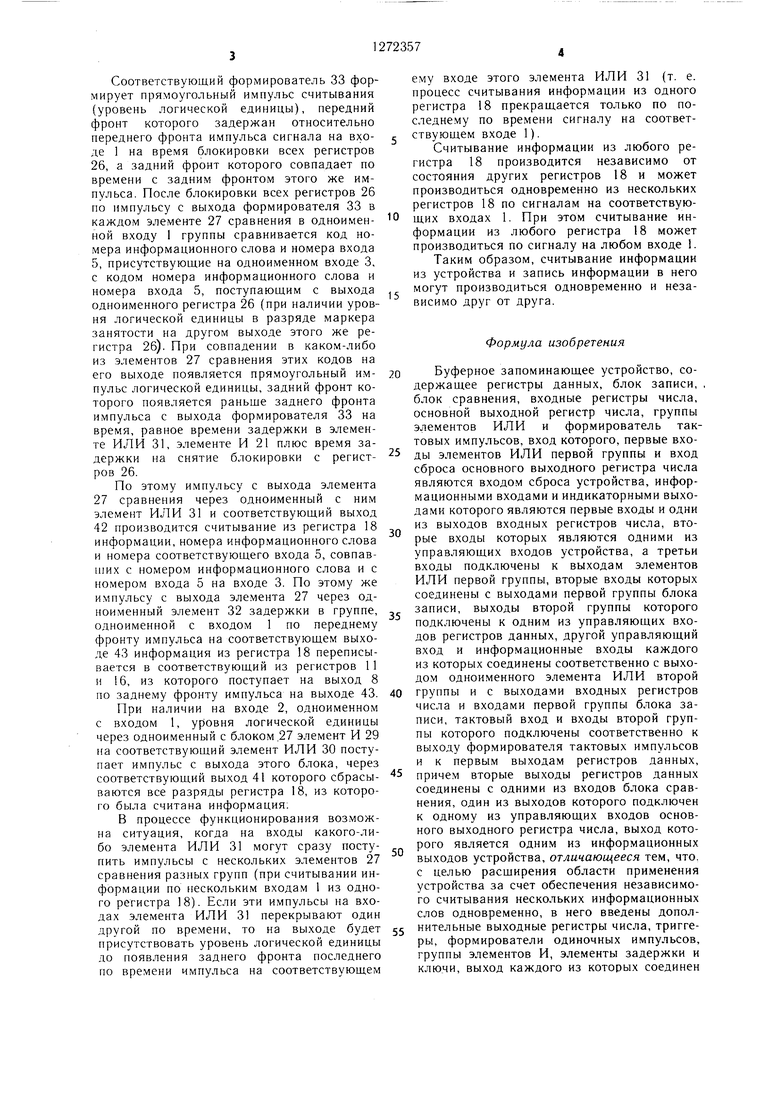

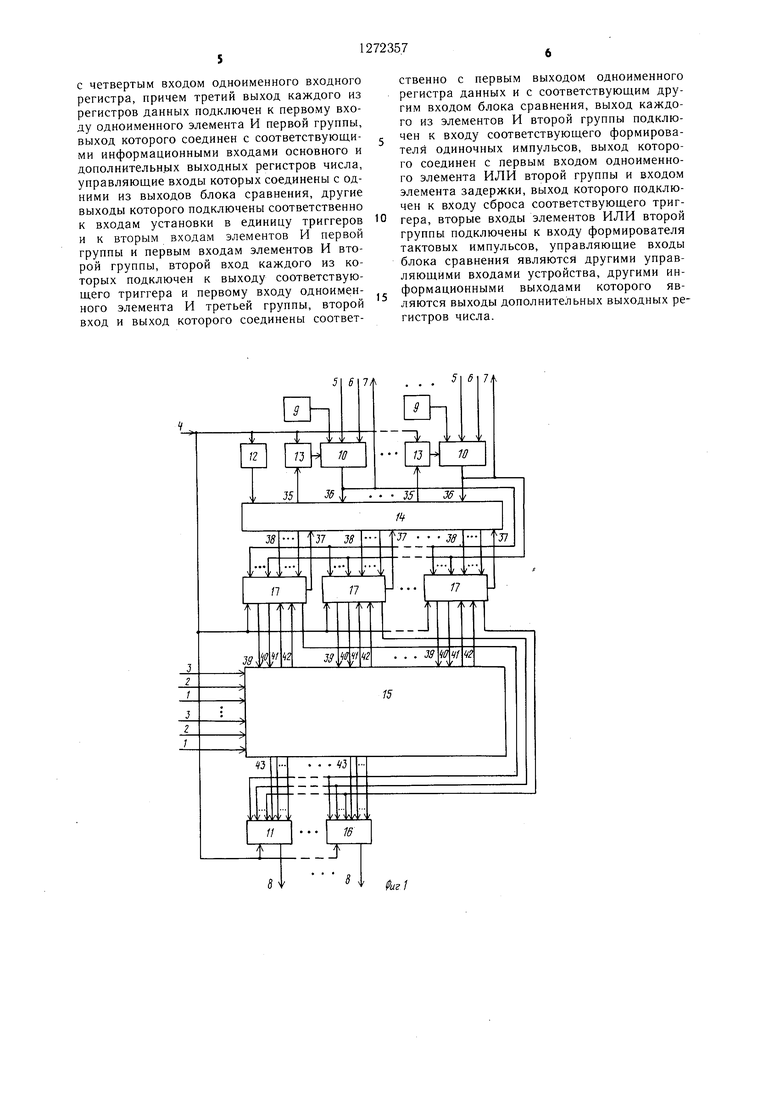

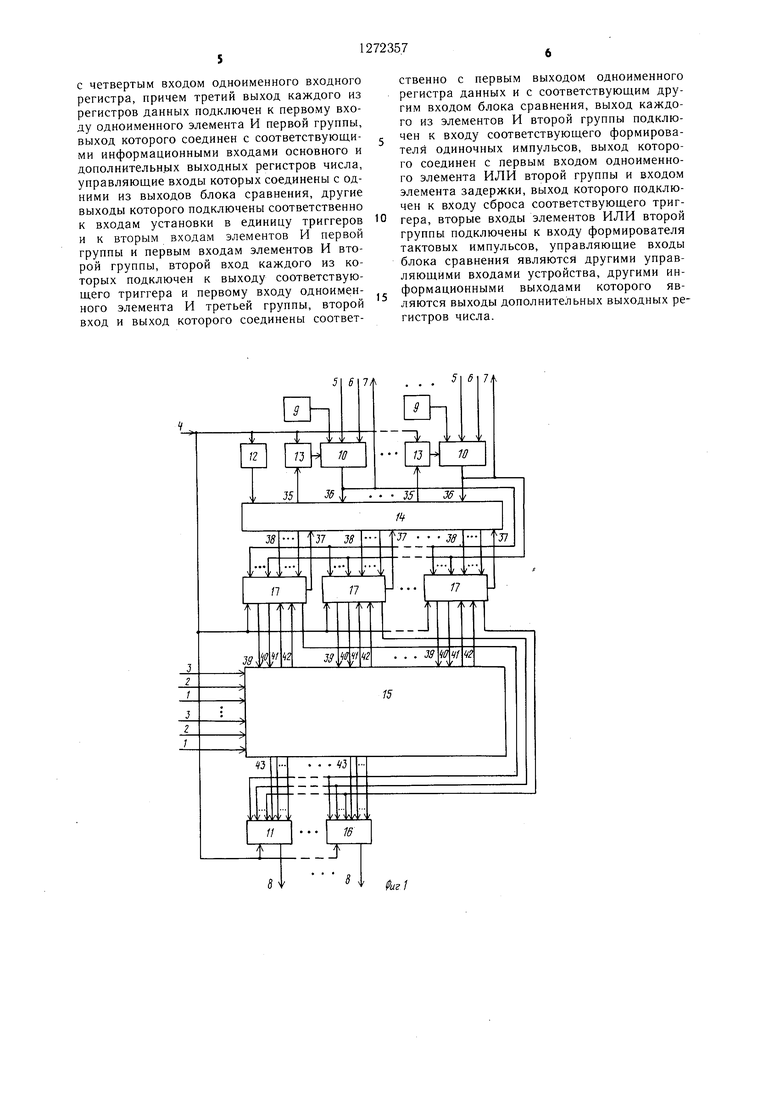

to оо ел Изобретение относится к вычислительнай технике, в частности к регистровым запоминающим устройствам. Цель изобретения - расширение области применения устройства за счет обеспечения независимого считывания нескольких информационных слов одновременно. На фиг. 1 и 2 изображены функциональные схемы предложенного устройства; на фиг. 3 - функциональная схема блока сравнения. На фиг. 1 изображены управляющие 1-3 входы, вход 4 сброса устройства, информационные 5 и управляющие 6 входы, индикаторные 7 и информационные 8 выходы устройства. Предложенное устройство содержит (фиг. 1) ключи 9, входные регистры 10 числа, основной выходной 11 регистр числа, формирователь 12 тактовых импульсов, первую группу элементов ИЛИ 13, блок 14 записи, блок 15 сравнения, дополнительные выходные регистры 16 числа, блоки 17 памяти, каждый из которых содержит (фиг. 2) регистр 18 данных, триггер 19, формирователь 20 одиночного импульса, элементы И 21-23 первой-третьей групп соответственно и элемент ИЛИ 24 второй группы и элемент 25 задержки. Блок 15 сравнения содержит (фиг. 3) группы регистров 26 номера слова, группы элементов 27 сравнения, группы элементов 28 задержки, группы элементов И 29, первую 30 и вторую 31 группы элементов ИЛИ, группы элементов 32 задержки, формирователи 33 сигналов считывания и элементы НЕ 34. На фиг. 1-3 обозначены выходы 35, входы 36-37 и выходы 38 блока 14 записи, входы 39 и 40 и выходы 41-43 блока 15 сравнения. Число регистров 26 номера слова, число элементов 27 сравнения, элементов 28 задержки, элементов И 29, элементов ИЛИ 30 и 31, элементов 32 задержки в каждой группе равно числу регистров 18 данных. Предложенное устройство работает следующим образом. Каждое информационное слово, представленное параллельным двоичным кодом, поступающее в устройство, содержит разряды информации, разряды номера этого информационного слова и разряд маркера, всегда равный единице. Наличие уровня логического нуля в разряде маркера любого регистра 10 (фиг. 1) и на одноименном выходе 7 указывает, что этот регистр 10 свободен для записи в него очередного информационного слова. При записи информации в устройство через вход 5 поступает очередное информационное слово, которое по сигналу логической единицы, поступающему через одноименный вход 6, записывается в соответствующий регистр 10. Одновременно в этот же регистр 10 записывается номер этого входа 5, набранный предварительно вручную с помощью ключей 9. Таким образом, при наличии информационного слова в любом регистре 10 на его информационном выходе будут присутствовать уровень логической единицы в разряде маркера, байты информации, номера этого информационного слова и номера соответствующего входа 5. Запись информационного слова в каждый свободный регистр 10 производится независимо от состояния других регистров 10. Свободному регистру 18 соответствует логический нуль на его выходе 37. По каждому тактовому импульсу, поступающему на выход формирователя 12, блок 14 формирует сигнал записи на выходе 38, одноименном с данным регистром 10 и свободным регистром 18, в который записывается информационное слово. По переднему фронту сигнала записи в свободный регистр 18 записывается информационное слово, которое по заднему фронту сигнала записи переписывается на его выходы, при этом на его выходе 39 присутствует код номера записанного информационного слова и код номера входа 5, через который оно поступило в устройство, а на выходах 37 и 40 - маркер занятости (т. е. уровень логической единицы), показывающий, что данный регистр 18 занят. Если нет свободных для записи инфор.мации регистров 18, то информационные слова остаются каждое в своем регистре 10 до момента освобождения какого-нибудь регистра 18 после считывания информации из устройства, при этом работа формирователя 12 не прекращается. Одновременно с записью информации к свободный регистр 18 на соответствующем выходе 35 формируется сигнал, по заднему фронту которого через элемент ИЛИ 13 сбрасываются все разряды соответствующего регистра 10, при этом на выходе 7 появляется уровень логического нуля. Считывание информации из регистра 8 производится по прямоугольному импульсу (уровень логической единицы), поступающему через какой-нибудь из входов 1 в блок 15, при наличии параллельного двоичного кода номера информационного слова и номера входа 5 на одноименном входе 3. В блоке 15 по этому импульсу на каком-либо входе 1 через элемент НЕ 34 (фиг. 3) блокируются на время считывания информации все регистры 26 в группе, одноименной с входом 1. Каждый регистр 26 до блокировки повторяет на своем втором выходе код номера информационного слова и номера входа 5, поступающие по входу 39, а на первом выходе - значение разряда маркера занятости, поступающее на вход этого регистра 26 через одноименный элемент 28 задержки с входа 40.

Соответствующий формирователь 33 формирует прямоугольный импульс считывания (уровень логической единицы), передний фронт которого задержан относительно переднего фронта импульса сигнала на входе 1 на время блокировки всех регистров 26, а задний фронт которого совпадает по времени с задним фронтом этого же импульса. После блокировки всех регистров 26 по импульсу с выхода формирователя 33 в каждом элементе 27 сравнения в одноименной входу 1 группы сравнивается код номера информационного слова и номера входа 5, присутствующие на одноименном входе 3, с кодом номера информационного слова и номера входа 5, поступающим с выхода одноименного регистра 26 (при наличии уровня логической единицы в разряде маркера занятости на другом выходе этого же регистра 26). При совпадении в каком-либо из элементов 27 сравнения этих кодов на его выходе появляется прямоугольный импульс логической единицы, задний фронт которого появляется раньше заднего фронта импульса с выхода формирователя 33 на время, равное времени задержки в элементе ИЛИ 31, элементе И 21 плюс время задержки на снятие блокировки с регистров 26.

По этому импульсу с выхода элемента 27 сравнения через одноименный с ним элемент ИЛИ 31 и соответствующий выход 42 производится считывание из регистра 18 информации, номера информационного слова и номера соответствующего входа 5, совпавших с номером информационного слова и с номером входа 5 на входе 3. По этому же импульсу с выхода элемента 27 через одноименный элемент 32 задержки в группе, одноименной с входом 1 по переднему фронту импульса на соответствующем выходе 43 информация из регистра 18 переписывается в соответствующий из регистров 11 и 16, из которого поступает на выход 8 по заднему фронту импульса на выходе 43.

При наличии на входе 2, одноименном с входом 1, уровня логической единицы через одноименный с блоком .27 элемент И 29 на соответствующий элемент ИЛИ 30 поступает импульс с выхода этого блока, через соответствующий выход 41 которого сбрасыБаются все разряды регистра 18, из которого была считана информация;

В процессе функционирования возможна ситуация, когда на входы какого-либо элемента ИЛИ 31 могут сразу поступить импульсы с нескольких элементов 27 сравнения разных групп (при считывании информации по нескольким входам 1 из одного регистра 18). Если эти импульсы на входах элемента ИЛИ 31 перекрывают один другой по времени, то на выходе будет присутствовать уровень логической единицы до появления заднего фронта последнего по времени импульса на соответствующем

ему входе этого элемента ИЛИ 31 (т. е. процесс считывания информации из одного регистра 18 прекращается только по последнему по времени сигналу на соответствующем входе 1).

Считывание информации из любого регистра 18 производится независимо от состояния других регистров 18 и может производиться одновременно из нескольких регистров 18 по сигналам на соответствующих входах 1. При этом считывание информации из любого регистра 18 может производиться по сигналу на любом входе 1.

Таким образом, считывание информации из устройства и запись информации в него могут производиться одновременно и независимо друг от друга.

Формула изобретения

Буферное запоминающее устройство, содержащее регистры данных, блок записи, блок сравнения, входные регистры числа, основной выходной регистр числа, группы элементов ИЛИ и формирователь тактовых импульсов, вход которого, первые входы элементов ИЛИ первой группы и вход сброса основного выходного регистра числа являются входом сброса устройства, информационными входами и индикаторными выходами которого являются первые входы и одни из выходов входных регистров числа, вторые входы которых являются одними из управляющих входов устройства, а третьи входы подключены к выходам элементов ИЛИ первой группы, вторые входы которых соединены с выходами первой группы блока записи, выходы второй группы которого подключены к одним из управляющих входов регистров данных, другой управляющий вход и информационные входы каждого из которых соединены соответственно с выходом одноименного элемента ИЛИ второй группы и с выходами входных регистров числа и входами первой группы блока записи, тактовый вход и входы второй группы которого подключены соответственно к выходу формирователя тактовых импульсов и к первым выходам регистров данных, причем вторые выходы регистров данных соединены с одними из входов блока сравнения, один из выходов которого подключен к одному из управляющих входов основного выходного регистра числа, выход которого является одним из информационных выходов устройства, отличающееся тем, что. с целью расщирения области применения устройства за счет обеспечения независимого считывания нескольких информационных слов одновременно, в него введены дополнительные выходные регистры числа, триггеры, формирователи одиночных импульсов, группы элементов И, элементы задержки и ключи, выход каждого из которых соединен

с четвертым входом одноименного входного регистра, причем третий выход каждого из регистров данных подключен к первому входу одноименного элемента И первой группы, выход которого соединен с соответствующими информационными входами основного и дополнительных выходных регистров числа, управляющие входы которых соединены с одними из выходов блока сравнения, другие выходы которого подключены соответственно к входам установки в единицу триггеров и к вторым входам элементов И первой группы и первым входам элементов И второй группы, второй вход каждого из которых подключен к выходу соответствующего триггера и первому входу одноименного элемента И третьей группы, второй вход и выход которого соединены соответственно с первым выходом одноименного регистра данных и с соответствующим другим входом блока сравнения, выход каждого из элементов И второй группы подключен к входу соответствующего формирователя одиночных импульсов, выход которого соединен с первым входом одноименного элемента ИЛИ второй группы и входом элемента задержки, выход которого подключен к входу сброса соответствующего триггера, вторые входы элементов ИЛИ второй группы подключены к входу формирователя тактовых импульсов, управляющие входы блока сравнения являются другими управляющими входами устройства, другими информационными выходами которого являются выходы дополнительных выходных регистров числа.

Us 10 8

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1203595A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1474742A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236555A1 |

| Запоминающее устройство | 1985 |

|

SU1288759A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1238160A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1265858A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

Изобретение относится к вычислительной технике, в частности к регистровым запоминающим устройствам, и может быть применено в вычислительных комплексах для обмена информацией между процессорами с различными скоростями вычислений. Целью изобретения является расширение области применения устройства за счет обеспечения независимого считывания нескольких информационных слов одновременно. Цель достигается за счет введения дополнительных выходных регистров числа, тригггеров, формирователей одиночных импульсов, группы элементов И, элементов НЕ и ключей в буферное запоминающее устройство, содержащее регистры данных, блок записи, входные регистры числа, основной выходной регистр числа li блок сравнения, а также за счет того, то в блоке сравнения число групп регистров номера слог.а. групп элементов сравнения, групп элементов И, элементов ИЛИ, элементов задержки н число формирователей СМГНЗЛОЕ считывания равно числ выходных регистров числа. При считывании выполняется сравнение кодов номера информационного слова и входа, по которому оно поступило в С1ройство, с кодами номеров, Ч1;сла и входа, поступающими на управляющие входы блока сравнения и при их совпадении производится считывание информации из соотС ветствующего регистра данных. 3 ил.

| Буферное запоминающее устройство | 1983 |

|

SU1109798A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1203595A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-11-23—Публикация

1985-03-07—Подача