3.Устройство по п.2, отличающееся тем, что каждый логический блок содержит формирователь сигналов записи, первый элемент ИЛИ, первую и вторую группы элементов И, причем первый и второй входы формирователя сигналов записи являются первым и вторым управляющими входами блока, третьим управляющим входом которого является первый вход первого элемента И второй группы, причем выход первого элемента ИЛИ подключен к третьему входу формирователя сигналов записи, выход которого соединен с первыми входами элементов И первой группы, второй вход каждого из которых, кроме первого, подключен к выходу предыдущего и первому входу последующего элементов И второй группы, вторые входы которых соединены с вторым входом формирователя сигналов записи, второй вход первого элемента И первой группы подключен к третьему входу первого элемента И второй группы и первому входу первого элемента ИЛИ, другие входы которого соединен с третьими входами одноименных элементов И второй группы, выход формирователя сигналов записи и выходы элементов И второй группы являются соответственно управляющим выходом и одними из выходов блока, входами и другими выходами которого являются соответственно входы первого элемента ИЛИ и выходы элементов И первой группы.

4.Устройство по пп. 1-3, отличающееся тем, что блок считывания содержит форИзобретение относится к вычислительной технике, в частности к регистровым запоминающим устройством и может применяться, например, для буферизации данных, поступающих одновременно от различных датчиков в параллельном коде.

Цель изобретения является расщирение функциональных возможностей устройства за счет осуществления в нем записи нескольких информационных слов при одновременном считывании из него информационного слова.

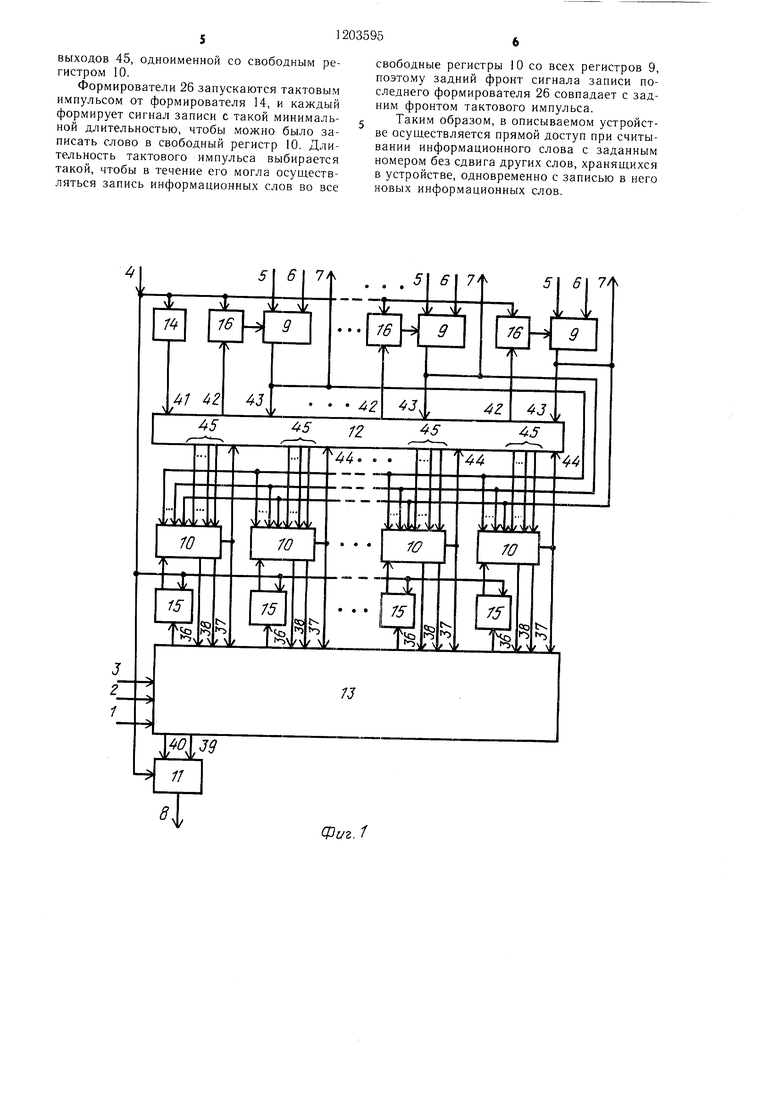

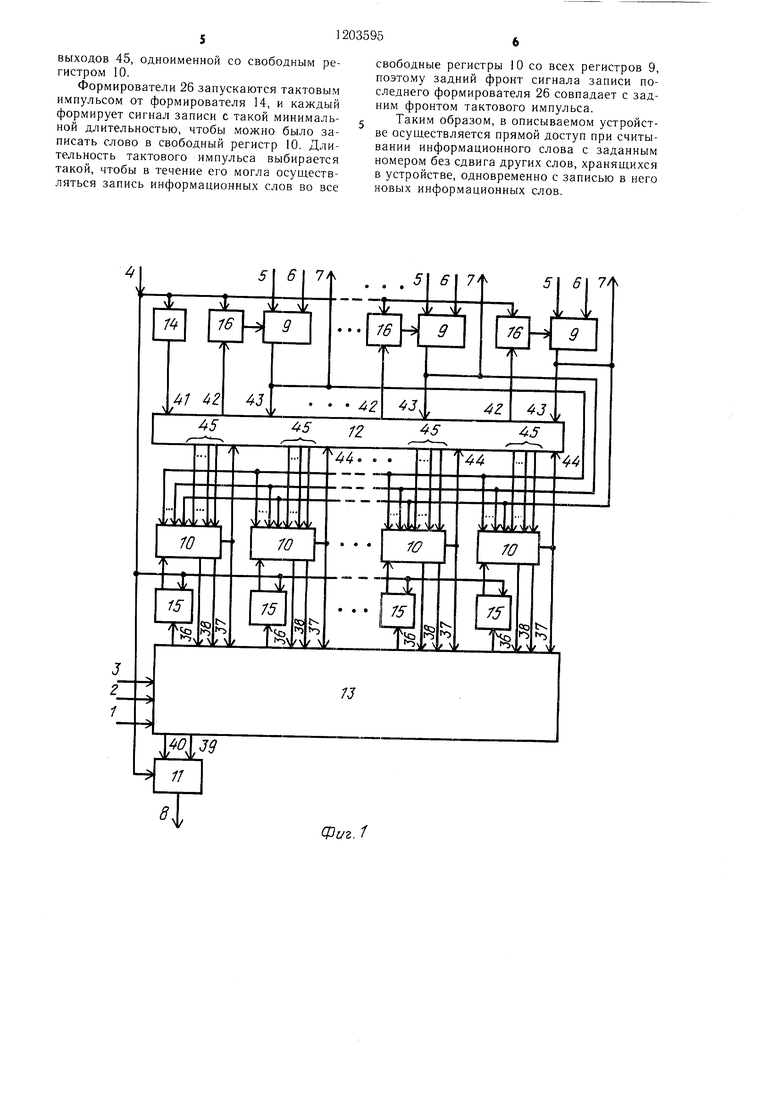

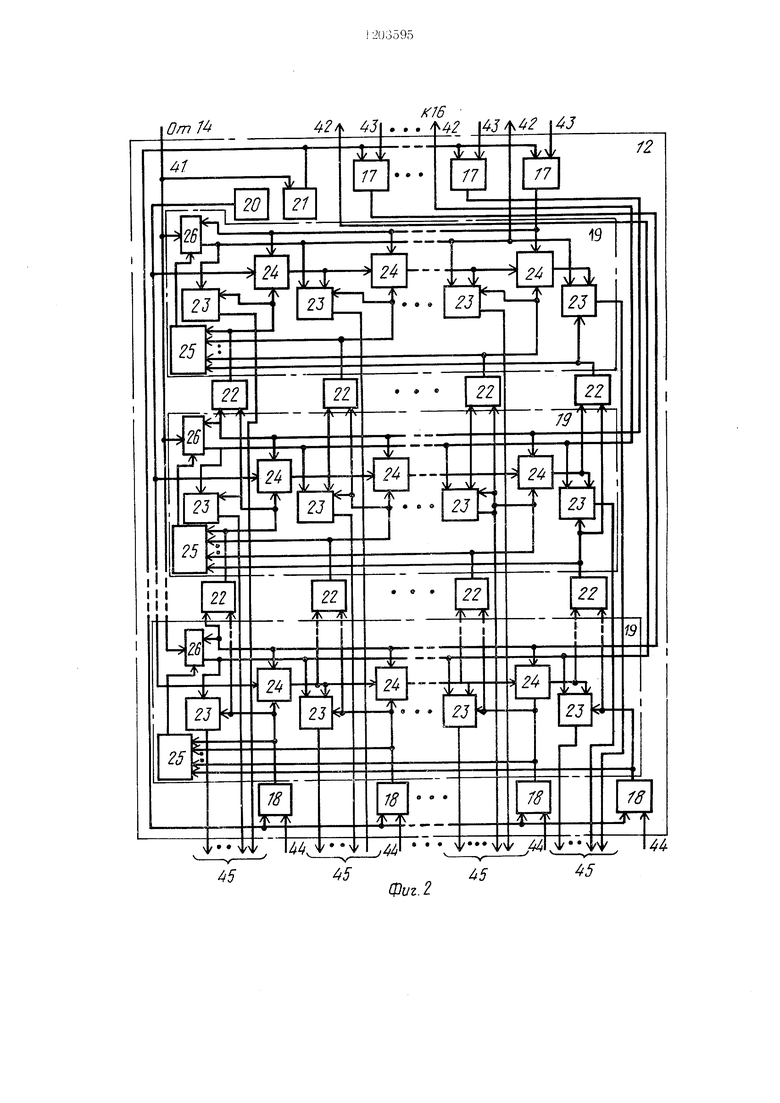

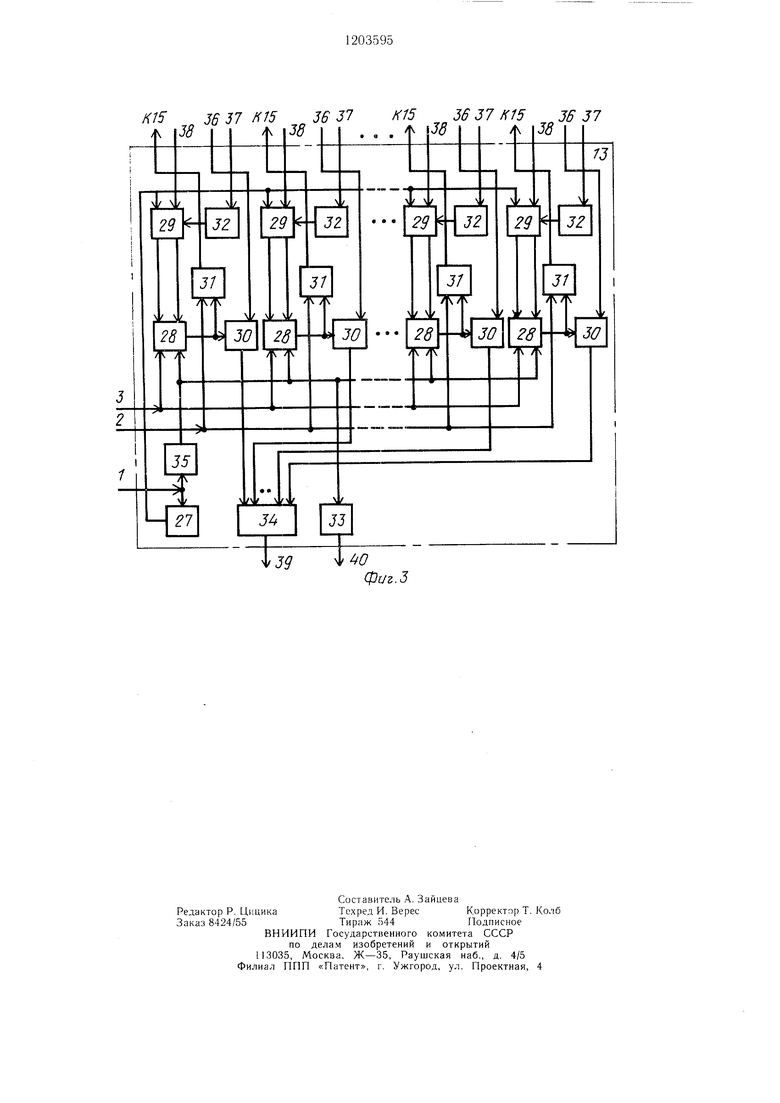

На фиг.1 изображена функциональная схема предложенного устройства; на фиг.2 и фиг.З - функциональные схемы наиболее предпочтительных вариантов выполнения блока записи и блока считывания соответственно.

На схеме устройства (фиг.1) обозначены управляющие входы 1-3, вход 4 сброса устройства, информационные 5 и управляю- u-iHe 6 входы, индикаторные 7 и информационные 8 выходы устройства. Предложенмирователь сигналов считывания, блоки сравнения, регистры номера слова, второй элемент НЕ, третью и четвертую группы элементов И, группу элементов задержки и второй элемент ИЛИ, причем первые входы регистров номера слова и входы элементов задержки группы являются одними из управляющих входов блока считывания, информационными входами которого являются первые входы элементов И третьей группы, второй вход каждого из которых и первый вход одноименного элемента И четвертой группы соединены с выходом одноименного блока сравнения, первый и второй входы которого подключены к выходам одноименного регистра номера слова, управляющий вход которого соединен с выходом второго элемента НЕ, а второй вход - с выходом одноименного элемента задержки группы, третьи входы блоков сравнения и вход элемента задержки подключены к выходу формирователя сигналов считывания, вход которого соединен с входом второго элемента НЕ, выходы элементов И третьей группы подключены к входам второго элемента ИЛИ, выход которого и выход элемента задержки являются соответственно информационным и управляющим выходами блока считывания, выходами сброса которого являются выходы элементов И четвертой группы, вторые входы которых, четвертые входы блоков сравнения и вход формирователя сигналов считывания являются соответственно другими управляющими входами блока считывания.

ное устройство содержит входные регистры 9, регистры 10 данных, выходной регистр 11, блок 12 записи, блок 13 считывания, формирователь 14 тактовых импульсов, пер- вую 15 и вторую 16 группы элементов ИЛИ.

Блок 12 записи (фиг. 2) содержит первую 17 и вторую 18 группы триггеров,логические блоки 19, формирователь 20, потенциального сигнала, первый элемент НЕ 21,

группы дополнительных элементов ИЛИ 22.

Каждый логический блок 19 содержит

первую 23 и вторую 24 группы элементов И,

первый элемент ИЛИ 25 и формирователь 26

сигналов записи.

Блок 13 считывания (фиг. 3) содержит

второй элемент НЕ 27, блоки 28 сравнения, регистры 29 номера слова, третью 30 и четвертую 3 группы элементов И, группу элементов 32 задержки, элемент 33 задержки, второй элемент ИЛИ 34 и формирователь 35 сигналов считывания.

На фиг. 3 и фиг. 1 обозначены также информационные входы 36, управляющие

входы 37 и 38, информационный 39 и управляющий 40 выходы блока 13 считывания.

На фиг. 1 и фиг. 2 обозначены также тактовый вход 41, управляющие выходы 42, управляющие входы 43 и 44 и группы выходов 45 блока 12 записи.

Предложенное устройство работает следующим образом.

Каждое информационное слово, представленное параллельным двоичным кодом, поступающее в устройство, содержит разряды информации,разряды номера слова, разряды номера входа 5, по которому поступило это слово, и разряд маркера, всегда равный единице.

Перед началом работы через вход 4 по- ступас импульс сброса, по заднему фронту которого устанавливаются в нуль все разряды, включая разряд маркера, регистров 9-11, и запускается формирователь 14, который через промежуток времени, равный времени установки в нуль регистров 9-11 начинает формировать на своем выходе непрерывную серию одинаковых прямоугольных импульсов с одинаковой скважностью.

Наличие (также и после сброса) уровня логического нуля в разряде маркера (на выходе 7) любого регистра 9 указывает на то, что этот .регистр 9 свободен для записи очередного информационного с.юва через соответствуюн ий вход 5 по переднему фронту сигнала, ноступаюн ему через соответствующий вход 6, а по заднему фронту этого же сигнала информационное слово перепи- олвается на выходы регистра 9.

При наличии информационного слова на его выходах присутствуют байты информации, номера слова, номера входа 5 и уровень «единицы в разряде маркера на входе 43 блока 12.

Запись слова в каждый регистр 9 производится независимо от состояния других регистров 9. По каждому тактовому импульсу на выходе формирователя 14 блок 12 формирует сигнал записи на соответствующем регистру 9 выходе в группе выходов 45, одноименной со свободным регистром 10, который определяется по наличию логического нуля на выходе 44 свободного регистра 10. По переднему фронту этого сигнала записи в свободный регистр 10 записывается информационное слово из регистра 9, которое переписывается на выходы регист)а 10 по заднему фронту сигнала записи. При этом на выходе 36 присутствуют байты информации, на выходе 38 - байты номера слова и номера входа 5, а в разряде маркера на выходе 44 - уровень логической единицы.

Запись в любой регистр 10 происходит независимо от состояния других регистров 10 и осуществляется в течение одного тактового импульса. Если свободного persicTpa 10 нет, то слово остается в регистре 9 до момента освобождения регистра 10 после считывания информации из устройства.

0

Одновременно с записью информации в регистр 10 на соответствующем выходе 42 блока 12 формируется импульс, по заднемч фронту которого через элемент ИЛИ 16 сбрасывается регистр 9, при этом на выходе 7 появляется сигнал «О, указывающий, что соответствующий регистр 9 свободен для записи в него очередного слова.

Считывание слова из любого регистра 10 производится но сигналу, поступаюп1ему

0 через вход 1 в блок 13 при наличии на вхо де 3 кодов номера слова и номера входа 5, которые сравниваются в блоке 13 соответственно с кодами номера слова и номера входа 5 на выходе 38 каждого занятого регистра 10. При совпадении этих кодов информа ция с выхода 36 соответствующего регистра 10 переп1 сывается через блок 13 в регистр 11. При этом все разряды этого регистра 10 сбрасываются в нуль по задпему фронту сигнала, формируемого блоком 13 на выходе одноименного элемента ИЛИ 15, если на входе 2 есть уровень логической единицы (при отсутствии которого регистр 10 после считывания не сбрасывается в нулевое состояние и информагшя из него может быть повторно считана).

5 В регистр 11 информация записывается с входов 39 по переднему фронту сигнала на входе 40. по заднему фронту которого байты информации переписываются на выход 8 устройства.

Выбор свободного регистра 10 осуществ0 ляется следуюпи1м образом в блоке 12. С выхода 44 регистра 10 значение маркера поступает на вход одноименного триггера 18 (фпг. 2), с выхода которого значение .маркера поступает на входы одноименных элементор, И 23 и 24 и одноименные входы элементов

ИЛИ 25 всех блоков 19 через соответствующие элементы ИЛИ 22.

С выхода формирователя 20 поступает сигнал логической единицы, который присутствует в течение всего времени работы устройства.

На выходе каждого триггера 17 устанавливается значение маркера занятости о,:.поименно1-о pei-истра 9. При наличии па выходе како1Ч)-лпбо триггера 17 уровня «1 сигнал с выхода формирователя 20 пере5 дается через элементы И 24 одноименного блока 19 (при наличии на третьих входах элементов И 24 уровней логической единицы) до того элемента И 24, на третьем входе которого присутствует «О.

Формирователь 26 формирует сипгз,

записи то.чько при наличии уровня «1, поступающего с выхода одноименного тригге- ia 17. и при наличии уровня единппы, но ступающего с выхода элемента ИЛИ 25 (что указывает яа наличие свободного для записи, регистра 10).

5 Таким образом, сигнал записи с выхода формирователя 26, одноименного с выбранным триггером 17, пройдет только через один лз элементов И 23 на выход из группы

выходов 45, одноименной со свободным регистром 10.

Формирователи 26 запускаются тактовым импульсом от формирователя 14, и каждый формирует сигнал записи с такой минимальной длительностью, чтобы можно было записать слово в свободный регистр 10. Длительность тактового импульса выбирается такой, чтобы в течение его могла осуществляться запись информационных слов во все

8

I

Фиг. 1

свободные регистры 10 со всех регистров 9, поэтому задний фронт сигнала записи последнего формирователя 26 совпадает с задним фронтом тактового импульса.

Таким образом, в описываемом устройстве осуществляется прямой доступ при считывании информационного слова с заданным номером без сдвига других слов, хранящихся в устройстве, одновременно с записью в него новых информационных слов.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1272357A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1474742A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Устройство для приема и обработки информации | 1988 |

|

SU1532958A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1238160A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Стековое запоминающее устройство | 1979 |

|

SU881863A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1109798A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-01-07—Публикация

1984-06-28—Подача