и информационными 13 выходами. Устройство предназначено для передачи одинаковой информации одновременно от нескольких процессоров на несколько периферийных накопителей на МД или МЛ. Устройство осуществляет прием серии пакетов информационных слов параллельно по всем входам 1 блоков 15 с допустимым рассогласованием их по времени, выявляет и корректирует ошибки в принимаемых информационных словах и выдает одновременно по всем выходам 13 откорректированные пакеты информационных слов, при этом контролируется запаздывание записи и чтения пакетов слов в каждом блоке 15. Прием и выдача запаздывающих сверх

допустимого пакетов информации прекращаются. Цель достигается путем выполнения коррекции выявленных ошибок в принятых словах, восстановления потерянного разряда слова, что выполняется в блоках 14 коррекции сравнением всех слов, считанных одновременно из всех блоков 15, а также путем блокировки приема по како-i му-либо из входов 1 пакета слов, содержащего больше допустимого число слов с ошибками путем повторного чтения из блоков 15 памяти пакета слов или отдельного слова, для чего подаются сигналы на входы 6 чтения, 7 и 8 повторного чтения устройства. 1 з.п. ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1203595A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1272357A1 |

| Запоминающее устройство | 1985 |

|

SU1288759A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1238160A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236555A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для сопряжения абонента с магистралью | 1989 |

|

SU1679494A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в многопроцеесорных системах обработки данных. Цель изобретения - расширение области применения устройства за счет обеспечения одновременной параллельной передачи нескольких идентичных информационных слов с коррекцией ошибок. Устройство содержит блоки 14 коррекции, блок 16 управления и блоки 15 оперативной памяти с информационными 1 и тактовыми 2 входами, входами 3 сброса, входами 6 чтения, входами 7 повторного чтения информационного слова, входами 8 повторного чтения пакета слов, выходами 9 окончания записи, выходами 10 прерывания записи, выходами 11 индикации режима чтения, тактовыми 12 и информационными 13 выходами. Устройство предназначено для передачи одинаковой информации одновременно от нескольких процессоров на несколько периферийных накопителей на МД или МЛ. Устройство осуществляет прием серии пакетов информационных слов параллельно по всем входам 1 блоков 15 с допустимым рассогласованием их по времени, выявляет и корректирует ошибки в принимаемых информационных словах и выдает одновременно по всем выходам 13 откорректированные пакеты информационных слов, при этом контролируется запаздывание записи и чтения пакетов слов в каждом блоке 15. Прием и выдача запаздывающих сверх допустимого пакетов информации прекращается. Цель достигается путем выполнения коррекции выявленных ошибок в принятых словах, восстановления потерянного разряда слова, что выполняется в блоках 14 коррекции сравнением всех слов, считанных одновременно из всех блоков 15, а также путем блокировки приема по какому-либо из входов 1 пакета слов, содержащего больше допустимого число слов с ошибками путем повторного чтения из блоков 15 памяти пакета слов или отдельного слова, для чегно подаются сигналы на входы 6 чтения, 7 и 8 повторного чтения устройства. 1 з.п.ф-лы.5 ил.

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в многопроцессорных системах обработки данных.

Целью изобретения является расширение области применения устройства за счет обеспечения одновременной параллельной передачи нескольких идентичных информационных слов с коррекцией ошибок.

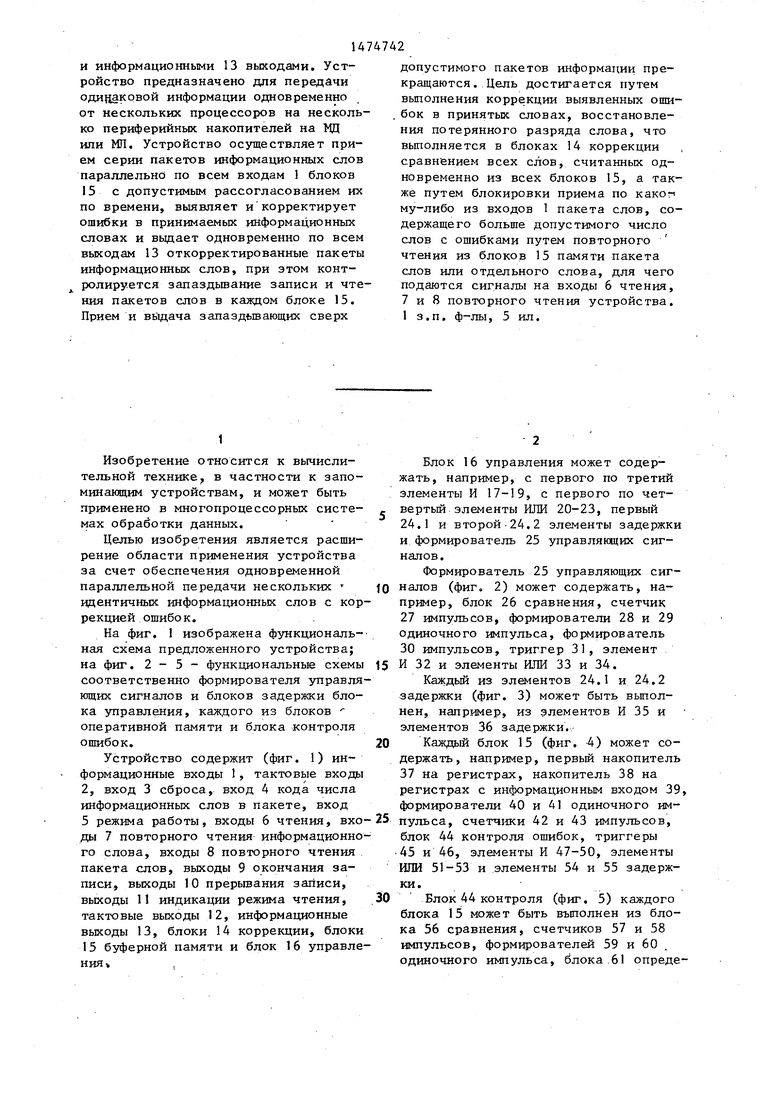

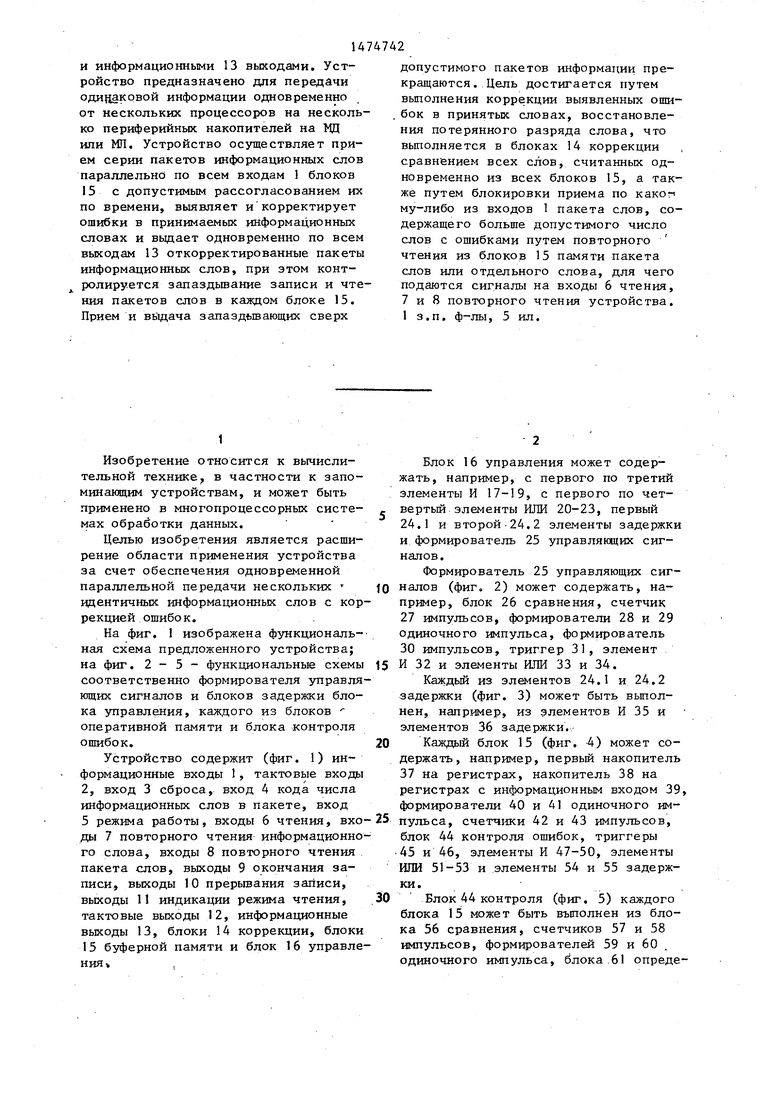

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - 5 - функциональные схемы соответственно формирователя управляющих сигналов и блоков задержки блока управления, каждого из блоков оперативной памяти и блока контроля ошибок.

Устройство содержит (фиг. 1) информационные входы 1, тактовые входы 2, вход 3 сброса, вход 4 кода числа информационных слов в пакете, вход 5 режима работы, входы 6 чтения, входы 7 повторного чтения информационного слова, входы 8 повторного чтения пакета слов, выходы 9 окончания записи, выходы 10 прерывания записи, выходы 11 индикации режима чтения, тактовые выходы 12, информационные выходы 13, блоки 14 коррекции, блоки 15 буферной памяти и блок 16 управления

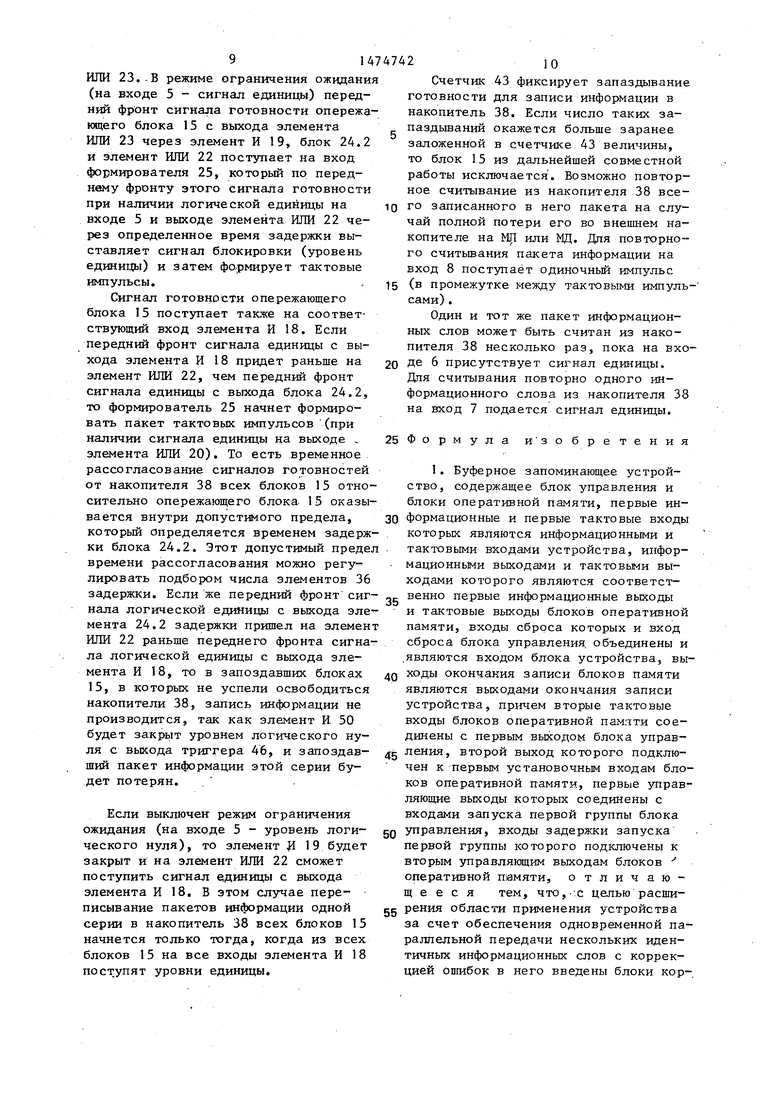

Блок 16 управления может содержать, например, с первого по третий элементы И 17-19, с первого по четвертый элементы ИЛИ 20-23, первый 24.1 и второй 24.2 элементы задержки и формирователь 25 управляющих сигналов.

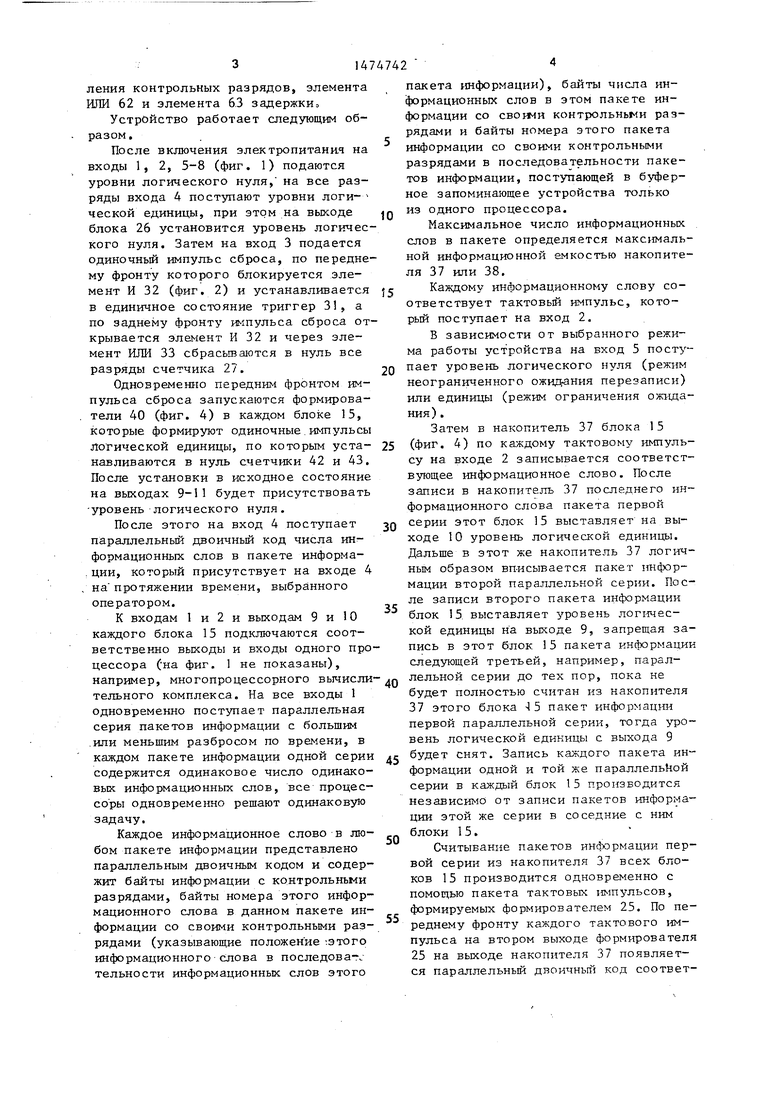

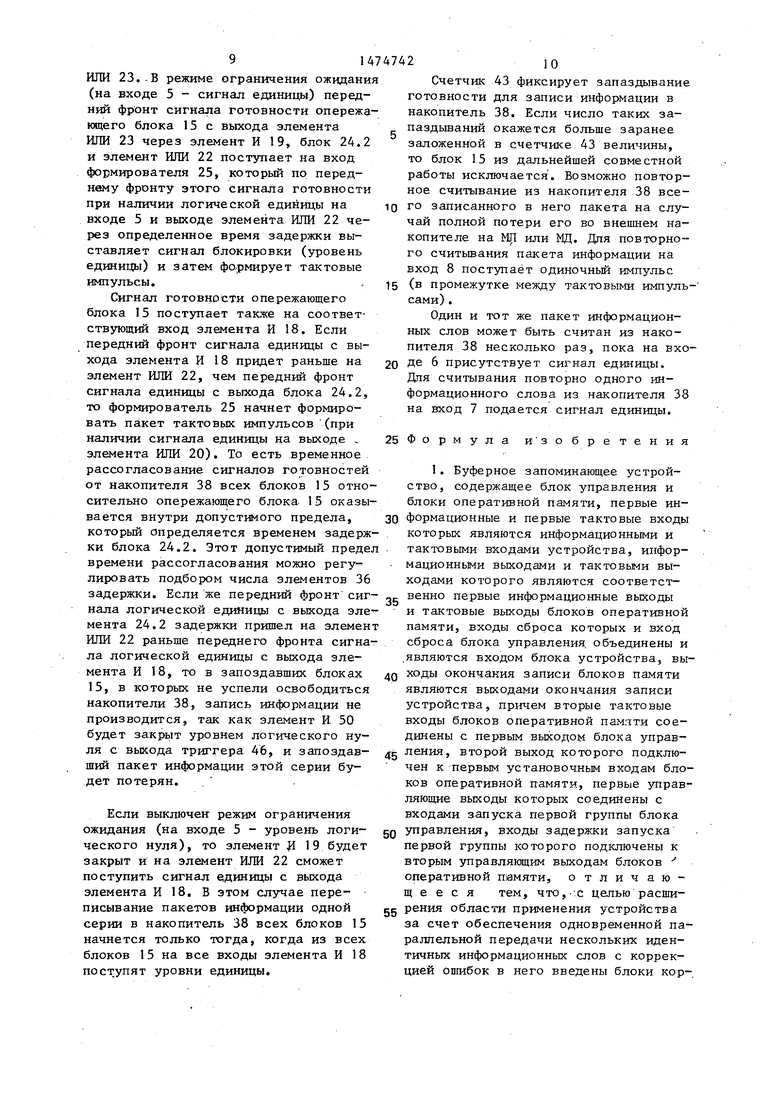

Формирователь 25 управляющих сигO налов (фиг. 2) может содержать, например, блок 26 сравнения, счетчик 27 импульсов, формирователи 28 и 29 одиночного импульса, формирователь 30 импульсов, триггер 31, элемент

5 И 32 и элементы ИЛИ 33 и 34.

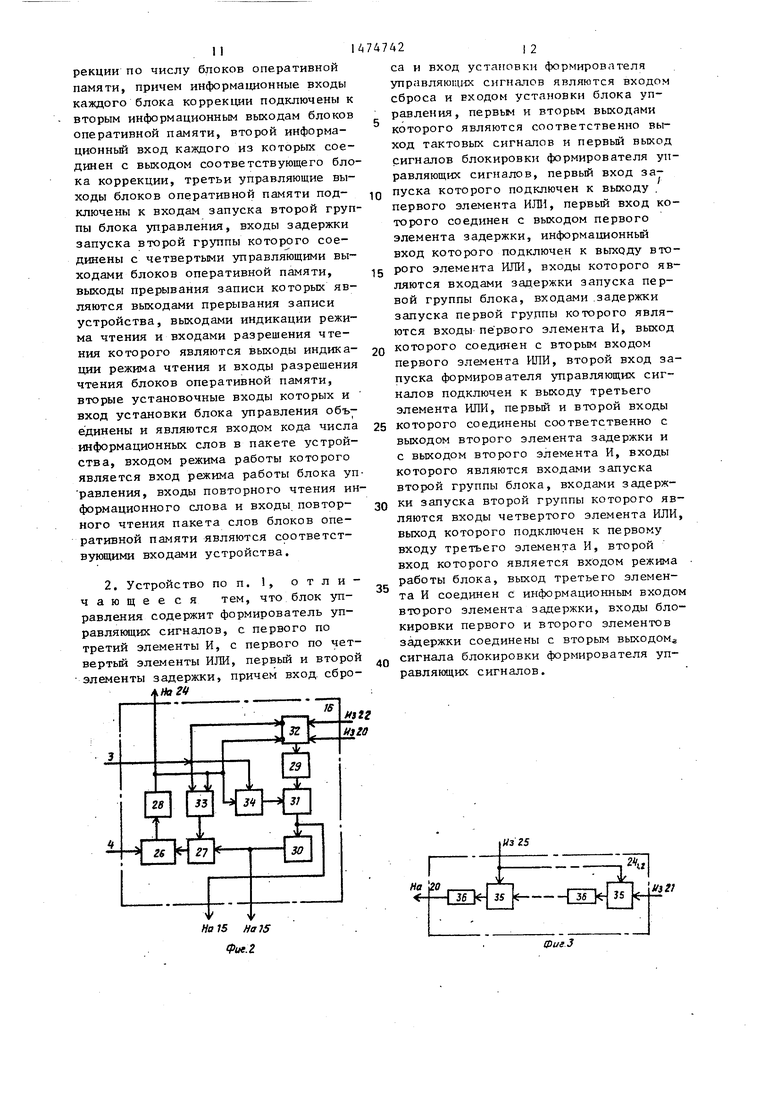

Каждый из элементов 24.1 и 24.2 задержки (фиг. 3) может быть выполнен, например, из элементов И 35 и элементов 36 задержки.

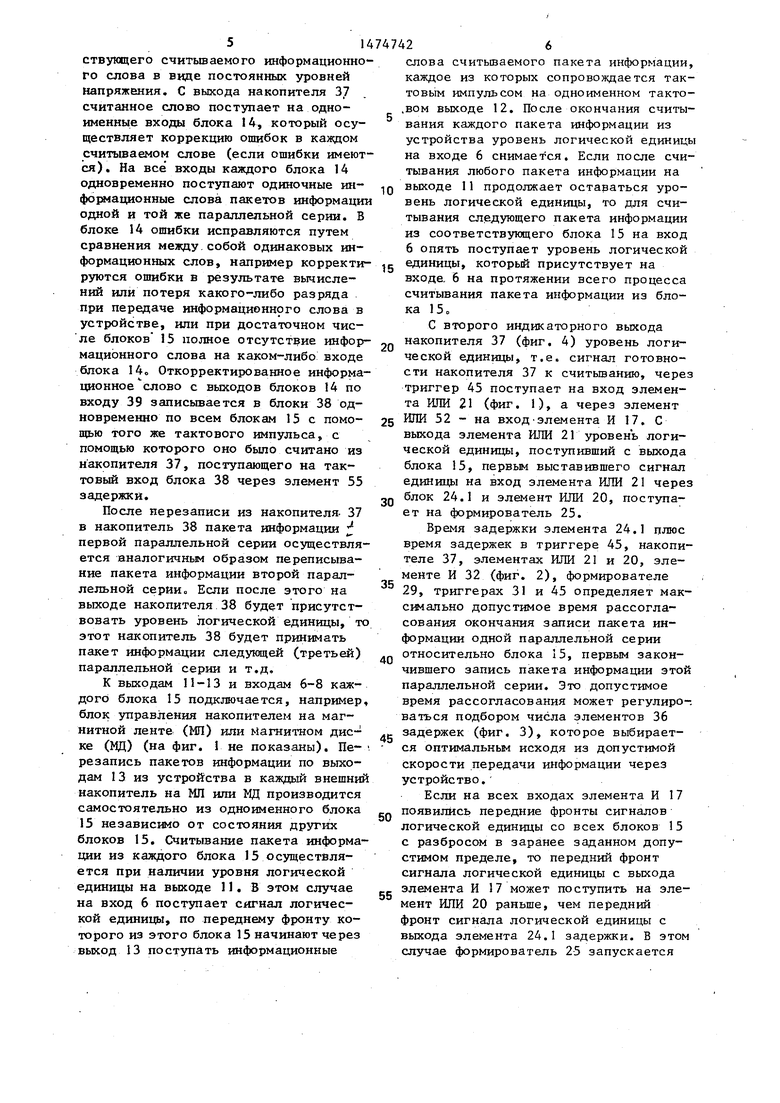

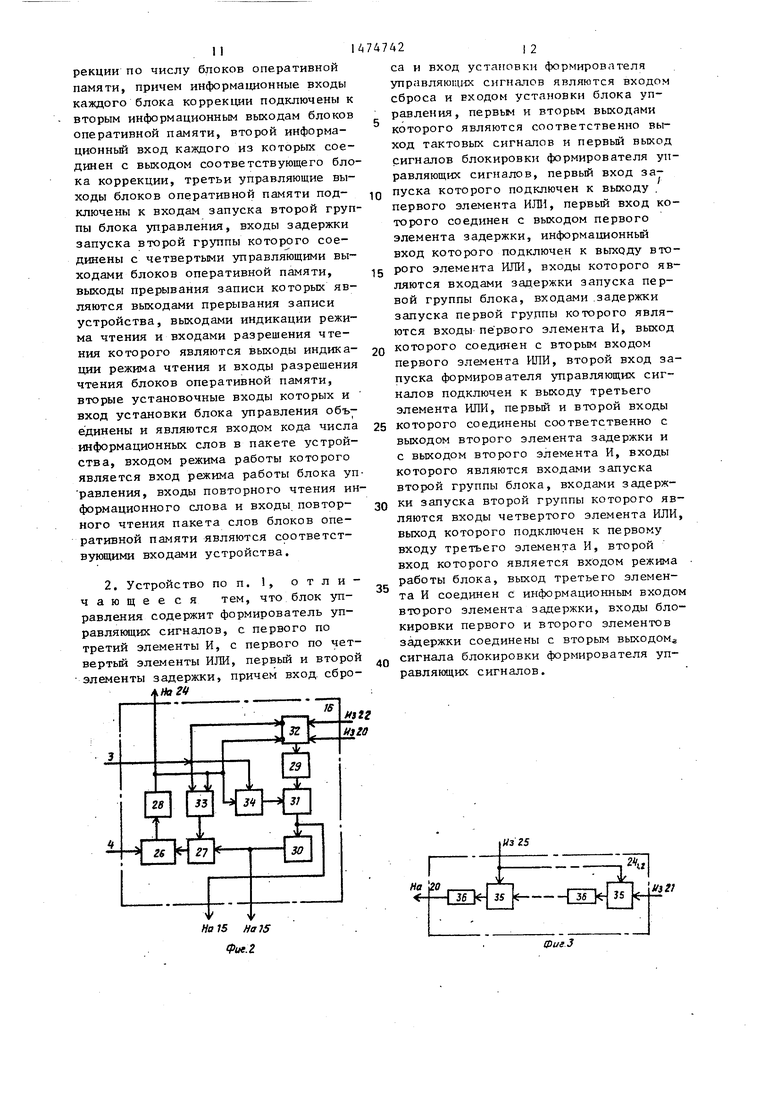

0 Каждый блок 15 (фиг. 4) может содержать, например, первый накопитель 37 на регистрах, накопитель 38 на регистрах с информационным входом 39, формирователи 40 и 41 одиночного им5 пульса, счетчики 42 и 43 импульсов, блок 44 контроля ошибок, триггеры 45 и 46, элементы И 47-50, элементы ИЛИ 51-53 и элементы 54 и 55 задержки.

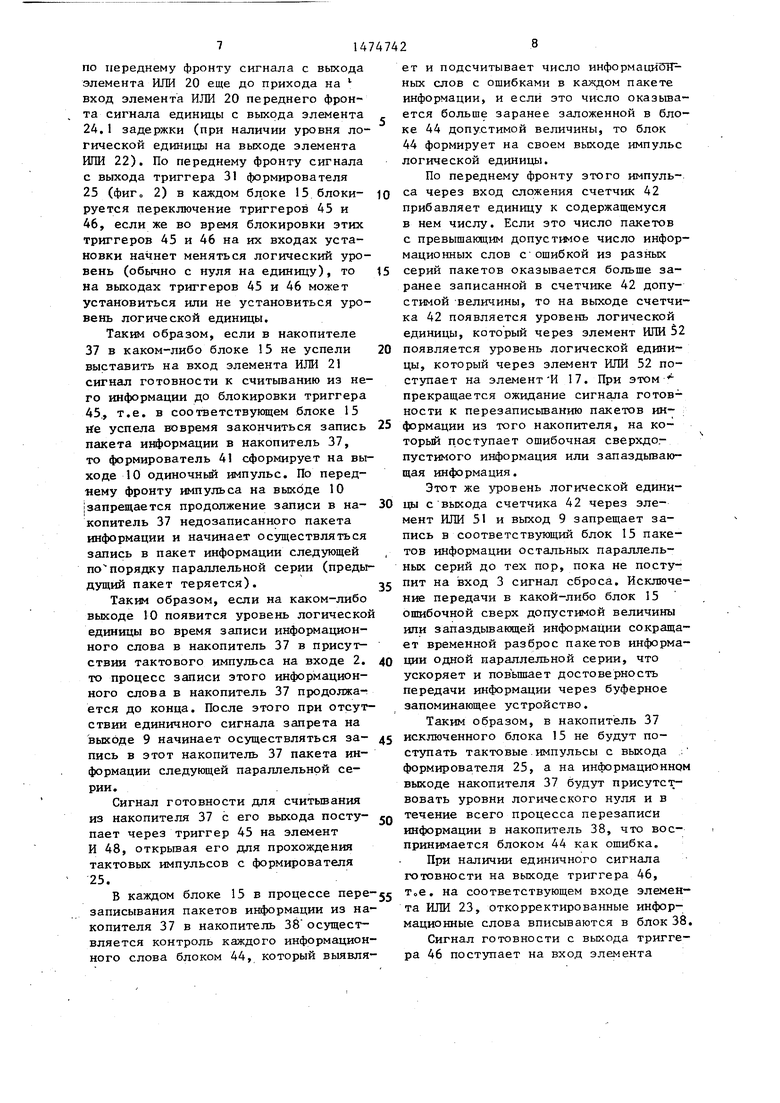

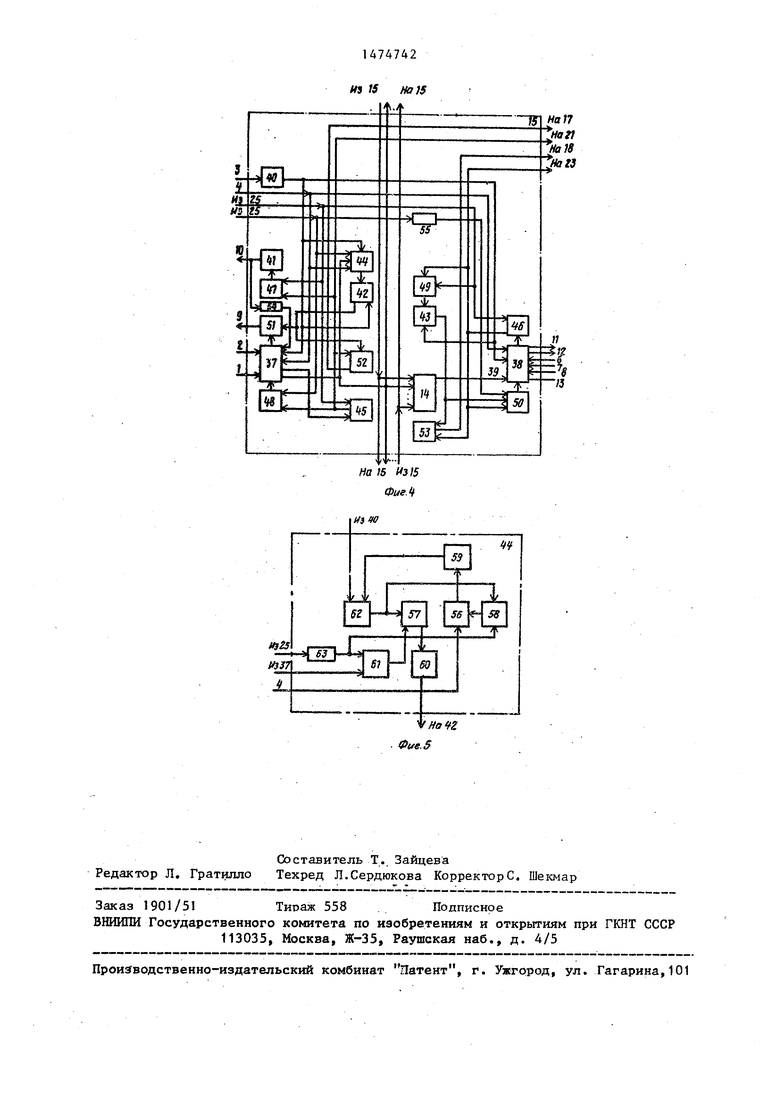

0 Блок 44 контроля (фиг. 5) каждого блока 15 может быть выполнен из блока 56 сравнения, счетчиков 57 и 58 импульсов, формирователей 59 и 60 одиночного импульса, блока 61 опреде

ления контрольных разрядов, элемента ИЛИ 62 и элемента 63 задержки.

Устройство работает следующим образом.

После включения электропитания на входы 1, 2, 5-8 (фиг. 1) подаются уровни логического нуля, на все разряды входа 4 поступают уровни логи- ческой единицы, при этом на выходе блока 26 установится уровень логического нуля. Затем на вход 3 подается одиночный импульс сброса, по переднему фронту которого блокируется элемент И 32 (фиг. 2) и устанавливается в единичное состояние триггер 31, а по заднему фронту импульса сброса открывается элемент И 32 и через элемент ИЛИ 33 сбрасываются в нуль все разряды счетчика 27.

Одновременно передним фронтом импульса сброса запускаются формирователи 40 (фиг. 4) в каждом блоке 15, которые формируют одиночные импульсы Логической единицы, по которым устанавливаются в нуль счетчики 42 и 43. После установки в исходное состояние на выходах 9-11 будет присутствовать уровень логического нуля.

После этого на вход 4 поступает параллельный двоичный код числа информационных слов в пакете информации, который присутствует на входе 4 на протяжении времени, выбранного оператором.

К входам 1 и 2 и выходам 9 и 10 каждого блока 15 подключаются соответственно выходы и входы одного процессора (на фиг. 1 не показаны), например, многопроцессорного вычисли тельного комплекса. На все входы 1 одновременно поступает параллельная серия пакетов информации с большим или меньшим разбросом по времени, в каждом пакете информации одной серии содержится одинаковое число одинаковых информационных слов, все процессоры одновременно решают одинаковую задачу.

Каждое информационное слово в любом пакете информации представлено параллельным двоичным кодом и содержит байты информации с контрольными разрядами, байты номера этого информационного слова в данном пакете информации со своими контрольными разрядами (указывающие положение этого информационного слова в последовав тельности информационных слов этого

0

0

5

5

п

0

5

5

0

5

пакета информации), байты числа информационных слов в этом пакете информации со своими контрольными разрядами и байты номера этого пакета информации со своими контрольными разрядами в последовательности пакетов информации, поступающей в буферное запоминающее устройства только из одного процессора.

Максимальное число информационных слов в пакете определяется максимальной информационной емкостью накопителя 37 или 38.

Каждому информационному слову соответствует тактовый импульс, который поступает на вход 2.

В зависимости от выбранного режима работы устройства на вход 5 поступает уровень логического нуля (режим неограниченного ожидания перезаписи) или единицы (режим ограничения ожидания) .

Затем в накопитель 37 блока 15 (фиг. 4) по каждому тактовому импульсу на входе 2 записывается соответствующее информационное слово. После записи в накопитель 37 последнего информационного слова пакета первой серии этот блок 15 выставляет на выходе 10 уровень логической единицы. Дальше в этот же накопитель 37 логичным образом вписывается пакет информации второй параллельной серии. После записи второго пакета информации блок 15 выставляет уровень логической единицы на выходе 9, запрещая запись в этот блок 15 пакета информации следующей третьей, например, параллельной серии до тех пор, пока не будет полностью считан из накопителя 37 этого блока -15 пакет информации первой параллельной серии, тогда уровень логической единицы с выхода 9 будет снят. Запись каждого пакета информации одной и той же параллельной серии в каждый блок 15 производится независимо от записи пакетов информации этой же серии в соседние с ним блоки 15.

Считывание пакетов информации первой серии из накопителя 37 всех блоков 15 производится одновременно с помощью пакета тактовых импульсов, формируемых формирователем 25. По переднему фронту каждого тактового импульса на втором выходе формирователя 25 на выходе накопителя 37 появляется параллельньй дгюичный код соответствующего считываемого информационного слова в виде постоянных уровней напряжения. С выхода накопителя 37 считанное слово поступает на одноименные входы блока 14, который осуществляет коррекцию ошибок в каждом считываемом слове (если ошибки имеются). На все входы каждого блока 14 одновременно поступают одиночные информационные слова пакетов информации одной и той же параллельной серии. В блоке 14 ошибки исправляются путем сравнения между собой одинаковых информационных слов, например корректируются ошибки в результате вычислений или потеря какого-либо разряда при передаче информационного слова в устройстве, или при достаточном числе блоков 15 полное отсутствие информационного слова на каком-либо входе блока 14с Откорректированное информационное слово с выходов блоков 14 по входу 39 записывается в блоки 38 одновременно по всем блокам 15 с помощью того же тактового импульса, с помощью которого оно было считано из накопителя 37, поступающего на тактовый вход блока 38 через элемент 55 задержки.

После перезаписи из накопителя- 37 в накопитель 38 пакета информации первой параллельной серии осуществляется аналогичным образом переписывание пакета информации второй параллельной серии Если после этого на выходе накопителя 38 будет присутствовать уровень логической единицы, то этот накопитель 38 будет принимать пакет информации следующей (третьей) параллельной серии и т.д.

К выходам 11-13 и входам 6-8 каждого блока 15 подключается, например, блок управления накопителем на магнитной ленте (МП) или магнитном диске (МД) (на фиг. 1 не показаны). Пе- резались пакетов информации по выходам 13 из устройства в каждый внешний накопитель на МП или МД производится самостоятельно из одноименного блока 15 независимо от состояния других блоков 15. Считывание пакета информации из каждого блока 15 осуществляется при наличии уровня логической единицы на выходе 11. В этом случае на вход 6 поступает сигнал логической единицы, по переднему фронту которого из этого блока 15 начинают через выход 13 поступать информационные

5

0

5

0

5

0

5

0

5

слова считываемого пакета информации, каждое из которых сопровождается тактовым импульсом на одноименном такто- .вом выходе 12. После окончания считывания каждого пакета информации из устройства уровень логической единицы на входе 6 снимается. Если после считывания любого пакета информации на выходе 11 продолжает оставаться уровень логической единицы, то для считывания следующего пакета информации из соответствующего блока 15 на вход 6 опять поступает уровень логической единицы, который присутствует на входе 6 на протяжении всего процесса считывания пакета информации из блока 15 „

С второго индикаторного выхода накопителя 37 (фиг. 4) уровень логической единицы, т.е. сигнал готовности накопителя 37 к считыванию, через триггер 45 поступает на вход элемента ИЛИ 21 (фиг. 1), а через элемент ИЛИ 52 - на вход элемента И 17. С выхода элемента ИЛИ 21 уровень логической единицы, поступивший с выхода блока 15, первым выставившего сигнал единицы на вход элемента ИЛИ 21 через блок 24.1 и элемент ИЛИ 20, поступает на формирователь 25.

Время задержки элемента 24.1 плюс время задержек в триггере 45, накопителе 37, элементах ИЛИ 21 и 20, элементе И 32 (фиг. 2), формирователе 29, триггерах 31 и 45 определяет максимально допустимое время рассогласования окончания записи пакета информации одной параллельной серии относительно блока 15, первым закончившего запись пакета информации этой параллельной серии. Это допустимое время рассогласования может регулироваться подбором числа элементов 36 задержек (фиг. 3), которое выбирается оптимальным исходя из допустимой скорости передачи информации через устройство.

Если на всех входах элемента И 17 появились передние фронты сигналов логической единицы со всех блоков 15 с разбросом в заранее заданном допустимом пределе, то передний фронт сигнала логической единицы с выхода элемента И 17 может поступить на элемент ИЛИ 20 раньше, чем передний фронт сигнала логической единицы с выхода элемента 24.1 задержки. В этом случае формирователь 25 запускается

по переднему фронту сигнала с выхода элемента ИЛИ 20 еще до прихода на v вход элемента ИЛИ 20 переднего фронта сигнала единицы с выхода элемента 24.1 задержки (при наличии уровня логической единицы на выходе элемента ИЛИ 22). По переднему фронту сигнала с выхода триггера 31 формирователя 25 (фиго 2) в каждом блоке 15 блокируется переключение триггеров 45 и 46, если же во время блокировки этих триггеров 45 и 46 на их входах установки начнет меняться логический уровень (обычно с нуля на единицу), то на выходах триггеров 45 и 46 может установиться или не установиться уровень логической единицы.

Таким образом, если в накопителе 37 в каком-либо блоке 15 не успели выставить на вход элемента ИЛИ 21 сигнал готовности к считыванию из него информации до блокировки триггера 45, т.е. в соответствующем блоке 15 йе успела вовремя закончиться запись пакета информации в накопитель 37, то формирователь 41 сформирует на выходе 10 одиночный импульс. По переднему фронту импульса на выходе 10 Iзапрещавтся продолжение записи в накопитель 37 недозаписанного пакета информации и начинает осуществляться запись в пакет информации следующей по порядку параллельной серии (предыдущий пакет теряется).

Таким образом, если на каком-либо выходе 10 появится уровень логическо единицы во время записи информационного слова в накопитель 37 в присутствии тактового импульса на входе 2. то процесс записи этого информационного слова в накопитель 37 продолжается до конца. После этого при отсутствии единичного сигнала запрета на выходе 9 начинает осуществляться запись в этот накопитель 37 пакета информации следующей параллельной серии.

Сигнал готовности для считывания из накопителя 37 с его выхода поступает через триггер 45 на элемент И 48, открывая его для прохождения тактовых импульсов с формирователя 25.

В каждом блоке 15 в процессе пере-55 т.е. на соответствующем входе элемензаписывания пакетов информации из накопителя 37 в накопитель 38 осуществляется контроль каждого информационного слова блоком 44, который выявлята ИЛИ 23, откорректированные информационные слова вписываются в блок 38. Сигнал готовности с выхода триггера 46 поступает на вход элемента

0

5

0

ет и подсчитывает число информациоТП- ных слов с ошибками в каждом пакете информации, и если это число оказывается больше заранее заложенной в блоке 44 допустимой величины, то блок 44 формирует на своем выходе импульс логической единицы.

По переднему фронту этого импульса через вход сложения счетчик 42 прибавляет единицу к содержащемуся в нем числу. Если это число пакетов с превышающим допустимое число информационных слов с ошибкой из разных серий пакетов оказывается больше заранее записанной в счетчике 42 допустимой величины, то на выходе счетчика 42 появляется уровень логической единицы, который через элемент ИЛИ 52 появляется уровень логической единицы, который через элемент ИЛИ 52 поступает на элемент И 17. При этом прекращается ожидание сигнала готовности к перезаписыванию пакетов ин5 формации из того накопителя, на который поступает ошибочная сверхдопустимого информация или запаздывающая информация.

Этот же уровень логической едини-

0 цы с выхода счетчика 42 через элемент ИЛИ 51 и выход 9 запрещает запись в соответствующий блок 15 паке- , тов информации остальных параллельных серий до тех пор, пока не посту5 пит на вход 3 сигнал сброса. Исключение передачи в какой-либо блок 15 ошибочной сверх допустимой величины или запаздывающей информации сокращает временной разброс пакетов информации одной параллельной серии, что ускоряет и повышает достоверность передачи информации через буферное запоминающее устройство.

Таким образом, в накопитель 37 исключенного блока 15 не будут поступать тактовые импульсы с выхода формирователя 25, а на информационном выходе накопителя 37 будут присутствовать уровни логического нуля и в течение всего процесса перезаписи информации в накопитель 38, что воспринимается блоком 44 как ошибка. При наличии единичного сигнала готовности на выходе триггера 46,

0

5

0

т.е. на соответствующем входе элемента ИЛИ 23, откорректированные информационные слова вписываются в блок 38. Сигнал готовности с выхода триггера 46 поступает на вход элемента

10

91474742

ИЛИ 23..В режиме ограничения ожидания (на входе 5 - сигнал единицы) передний фронт сигнала готовности опережающего блока 15 с выхода элемента ИЛИ 23 через элемент И 19, блок 24.2 и элемент ИЛИ 22 поступает на вход формирователя 25, который по переднему фронту этого сигнала готовности при наличии логической единицы на входе 5 и выходе элемента ИЛИ 22 через определенное время задержки выставляет сигнал блокировки (уровень единицы) и затем фо/рмирует тактовые импульсы.

Сигнал готовности опережающего блока 15 поступает также на соответствующий вход элемента И 18. Если передний фронт сигнала единицы с выхода элемента И 18 придет раньше на элемент ИЛИ 22, чем передний фронт сигнала единицы с выхода блока 24.2, то формирователь 25 начнет формировать пакет тактовых импульсов (при наличии сигнала единицы на выходе .. элемента ИЛИ 20). То есть временное рассогласование сигналов готовностей от накопителя 38 всех блоков 15 относительно опережающего блока 15 оказывается внутри допустимого предела, который определяется временем задержки блока 24.2. Этот допустимый предел времени рассогласования можно регулировать подбором числа элементов 36

10

Счетчик 43 фиксирует запаздывание готовности для записи информации в накопитель 38. Если число таких запаздываний окажется больше заранее заложенной в счетчике 43 величины, то блок 15 из дальнейшей совместной работы исключается. Возможно повторное считывание из накопителя 38 всего записанного в него пакета на случай полной потери его во внешнем накопителе на МП или МД. Для повторного считывания пакета информации на вход 8 поступает одиночный импульс

15 (в промежутке между тактовыми импульсами).

Один и тот же пакет информационных слов может быть считан из накопителя 38 несколько раз, пока на вхо20 де 6 присутствует сигнал единицы. Для считывания повторно одного информационного слова из накопителя 38 на вход 7 подается сигнал единицы.

25 Формула и зобре тения

памяти, входы сброса которых и вход сброса блока управления объединены и .являются входом блока устройства, вы- 4Q ходы окончания записи блоков памяти являются выходами окончания записи устройства, причем вторые тактовые входы блоков оперативной памяти соединены с первым выходом блока управля с выхода триггера 46, и запоздав- 5 ления второй выход которого подклю- ший пакет информации этой серии бу- чен к первым установочным входам бло- дет потерян. ков оперативной памяти, первые управляющие выходы которых соединены с входами запуска первой группы блока 50 управления, входы задержки запуска первой группы которого подключены к вторым управляющим выходам блоков оперативной памяти, отличающееся тем, что,, с целью расши- cg рения области применения устройства за счет обеспечения одновременной параллельной передачи нескольких идентичных информационных слов с коррекцией ошибок в него введены блоки корЕсли выключен режим ограничения ожидания (на входе 5 - уровень логического нуля), то элемент J4 19 будет закрыт и на элемент ИЛИ 22 сможет поступить сигнал единицы с выхода элемента И 18. В этом случае переписывание пакетов информации одной серии в накопитель 38 всех блоков 15 начнется только тогда, когда из всех блоков 15 на все входы элемента И 18 поступят уровни единицы.

2

10

Счетчик 43 фиксирует запаздывание готовности для записи информации в накопитель 38. Если число таких запаздываний окажется больше заранее заложенной в счетчике 43 величины, то блок 15 из дальнейшей совместной работы исключается. Возможно повторное считывание из накопителя 38 всего записанного в него пакета на случай полной потери его во внешнем накопителе на МП или МД. Для повторного считывания пакета информации на вход 8 поступает одиночный импульс

(в промежутке между тактовыми импуль сами).

Один и тот же пакет информационных слов может быть считан из накопителя 38 несколько раз, пока на входе 6 присутствует сигнал единицы. Для считывания повторно одного информационного слова из накопителя 38 на вход 7 подается сигнал единицы.

Формула и зобре тения

памяти, входы сброса которых и вход сброса блока управления объединены и являются входом блока устройства, вы- ходы окончания записи блоков памяти являются выходами окончания записи устройства, причем вторые тактовые входы блоков оперативной памяти соединены с первым выходом блока управ

Ei

за

L-P

На 15 На 15 Фие.2

1«з25

И) 2)

ФиеЗ

Н9 IS

tU3f -

Haft

На 18 Hal3

На IS Из IS ФиеЦ

VHatZ Фие.5

| Буферное запоминающее устройство | 1981 |

|

SU995123A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1238160A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-04-23—Публикация

1987-02-23—Подача