соединены с группой информационных входов регистра хранения исправной микрокоманды, первый выход которого соединен с вторым входом блока элементов И, группа выходов которого является группой выходов устройства, второй выход регистра хранения исправной микрокоманды подключен к второму входу третьего элемента И, выход которого подключен к входу останова блока пуска-останова, третий и четвертьцЧ выходы которого соединены с входами считывания второго и первого блоков памяти соответственно,третий выход регистра хранения исправной микрокоманды подключен к третьим группам инфорг адионных входов первого и второго регистров адреса соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1309024A1 |

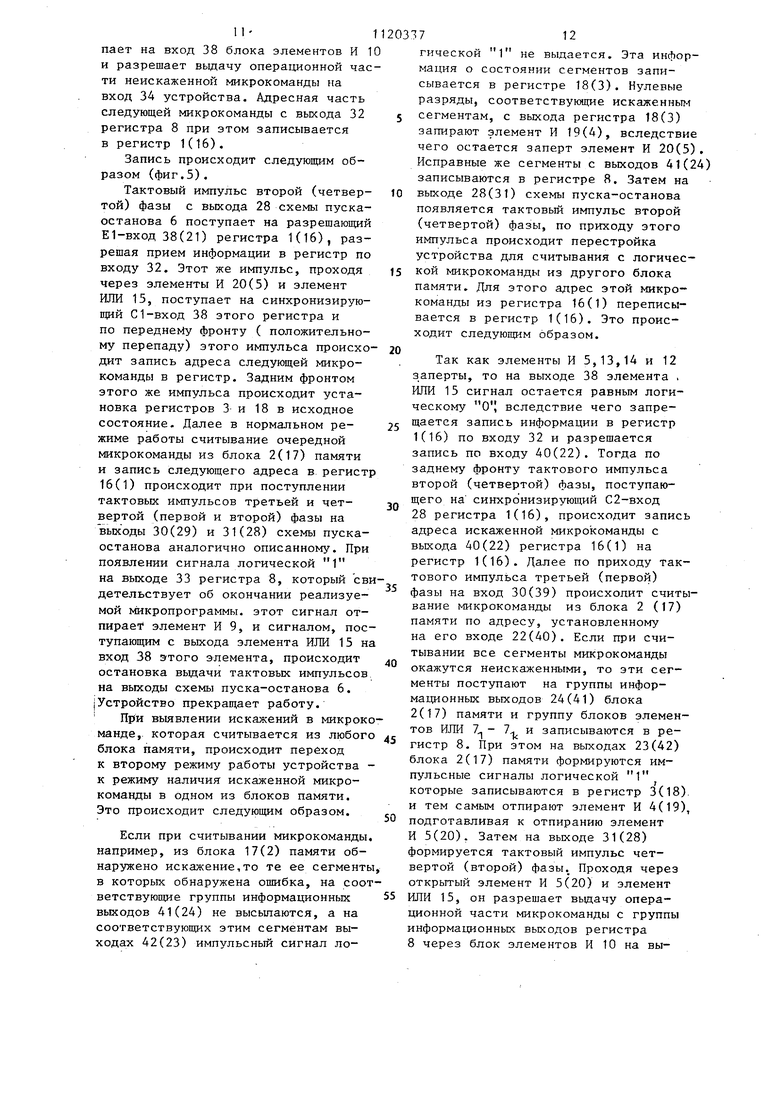

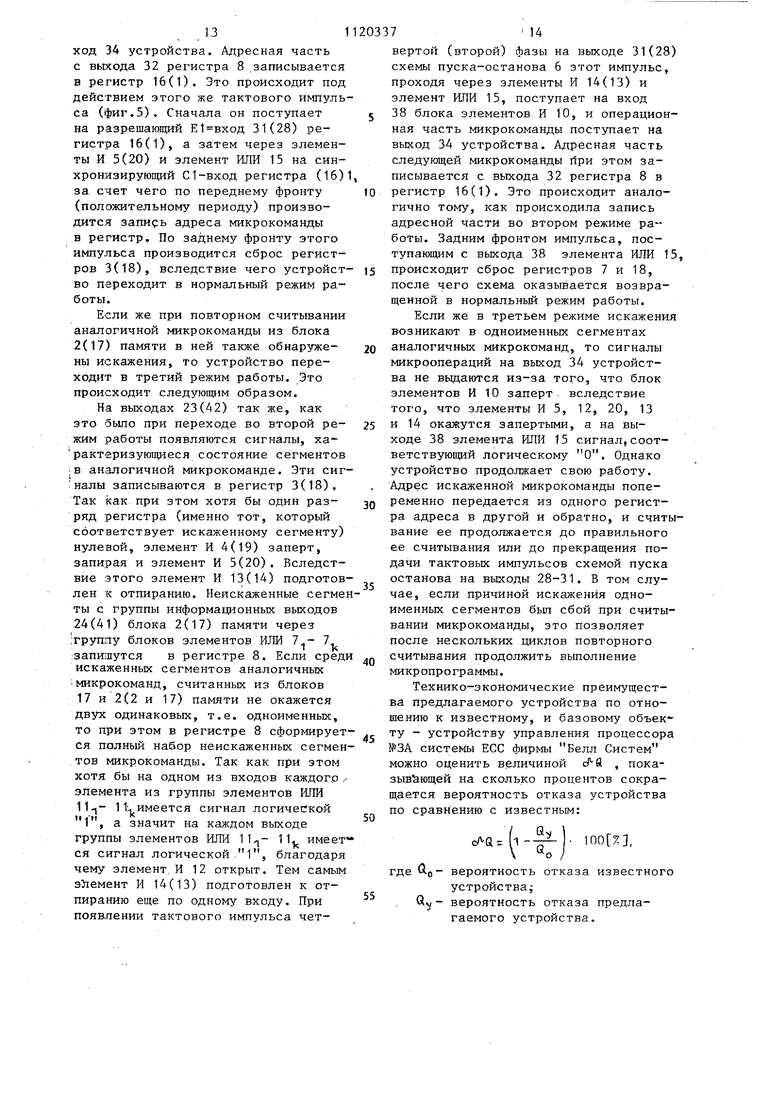

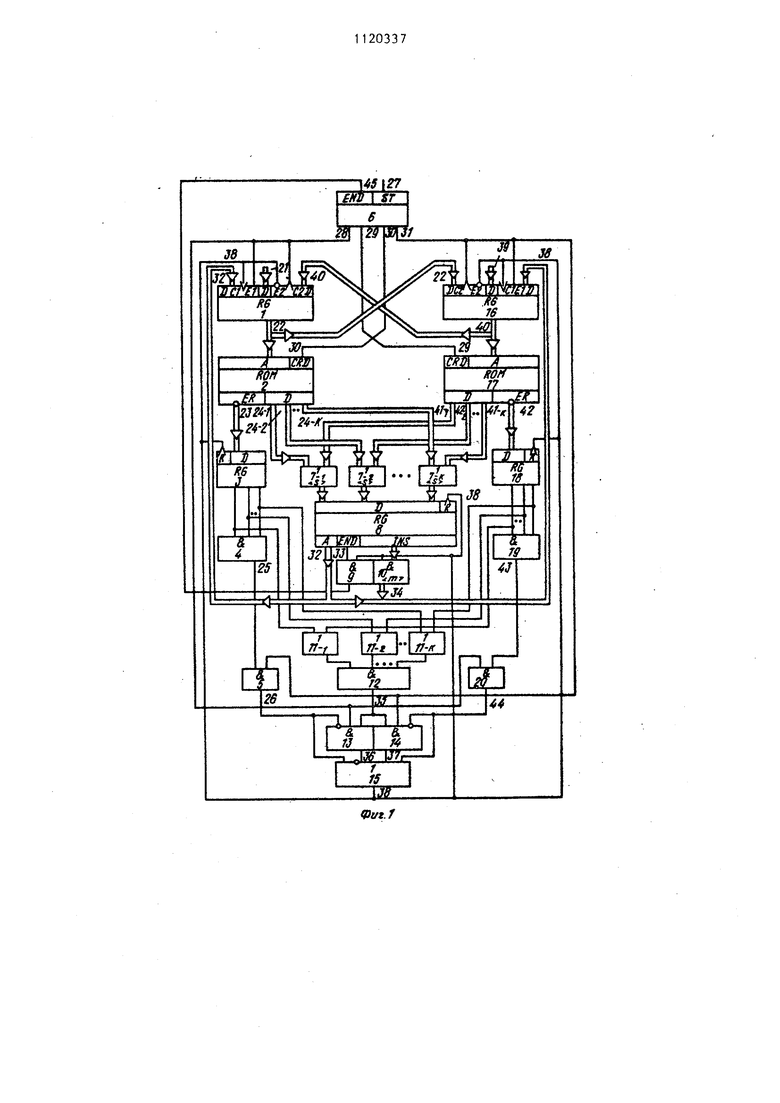

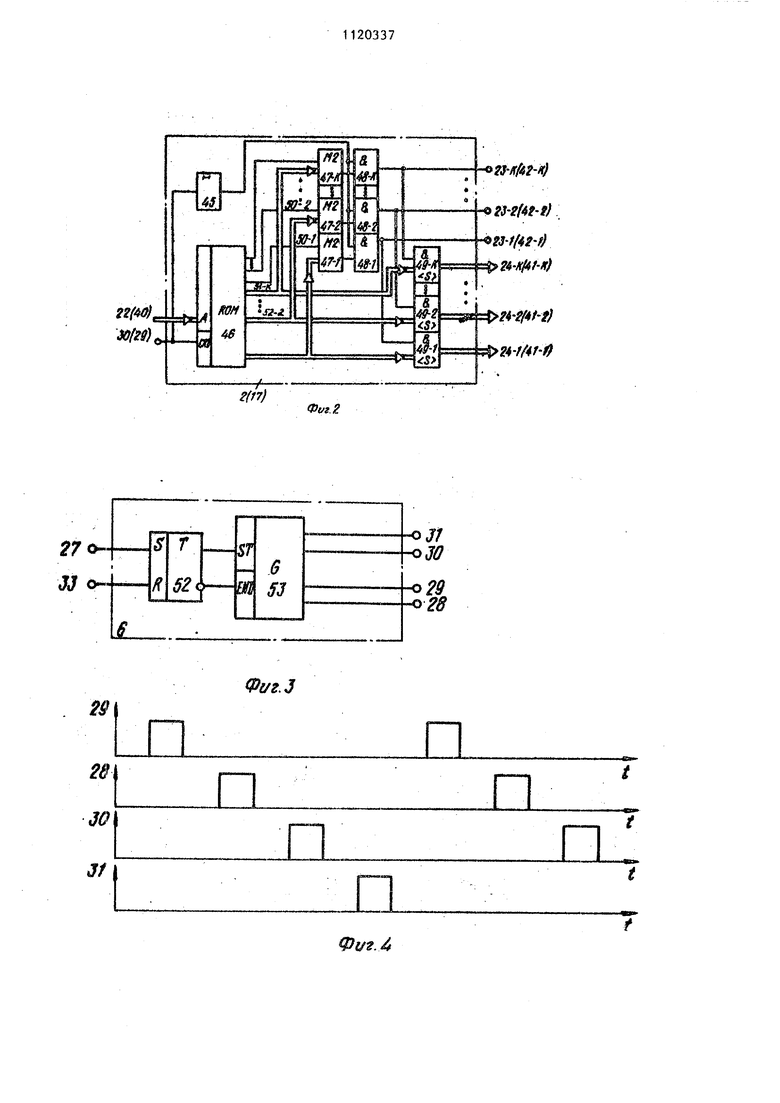

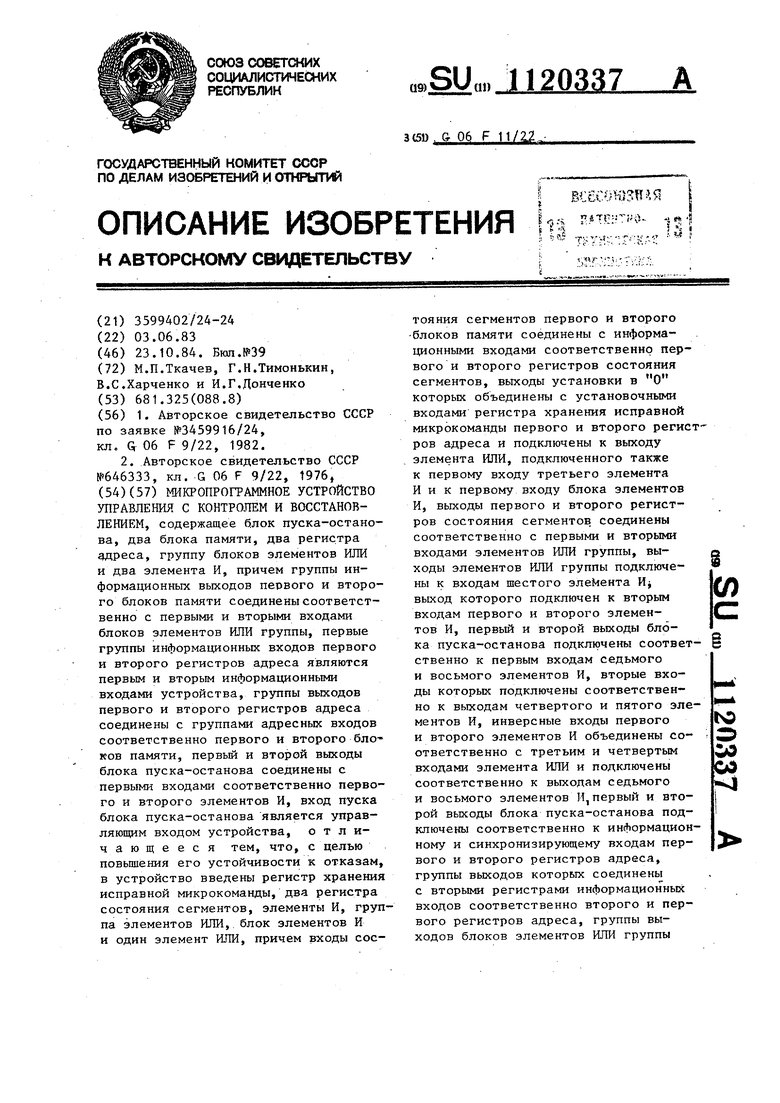

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ И ВОССТАНОВЛЕНИЕМ, содержащее блок пуска-останова, два блока памяти, два регистра адреса, группу блоков элементов ИЛИ и два элемента И, причем группы информационных выходов первого и второго блоков памяти соединены соответственно с первыми и вторыми входами блоков элементов ИЛИ группы, первые группы информационных входов первого и второго регистров адреса являются первым и вторым информационными входами устройства, группы выходов первого и второго регистров адреса соединены с группами адресных входов соответственно первого и второго блоков памяти, первьй и второй выходы блока пуска-останова соединены с первыми входами соответственно первого и второго элементов И, вход пуска блока пуска-останова является управляющим входом устройства, отличающееся тем, что, с целью повьшения его устойчивости к отказам, в устройство введены регистр хранения исправной микрокоманды, два регистра состояния сегментов, элементы И, группа элементов ИЛИ, блок элементов И и один элемент ИЛИ, причем входы состояния сегментов первого и второго блоков памяти соединены с информационными входами соответственно первого и второго регистров состояния сегментов, выходы установки в О которых объединены с установочными входами регистра хранения исправной микрокоманды первого и второго регистров адреса и подключены к выходу элемента ИЛИ, подключенного также к первому входу третьего элемента И и к первому входу блока элементов И, выходы первого и второго регистров состояния сегментов соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы элементов ИЛИ группы подключены к входам шестого элемента И (Л выход которого подключен к вторым входам первого и второго элементов И, первый и второй выходы блока пуска-останова подключены соответственно к первым входам седьмого и восьмого элементов И, вторые входы которых подключены соответственно к выходам четвертого и пятого элеto ментов И, инверсные входы первого и второго элементов И объединены соZfd Од ответственно с третьим и четвертым входами элемента ИЛИ и подключены соответственно к выходам седьмого и восьмого элементов И,первый и второй выходы блока пуска-останова подключены соответственно к информационному и синхронизирующему входам первого и второго регистров адреса, группы выходов которых соединены с вторыми регистрами информационных входов соответственно второго и первого регистров адреса, группы выходов блоков элементов ИЛИ группы

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ с повьшенной надежностью.

Известно микропрограммное устройс во управления, содержащее два блока памяти, два регистра адреса, два коммутатора, две группы элементов , шесть триггеров, четыре элемента И и группу элементов ИЛИ

Недостатком данного устройства является большая структурная избыто :ность, требуемая для обеспечения; заданного уровня устойчивости к отказам.

Наиболее близким к предлагаемому устройству по технической сущности и достигаемому эффекту является перестраиваемое микропрограммное устройство управления, которое содержит два блока памяти, два регистра адреса, два коммутатора, два триггера, два элемента И и группу блоков элементов ИЛИ, причем первый и вто-. рой входы синхронизации устройства соответственно через первый и второй элементы И соединены с входами считывания соответственно первого и второго блоков памяти, группы адресных входов которых соединены с группами информационных выходов соответственно первого и второго регистра адреса, выходы поля микроопераций первого и второго блоков памяти соединены соответственно с первыми и вторыми входами группы блоков элементов ШШ, выходы которых являются группой выходов устройства, выходы поля адреса первого и второго блоков памяти соединены с первыми группами информа1шонных входов соответственно второго и первого регистров адреса

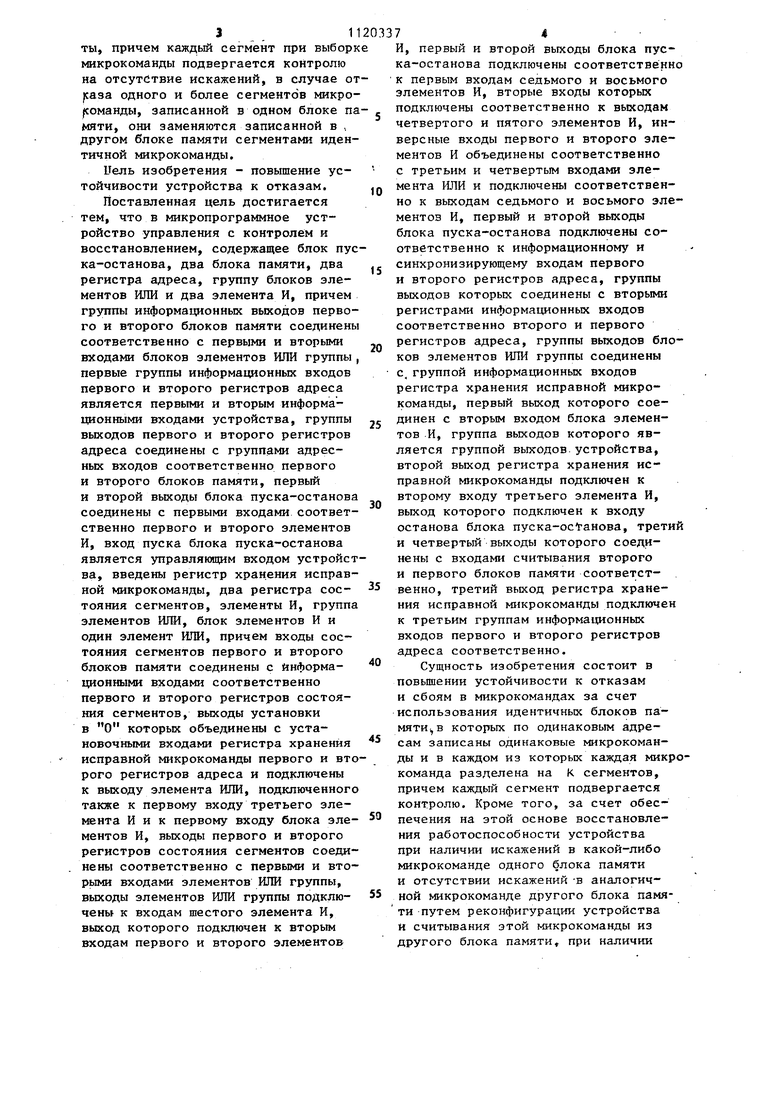

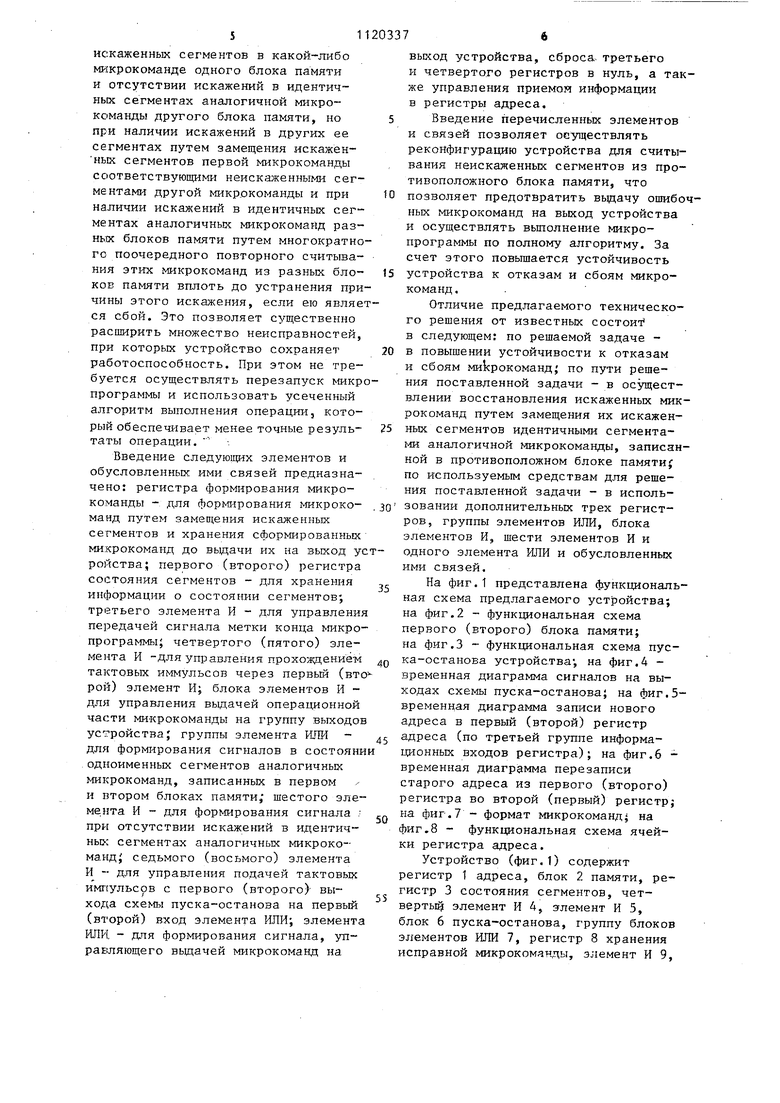

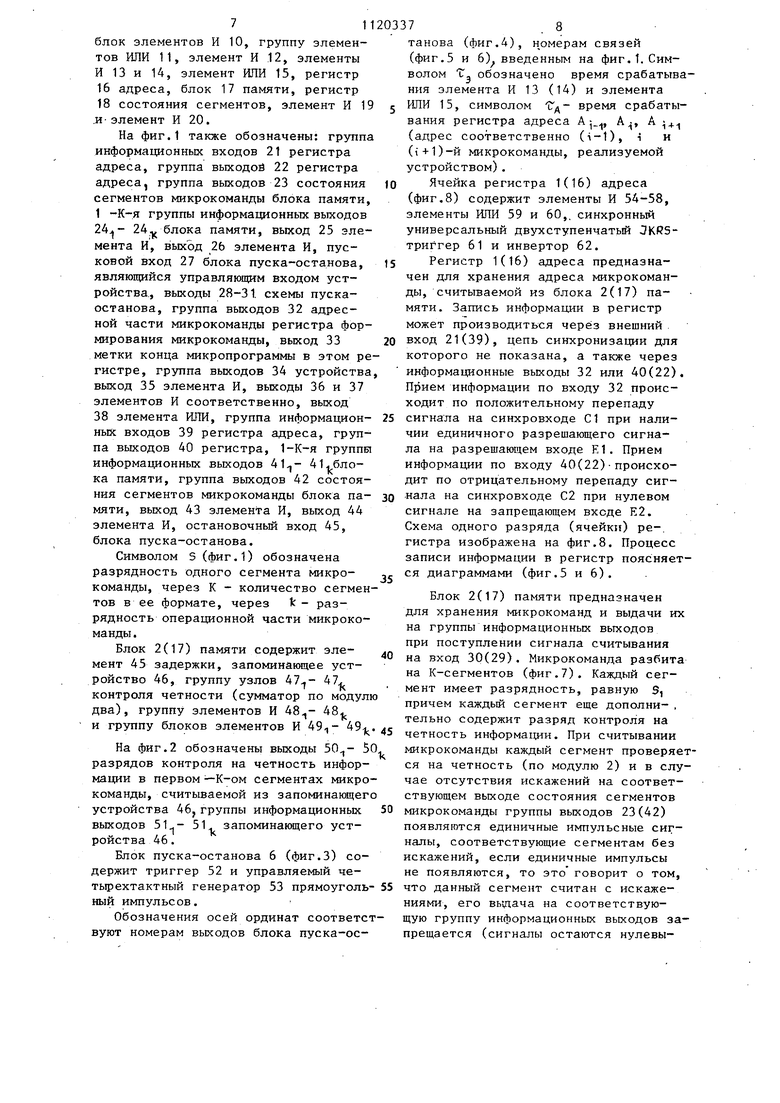

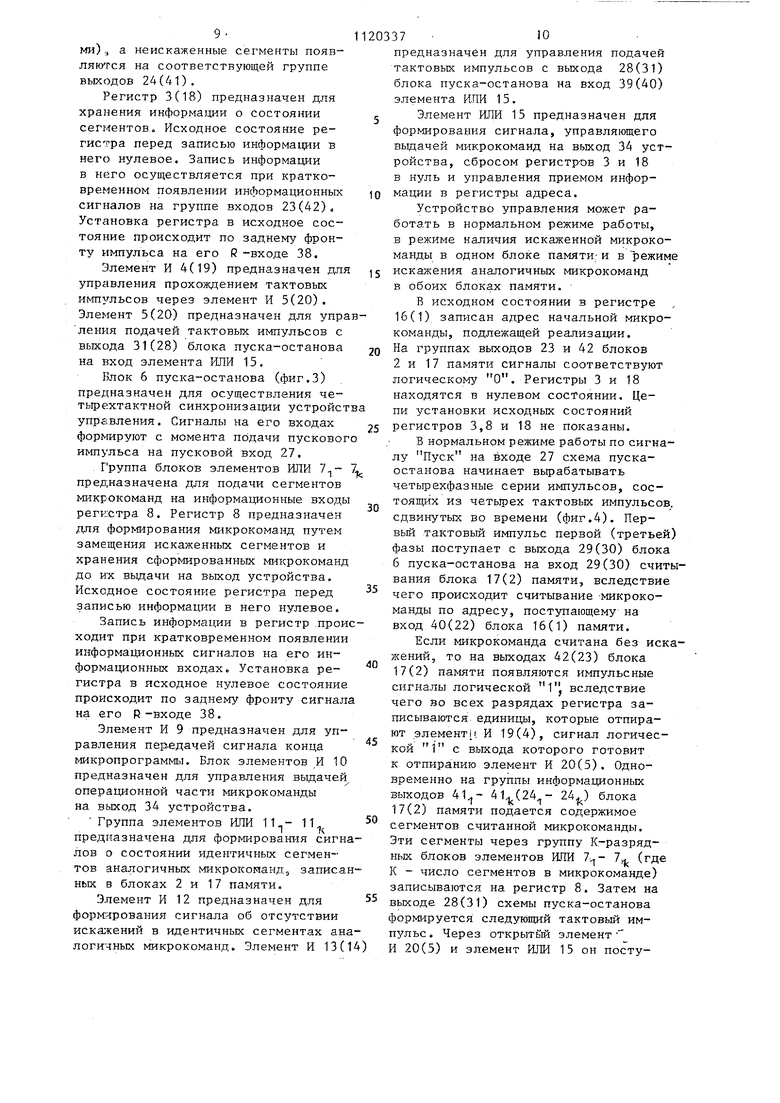

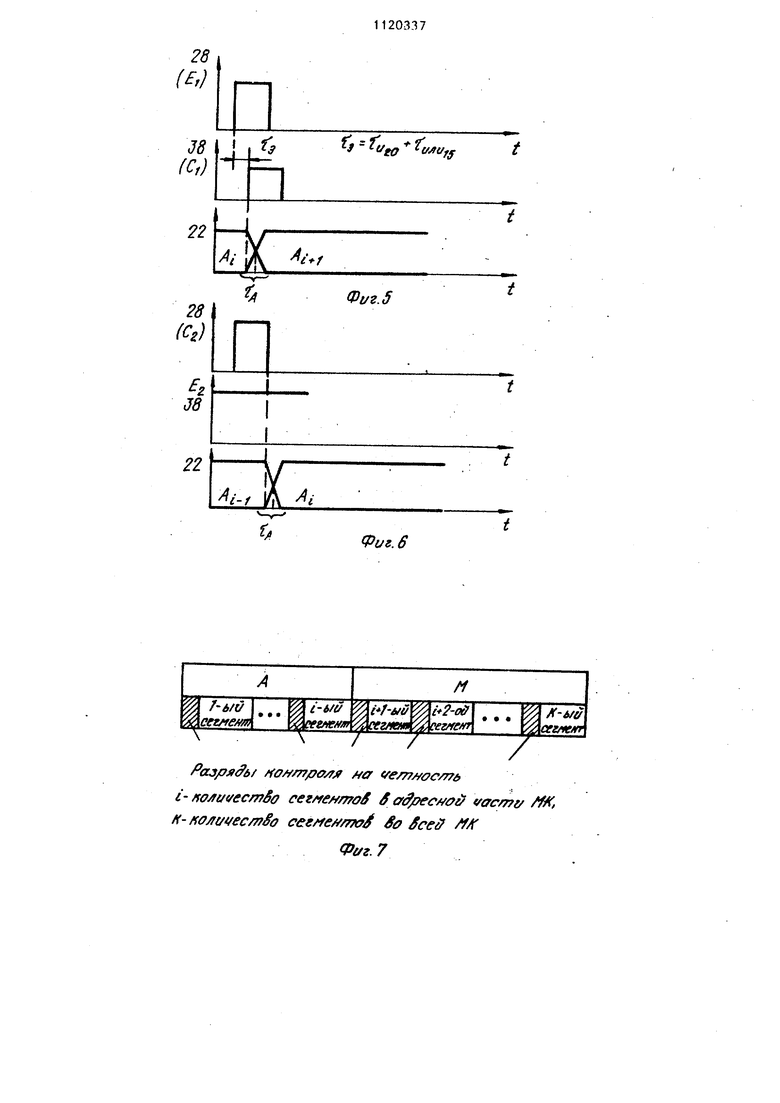

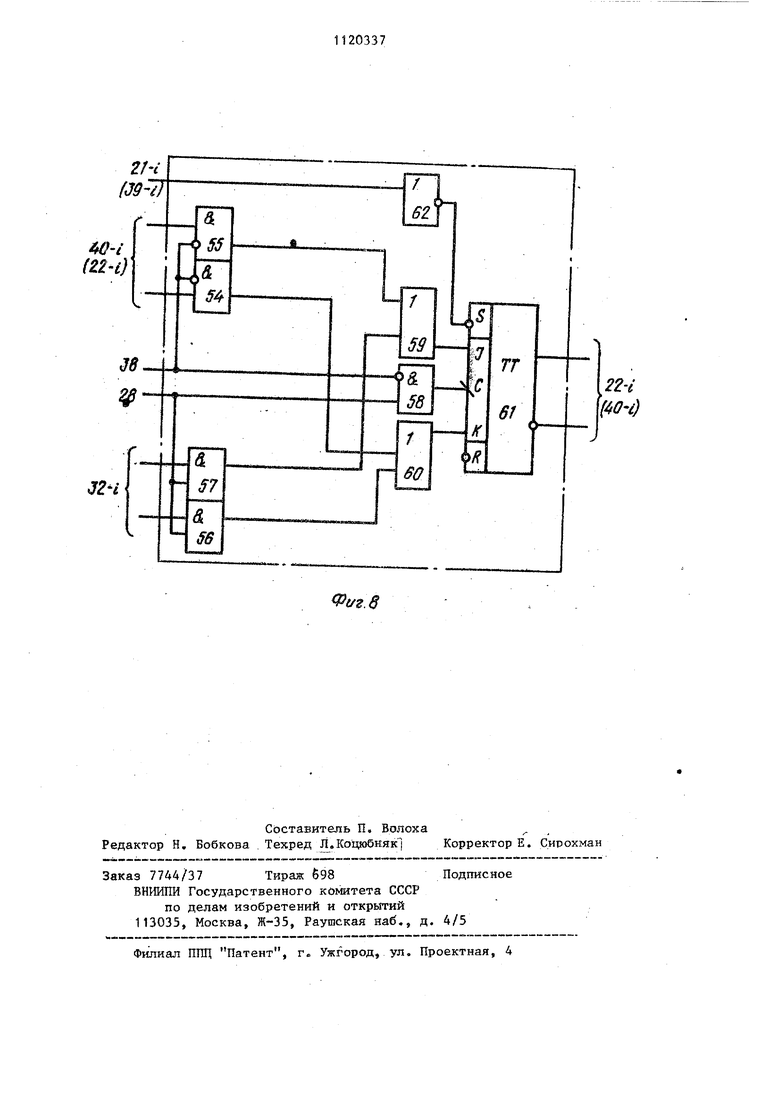

через первый и второй коммутаторы соответственно, выход неисправности первого и второго блоков памяти соединен с второй группой информап юнных входов соответственно второго и первого регистров адреса и со счетным входом соответственно первого и второго триггеров, единичные выходы которьк соединены с вторыми входами соответственно второго и первого элементов И, а нулевые выходы с управляющим входом соответственно первого и второго коммутаторов, входы синхронизации которых соединены соответственно с вторым и первым входами синхронизации устройства 2. Недостатком известного устройства является низкая устойчивость к отказам, вызванная тем, что при отказе какой-либо микрокоманды в одном блоке памяти устройство не может продолжить выполнение микропрограммы, а должно прекратить ее реализацию и перейти к другой микропрограмме, которая записана полностью в противоположном блоке памяти и задает усеченный алгоритм вьшолнения операции. Неисправный блок памяти при этом отключается. Если же отказ микрокоманды произойдет и в другом блоке памяти, то этот блок также будет отключен, и устройство вообще прекратит функционирование. В то же время в устройстве может быть обеспечена возможность продолжения функционирования, причем даже не по усеченному алгоритму и без перезапуска выполнения микропрограммы. Эта возможность может быть реализована путем использования в устройстве идентичных блоков памяти, в которых каждая микрокоманда разбита на сегменты, причем каждый сегмент при выбор микрокоманды подвергается контролю на отсутствие искажений, в случае о |саза одного и более сегментбв микро соманды, записанной в одном блоке п мяти, они заменяются записанной в другом блоке памяти сегментами иден тичной микрокоманды. иель изобретения - повышение устойчивости устройства к отказам. Поставленная цель достигается тем, что в микропрограммное устройство управления с контролем и восстановлением, содержащее блок пус ка-останова, два блока памяти, два регистра адреса, группу блоков элементов ШШ и два элемента И, причем группы информационных выходов первого и второго блоков памяти соединены соответственно с первыми и вторыми входами блоков элементов ИЛИ группы первые группы информационных входов первого и второго регистров адреса является первыми и вторым информа1ЩОННЫМИ входами устройства, группы вькодов первого и второго регистров адреса соединены с группами адресных входов соответственно первого и второго блоков памяти, первый и второй выходы блока пуска-останова соединены с первыми входами соответственно первого и второго элементов И, вход пуска блока пуска-останова является управляющим входом устройст ва, введены регистр хранения исправной микрокоманды, два регистра соетояния сегментов, элементы И, группа элементов ИЛИ, блок элементов И и один элемент ИЛИ, причем входы состояния сегментов первого и второго блоков памяти соединены с йнформационными входами соответственно первого и второго регистров состояния сегментов, выходы установки в О которых объединены с установочными входами регистра хранения исправной микрокоманды первого и вто рого регистров адреса и подключены к выходу элемента ИЛИ, подключенного также к первому входу третьего элемента И и к первому входу блока элементов И, выходы первого и второго регистров состояния сегментов соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы элементов ШШ группы подключены к входам шестого элемента И, выход которого подключен к вторым входам первого и второго элементов И, первый и второй выходы блока пуска-останова подключены соответственно к первым входам седьмого и восьмого элементов И, вторые входы которых подключены соответственно к выходам четвертого и пятого элементов И, инверсные входы первого и второго элементов И объединены соответственно с третьим и четвертым входами элемента ИЛИ и подключены соответственно к выходам седьмого и восьмого элементов И, первый и второй выходы блока пуска-останова подключены соответственно к информационному и синхронизирующему входам первого и второго регистров адреса, группы выходов которых соединены с вторыми регистрами информационных входов соответственно второго и первого регистров адреса, группы выходов блоков элементов ИЛИ группы соединены с, группой информационных входов регистра хранения исправной микрокоманды, первый выход которого соединен с вторым входом блока элементов И, группа выходов которого является группой выходов, устройства, второй выход регистра хранения исправной микрокоманды подключен к второму входу третьего элемента И, выход которого подключен к входу останова блока пуска-осТанова, третий и четвертый выходы которого соединены с входами считывания второго и первого блоков памяти соответственно, третий выход регистра хранения исправной микрокоманды подключен к третьим группам информационных входов первого и второго регистров адреса соответственно. Сущность изобретения состоит в повьппении устойчивости к отказам и сбоям в микрокомандах за счет использования идентичных блоков памяти1,в которьк по одинаковым адресам записаны одинаковые микрокоманды и в каждом из которых каждая микрокоманда разделена на К сегментов, причем каждый сегмент подвергается контролю. Кроме того, за счет обеспечения на этой основе восстановления работоспособности устройства при наличии искажений в какой-либо микрокоманде одного блока памяти и отсутствии искажений -в аналогичной микрокоманде другого блока памяти путем реконфигурации устройства и считывания этой микрокоманды из другого блока памяти, при наличии искаженных сегментов в какой-либо микрокоманде одного блока памяти и отсутствии искажений в идентичных сегментах аналогичной микрокоманды другого блока памяти, но прИ наличии искажений в других ее сегментах путем замещения искаженных сегментов первой микрокоманды соответствующими неискаженными сегментами другой микрокоманды и при наличии искажений в идентичных сегментах аналогичных микрокоманд разнь:сх блоков памяти путем многократно го поочередного повторного считывания этих микрокоманд из разных блоков памяти вплоть до устранения при ся сбой. Это позволяет существенно расширить множество неисправностей, при которых устройство сохраняет работоспособность. При этом не требуется осуществлять перезапуск микр программы и использовать усеченный алгоритм выполнения операции, который обеспечивает менее точные результаты операции, Введение следующих элементов и обусловленных ими связей предназначено: регистра формирования микрокоманды - для форм1 рования микрокоманд путем замещения искаженных сегментов и хранения сформированных микрокоманд до выдачи их на выход у ройства; первого (второго) регистра состояния сегментов - для хранения информации о состоянии сегментов; третьего элемента И - для управлени передачей сигнала метки конца микро программы; четвертого (пятого) элемента И ДЛЯ управления прохождение-м тактовых иммульсов через первый (вт рой) элемент И; блока элементов И для управления выдачей операционной части микрокоманды на группу выходо устройства; группы элемента ИЛИ - для формирования сигналов в состоян .одноименных сегментов аналогичных микрокоманд, записанных в первом и втором блоках памяти, шестого эле мента И - для формирования сигнала при отсутствии искажений в идентичны : сегментах аналогичных микрокоманд j седьмого (восьмого) элемента И - для управления подачей тактовых импульсов с первого (второго)- выхода схемы пуска-останова на первый (второй) вход элемента ИЛИ; элемент ИЛИ - для формирования сигнала, упраЕ1ЛЯющего вьщачей микрокоманд на 1 6 выход устройства, сброса третьего и четвертого регистров в нуль, а также управления приемои информации в регистры адреса. Введение перечисленных элементов и связей позволяет осуществлять реконфигурацию устройства для считывания неискаженных сегментов из противоположного блока памяти, что позволяет предотвратить вьщачу ошибочных микрокоманд на выход устройства и осуществлять вьшолнение микропрограммы по полному алгоритму. За счет этого повышается устойчивость устройства к отказам и сбоям микрокоманд . Отличие предлагаемого технического решения от известных состои в следующем: по решаемой задаче в повышении устойчивости к отказам и сбоям миkpoкoмaнд; по пути решения поставленной задачи - в осуществлении восстановления искаженных микрокоманд путем замещения их искаженных сегментов идентичными сегментами аналогичной микрокоманды, записанной в противоположном блоке памяти по используемым средствам для решения поставленной задачи - в использовании дополнительных трех регистров, группы элементов ИЛИ, блока элементов И, шести элементов И и одного элемента РШИ и обусловленных ими связей. На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема первого (второго) блока памяти; на фиг.З - функциональная схема пуска-останова устройства; на фиг.4 временная диаграмма сигналов на выходах схемы пуска-останова; на фиг.5временная диаграмма записи нового адреса в первый (второй) регистр адреса (по третьей группе информационных входов регистра); на фиг,6 временная диаграмма перезаписи старого адреса из первого (второго) регистра во второй (первый) регистр; на фиг.7 - формат микрокоманду на фиг„8 - функциональная схема ячейки регистра адреса. Устройство (фиг.О содержит регистр 1 адреса, блок 2 памяти, регистр 3 состояния сегментов, четвертыЕ элемент И 4, элемент И 5, блок 6 пуска-останова, группу блоков элементов ИЛИ 7, регистр 8 хранения исправной микрокоманды, элемент И 9, блок элементов И 10, группу элементов ИЛИ 11, элемент И 12, элементы И 13 и 14, элемент ИЛИ 15, регистр 16 адреса, блок 17 памяти, регистр 18 состояния сегментов, элемент И 19 .и- элемент И 20. На фиг.1 также обозначены: группа информационных входов 21 регистра адреса, группа выходой 22 регистра адреса, группа выходов 23 состояния сегментов микрокоманды блока памяти, 1 -К-я группы информационных выходов 24 блока памяти, выход 25 элемента И, выход 26 элемента И, пусковой вход 27 блока пуска-останова, являющийся управляющим входом устройства., выходы 28-31. схемы пускаостанова, группа выходов 32 адресной части микрокоманды регистра формирования микрокоманды, выход 33 метки конца микропрограммы в этом ре гистре, группа выходов 34 устройства выход 35 элемента И, выходы 36 и 37 элементов И соответственно, выход 38 элемента ИЛИ, группа информационных входов 39 регистра адреса, группа выходов 40 регистра, 1-К-я группш информационных выходов 41-,- 4 Ь блока памяти, группа выходов 42 состояния сегментов микрокоманды блока памяти, выход 43 элемента И, выход 44 элемента И, остановочный вход 45, блока пуска-останова. Символом S (фиг.1) обозначена разрядность одного сегмента микрокоманды, через К - количество сегмен тов в ее формате, через 1 - разрядность операционной части микрокоманды . Блок 2(17) памяти содержит элемент 45 задержки, запоминающее устройство 46, группу узлов . контроля четности (сумматор по модул два), группу элементов И 48.,- 48| и группу блоков элементов И 49,- 49|, На фиг.2 обозначены выходы 5 разрядов контроля на четность информации в первом -К-ом сегментах микро команды, считываемой из запоминакицег устройства 46j группы информационных выходов 51 запоминающего устройства 46. Блок пуска-останова 6 (фиг.З) содержит триггер 52 и управляемый четырехтактный генератор 53 прямоуголь ный импульсов. Обозначения осей ординат соответс вуют номерам выходов блока пуска-останова (фиг.4), изомерам связей (фиг.5 и 6). введенньпч на фиг. 1. Символом Тд обозначено время срабатывания элемента И 13 (14) и элемента ИЛИ 15, символом Тд- время срабатывания регистра адреса А |, А., А .;4.(адрес соответственно (i-1), i и ({+1)-й микрокоманды, реализуемой устройством). Ячейка регистра 1(16) адреса (фиг.8) содержит элементы И 54-58, элементы ИЛИ 59 и 60,, синхронный универсальный двухступенчатый JKPSтриггер 61 и инвертор 62. Регистр 1(16) адреса предназначен для хранения адреса микрокоманды, считываемой из блока 2(17) памяти. Запись информации в регистр может производиться через внешний вход 21(39), цепь синхронизации для которого не показана, а также через информационные выходы 32 или 40(22). Прием информации по входу 32 происходит по положительному перепаду сигнала на синхровходе С1 при наличии единичного разрешающего сигнала на разрешающем входе Е1. Прием информации по входу 40(22) происходит по отрицательному перепаду сигнала на синхровходе С2 при нулевом сигнале на запрещающем входе Е2. Схема одного разряда (ячейки) ре-, гистра изображена на фиг.8. Процесс записи информации в регистр пояс:няется диаграммами (фиг.5 и 6). Блок 2(17) памяти предназначен для хранения микрокоманд и выдачи их на группы информационных выходов при поступлении сигнала считывания на вход 30(29). Микрокоманда разбита на К-сегментов (фиг.7). Каждый сегмент имеет разрядность, равную 3, причем каждый сегмент еще дополни- . тельно содержит разряд контроля на четность информацией. При считывании микрокоманды каждый сегмент проверяется на четность (по модулю 2) и в случае отсутствия искажений на соответствующем выходе состояния сегментов микрокоманды группы выходов 23(42) появляются единичные импульсные сигналы, соответствующие сегментам без искажений, если единичные импульсы не появляются, то это говорит о том, что данный сегмент считан с искажениями, его выдача на соответствующую группу информационных выходов запрещается (сигналы остаются нулевыми)., а неискаженные сегменты появляются на соответствующей группе выходов 24(41) . Регистр 3(18) предназначен для хранения информатдии о состоянии сегментов,. Исходное состояние регистра перед записью информации в него нулевое. Запись информации в него осуществляется при кратковременном появлении информационных сигналов на группе входов 23(42). Установка регистра в исходное состояние происходит по заднену фронту импульса на его R -входе 38. Элемент И 4(19) предназначен для управления прохождением тактовых импульсов через элемент И 5(20). Элемент 5(20) предназначен для упра ления подачей тактовых импульсов с выхода 31(28) блока пуска-останова на вход элемента РШИ 15. Блок 6 пуска-останова (фиг.З) предназначен для осуществления четырехтактной синхронизации устройст управления. Сигналы на его входах формируют с момента подачи пусковог импульса на пусковой вход 27. , Группа блоков элементов ИЛИ предназначена для подачи сегментов микрокоманд на информационные входы регистра 8. Регистр 8 предназначен для формирования микрокоманд путем замещения искаженных сегментов и хранения сформированных микрокоманд до их вьщачи на выход устройства. Исходное состояние регистра перед записью информации в него нулевое. Запись информации в регистр .прои ходит при кратковременном появлении информационных сигналов на его информационных входах., Установка регистра в исходное нулевое состояние происходит по заднему фронту сигнал на его R-входе 38. Элемент И 9 предназначен для управления передачей сигнала конца микропрограммы. Блок элементов И 10 предназначен для управления выдачей операционной части шкpoкoмaнды на выход 34 устройства. Группа элементов ИЛИ 11,- 11, предназначена для формирования снгн лов о состоянии идентичных сегментов аналогичных микрокоманд записа ных в блоках 2 и 17 памяти. Элемент И 12 предназначен для форм; рования сигнала об отсутствии искаисений в идентичных сегментах ан логичных микрокоманд. Элемент И 13 предназначен для управления подачей тактовых импульсов с выхода 28(31) блока пуска-останова на вход 39(40) элемента ИЛИ 15. Элемент ИЛИ 15 предназначен для формирования сигнала, управляющего вьщачей микрокоманд на выход 34 устройства, сбросом регистр-ов 3 и 18 в нуль и управления приемом информации в регистры адреса. Устройство управления может работать в нормальном режиме работы, в режиме наличия искаженной микрокоманды в одном блоке памяти; и в режиме искажения аналогичных микрокоманд в обоих блоках памяти. В исходном состоянии в регистре 16(1) записан адрес начальной микрокоманды, подлежащей реализации. На группах выходов 23 и 42 блоков 2 и 17 памяти сигналы соответствуют логическому О. Регистры 3 и 18 находятся в нулевом состоянии. Цепи установки исходных состояний регистров 3,8 и 18 не показаны. В нормальном режиме работы по сигналу Пуск на входе 27 схема пускаостанова начинает вырабатывать четырехфазные серии импульсов, состоящих из четырех тактовых импульсов. сдвинутых во времени (фиг.4). Первьй .тактовый импульс первой (третьей) фазы поступает с выхода 29(30) блока б пуска-останова на вход 29(30) считывания блока 17(2) памяти, вследствие чего происходит считывание -микрокоманды по адресу, поступающему на вход 40(22) блока 16(1) памяти. Если микрокоманда считана без искажениЙ5 то на выходах 42(23) блока 17(2) памяти появляются импульсные сигналы логической 1 вследствие чего во всех разрядах регистра записываются единицы, которые отпирают элемент И 19(4), сигнал логической 1 с вькода которого готовит к отпиранию элемент И 20(5). Одновременно на группы информационных выходов 41.- 4Ь( 24.) блока 17(2) памяти подается содержимое сегментов считанной микрокоманды. Эти сегменты через группу К-разрядных блоков элементов ИЛИ 7, (где К - число сегментов в микрокоманде) записываются на регистр 8. Затем на выходе 28(31) схемы пуска-останова формируется следующий тактовый импульс . Через открытьй элемент И 20(5) и элемент ИЛИ 15 он посту11пает на вход 38 блока элементов И 1 и разрешает вьщачу операционной час ти неискаженной микрокоманды на вход 34 устройства. Адресная часть следующей микрокоманды с выхода 32 регистра 8 при этом записывается в регистр 1(16) . Запись происходит следующим образом (фиг.5). Тактовый импульс второй (четвертой) фазы с выхода 28 схемы пускаостанова 6 поступает на разрешающий Е1-ВХОД 38(21) регистра 1(16), разрешая прием информации в регистр по входу 32. Этот же импульс, проходя через элементы И 20(5) и элемент ИЛИ 15, поступает на синхронизируюпщй С1-вход 38 этого регистра и по переднему фронту ( положительному перепаду) этого импульса происхо дит запись адреса следующей микрокоманды в регистр. Задним фронтом этого же импульса происходит установка регистров 3 и 18 в исходное состояние. Далее в нормальном режиме работы считывание очередной микрокоманды из блока 2(17) памяти и запись следующего адреса в регист 16(1) происходит при поступлении тактовых импульсов третьей и четвертой (первой и второй) фазы на выходы 30(29) и 31(28) схемы пускаостанова аналогично описанному. При появлении сигнала логической 1 на выходе 33 регистра В, который св детельствует об окончании реализуемой микропрограммы, этот сигнал отпирает элемент И 9, и сигналом, пос тупающим с выхода элемента ИЛИ 15 н вход 38 этого элемента, происходит остановка вьщачи тактовых импульсов на выходы схемы пуска-останова 6. |Устройство прекращает работу. При выявлении искажений в микрок манде, которая считывается из любог блока памяти, происходит переход к второму режиму работы устройства к режиму наличия искаженной микрокоманды в одном из блоков памяти. Это происходит следующим образом. Если при считывании микрокоманды например, из блока 17(2) памяти обнаружено искажение,то те ее сегмент в которых обнаружена ошибка, на соо ветствуюЕЦие группы информационных выходов 41(24) не высьшаются, а на соответствующих этим сегментам выходах 42(23) импульсный сигнал ло712гической 1 не выдается. Эта информация о состоянии сегментов записывается в регистре 18(3). Нулевые разряды, соответствующие искаженным сегментам, с выхода регистра 18(3) запирают элемент И 19(4), вследствие чего остается заперт элемент И 20(5). Исправные же сегменты с выходов 41(24) записываются в регистре Я. Затем на выходе 28(31) схемы пуска-останова появляется тактовый импульс второй (четвертой) фазы, по приходу этого импульса происходит перестройка устройства для считывания с логичес- кой микрокоманды из другого блока памяти. Для этого адрес этой микрокоманды из регистра 16(1) переписывается в регистр 1(16). Это происходит следующим образом. Так как элементы И 5,13,14 и 12 заперты, то на выходе 38 элемента . РШИ 15 сигнал остается равным логическому О вследствие чего запрещается запись информации в регистр 1(16) по входу 32 и разрешается запись по входу 40(22). Тогда по заднему фронту тактового импульса второй (четвертой) фазы, поступающего на синхронизирующий С2-вход 28 регистра 1(16), происходит запись адреса искаженной микрокоманды с выхода 40(22) регистра 16(1) на регистр 1(16). Далее по приходу тактового импульса третьей (первой) фазы на вход 30(39) происходит считывание микрокоманды из блока 2 (17) памяти по адресу, установленному на его входе 22(40). Если при считывании все сегменты микрокоманды окажутся неискаженными, то эти сегменты поступают на группы информационных выходов 24(41) блока 2(17) памяти и группу блоков элементов ИЛИ 7-. - 7 и записываются в регистр 8. При этом на выходах 23(42) блока 2(17) памяти формируются импульсные сигналы логической 1 которые записываются в регистр 3(18). и тем самым отпирают элемент И 4(19), подготавливая к отпиранию элемент И 5(20). Затем на выходе 31(28) формируется тактовый импульс четвертой (второй) фазы. Проходя через открытый элемент И 5(20) и элемент ИЛИ 15, он разрешает выдачу операционной части микрокоманды с группы информационных выходов регистра 8 через блок элементов И 10 на вы1.3 ход 34 устройства. Адресная часть с вькода 32 регистра 8 записывается в регистр 16(1). Это происходит под действием этого же тактового импуль са (фиг,5). Сначала он поступает на разрешающий 31(28) регистра 16(1), а затем через элементы И 5(20) и элемент ИЛИ 15 на синхронизирующий С1-ВХОД регистра (16) за счет чего по переднему фронту (положительному периоду) производится запись адреса микрокоманды в регистр. По заднему фронту этого импульса производится сброс регистров 3(18), вследствие чего устройст во переходит в нормальный режим работы. Если же при повторном считывании аналогичной микрокоманды из блока 2(17) памяти в ней также обнаружены искажения, то устройство переходит в третий режим работы. Это происходит следующим образом. На выходах 23(42) так же, как это бьшо при переходе во второй режим работы появляются сигналы, характеризующиеся состояние сегментов : в ан.алогичной микрокоманде. Эти сиг налы записываются в регистр 3(18). Так как при зтом хотя бы один разряд регистра (именно тот, который соответствует искаженному сегменту) нулевой, элемент И 4(19) заперт, запирая и элемент И 5(20). Вследствие этого элемент И 13(14) подготов лен к отпиранию. Неискаженные сегме ты с группы информационных выходов 24(41) блока 2(17) памяти через группу блоков элементов ИЛИ 7 - 7 :запишутся в регистре 8. Если сред искаженных сегментов аналогичных Микрокоманд, считанных из блоков 17 и 2(2 и 17) памяти не окажется двух одинаковых, т.е. одноименных, то при этом в регистре 8 сформирует ся полный набор неискаженных сегмен тов микрокоманды. Так как при этом хотя бы на одном из входов каждогр элемента из группы элементов ИЛИ 11-(- 1 Ъ имеется сигнал логической 1, а значит на каждом выходе группы элементов ИЛИ 1Ц 1 L имеет ся сигнал логической 1, благодаря чему элемент. И 12 открыт. Тем самым элемент И 14(13) подготовлен к отпиранию еще по одному входу. При пояапении тактового импульса чет7 14 вертой (второй) фазы на выходе 31(28) схемы пуска-останова 6 этот импульс, проходя через элементы И 14(13) и элемент ИЛИ 15, поступает на вход 38 блока элементов И 10, и операционная часть микрокоманды поступает на выход 34 устройства. Адресная часть следующей микрокоманды йри этом записывается с выхода 32 регистра 8 в регистр 16(1). Это происходит аналогично тому, как происходила запись адресной части во втором режиме работы. Задним фронтом импульса, поступающим с выхода 38 элемента ИЛИ 15, происходит сброс регистров 7 и 18, после чего схема оказывается возвращенной в нормальный режим работы. Если же в третьем режиме искажения возникают в одноименных сегментах аналогичных микрокоманд, то сигналы микроопераций на выход 34 устройства не вьщаются из-за того, что блок элементов И 10 заперт вследствие того, что элементы И 5, 12, 20, 13 и 14 окажутся запертыми, а на выходе 38 элемента ИЛИ 15 сигнал,соответствующий логическому О. Однако устройство продолжает свою работу. Адрес искаженной микрокоманды попеременно передается из одного регистра адреса в другой и обратно, и считывание ее продолжается до правильного ее считывания или до прекращения подачи тактовых импульсов схемой пуска останова на выходы 28-31. В том случае, если причиной искажения одноименных сегментов был сбой при считывании микрокоманды, это позволяет после нескольких циклов повторного считывания продолжить выполнение микропрограммы. Технико-экономические преимущества предлагаемого устройства по отношению к известному, и базовому объекту - устройству управления процессора №ЗА системы ЕСС фирмы Белл Систем можно оценить величиной , показывйющей на сколько процентов сокращается вероятность отказа устройства по сравнению с известным: , cAa И где 0 вероятность отказа известного устройства; (j - вероятность отказа предлагаемого устройства.

4S127

(Jf)

Ф1/г2

Ф1/г.

.4

Раз/уя б/ HO/ mjSjG/Tjf jvcr tfe/7 //c c/776 i-no v /ec/7 So cezffe/fmffS S cf / ec//ue vacmt/ / K-f(O i/vec/7 So cee e /TTff So Scei

Фиг. 6

фуг. 7

21-i fJS

40-f

m-iT

3B

/

rr

22-i (40)

6f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке №3459916/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Перестраиваемое микропрограммное устройство управления | 1976 |

|

SU646333A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-03—Подача