to

Ci 4

СО

Изобретение относится к вычисли - , тёльыой технике, в частности к авуоматизкрованиьв системам контроля цифровых устройств, и ьюжет быть использовано для контроля цифровых устройс;|рв в процессе их производства и эксплуа тации.

Известно устройство для контроля цифровых блоков, соле рзкащее блох ввода, блок памяти, 1«5Ш4утатор, блок . сравнения, блок управления и схему О индикации неисправностиJ l.

Недостатком устройства является большой расход памяти на хранение t&c- тов и эталонов, а также невозможности обеспечения контроля цифровое блоков, US работающих с высоким реальным быстро-( действием.

, Наиболее близким по технической сущности к предлагаемсму является устройство для контроля дискретщах JQ объектов сгодержаадее блок ввода, блок памяти блок сравнения, блок управления, кс 1мутатори и многовходовьШ элемент ИЛИ.

Первый выход блока вовода связан с 25 первым входом блока памяти, второй вход которого подклйчен к первому выходу блока управлеиия. Второй вы- ход блока управления соединен с первым &ХОДСШ блока сравнения, а второй 0 блока вврда связан с первым входом блока управления, третий вьгход которого подключен к входу блока ввода . Первый выхсод блока памяти подсоединен к второму входу блЬка срав нения ,„ Второй выход блока памяти пддеоединен к первому входу первого ко1Ф1утаФара, к второму входу которого подасшчен четвертый выход блока управления. Выход первого колв«утатора связан с . nepBt j входом многовходового элемен- та или, к второму входу которого йодаУ ключей первый выход второго кеддаута тора. Второй выход второго котлуха тора связан с третьим входом блока управления. Первый вход второго ко1«4у 5 татора подсоединен к пятого входу .блока управления. Выход блока сравнения подключен «второму входу блока управления. Выход многовходового элемента ИШ1 и второй вход ВТОРОГО КОММу-еп

та тора являются соо-гветственно выхоаом н входом, устройс тва.. В таком устройстве lio сигналу блока управления из блока памяти чев)ез коммутатор и многовходовый элемент ИЛИ выдаются . TecTOBibBS наборы на контролируемый объектi Реакции контролируемого объекта на 5гестовые набора через KcaswyTaтор подаются я& блок сравнения, где сравниваются с эталонными реакциями, поступакадими из блока памяти. Сигнал 60 сравнения или несравнения выходных реакций с эталоиньаш поступает в блсж управЛенияС23.

К недостаткам этого устройства следует отнести большой ббъект блока 65

памяти для хранения тестовых иабрров и эталонных реакций, а такке невозможность обеспечения контроля цифровых блоков, работающих с высоким ре sunbmstA быстродействием из-за налиния двух обращений/к блоку а тестом и эталоном, а также из-за задержки сигналов в целях коммутаций.

Цель изобр 1 ения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля дискретных объектов, содержащее блок памяти, блок врода, блок управления, блок сравнения, причем группа выходов блока ввода подключена к i pynne информационных входов блока памяти, угрравляюидай вход которого связан с первьм выходом блока управлений, второй выход которого соединен с входом блока ввода/ группа инфррмационных выходов блока памяти подкл очена к перзвой Группе соответствующих входов блока сравнения, первый выход которого является контрольным выходом у тро8ства а второй выход связан с входот«5 блока управления, вторая группа информационных выходов блока памяти ; соединена с группой Соответствующих ; входов контролируемого блока, введе-. ны комбинационный сутФ1атор с циклический переносом и регистр, причем первая группа информационных входов комбинационного сумматора с циклическшл переносом подключена к группе выходов контролируемого, блока, .вторая группа информационные входов комбинационного сумматора с циклическим пе1 еносом связана с группой выходов .регистра, подключенных к второй группе соответствующих входов блока сравнения, группа выходов ксйлбинационного сушлатора с циклическим переносом соединена с группой входов регистра.

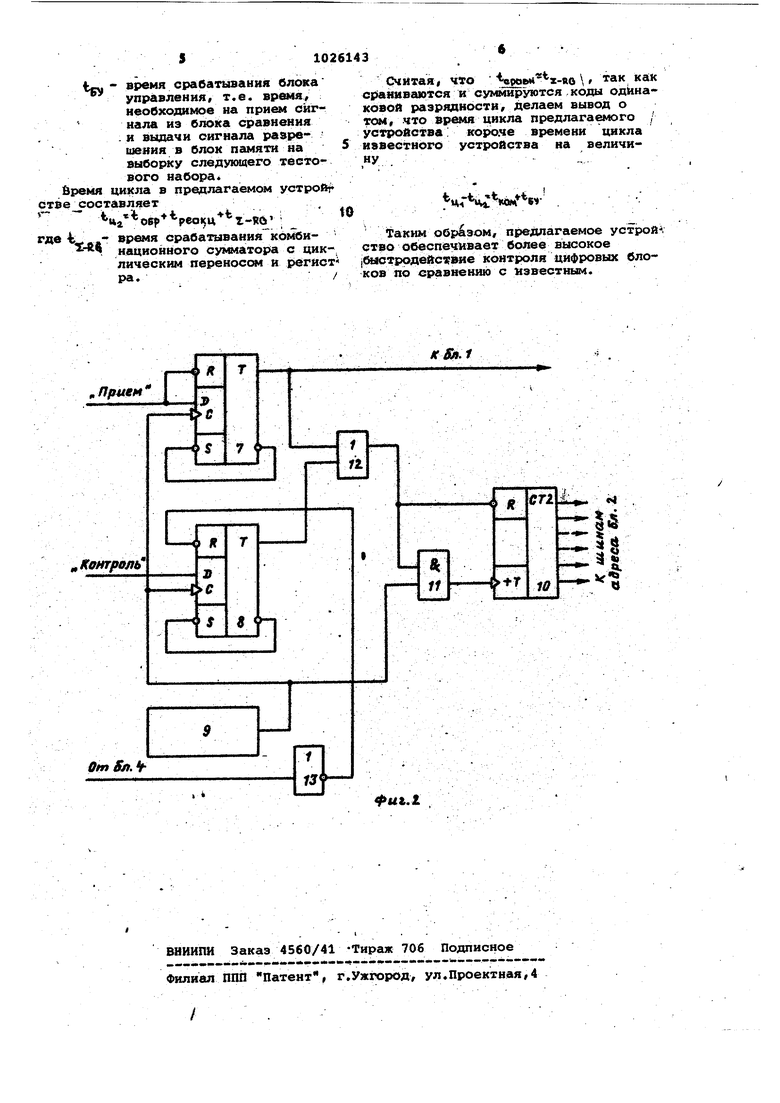

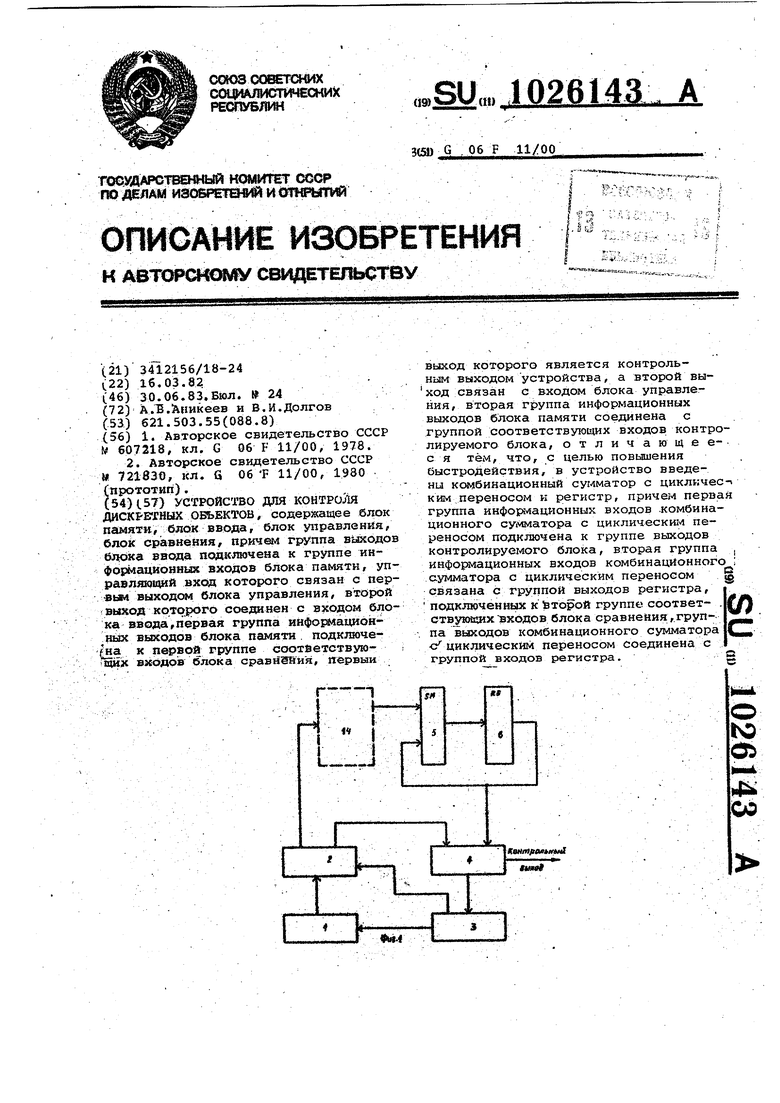

На фиг.1 представлена структурная схема устройства для контроля дискрет ных объектов; на фиг.2 - функциональна схема блока управления. ,

Устройство Для контроля дискретных объектов содержит блок 1 ввода, блок 2 памяти, блок 3 управления, блок 4 сравнения, комбинационный сумматор 5 с циклическим переносом, , регистр. 6./

лок управления выполнен по схеме управляющего автомата с жесткой логикой и содержит два C-U триггера 7 и В, генератор 9 импульсов, двоич. ный счетчик,. 10, элемент 11, элемент.: ИЛИ 12,элемент НЕ 13. Выход генера тора Эямпульсов подсоединен к С-вхОдам триггеров 7 и 8 и. к первому входу элемента И 11. Входы R и В Триггера 7 соединены между собой и coBiwecTHo с входом Т триггера 8 являются внешними входами блока 3 управления. Входы 5 триггеров 7 и 8 связа.йы со инверсными выходам а вход ft триггера 8 подключен к вы ходу элемента НЕ 13, вход которого является входом блока 3 управления. Прямые выходы триггеров 7 и 8 евяза ны с первым ивторЕлм входами, еоответственно элемента ИЛИ 12, выход которого подсоединен к входу R счет чика 10 и второму вкоду элемента И Выходу элемента И 11 связан.со счетным входом счетчика 10. Выходы счет чика 10 являются вторым выходом бло .ка 3 управления и подключены к адре ным шинам блока 2 памяти. Прямой :вы ход триггера 7 подключен к входу бл ка 1 ввода. Кроме того, устройств содержит контролируем цифровой блок 14. Устройство работает следующим об разом. , Па сигналу с блока 3 управления рез блок 1 ввода в блок 2 памяти по ступает тестовая информация в виде TectoBbix наборов. Ир, сигналу начала контроля, вглдаваемому с блока 3 управления, блок 2 памяти начинает подавать тестовые наборы на контролируемый цифровой блок. Реакции на тестовые наборы поступают на сумматор 5 с циклическим переносом, где суммируются с циклической су1да«ой, полученной в предыдущих циклах, хра нящейся в регистре б и получаемой на сумматоре 5 ( в исходном состоянии регистр б в О). После прохождения всех тестовых наборов блок памяти выдает на блок 4 сравнения эталонную контрольную сумму, которая сравнивается с контрольной сум мой, полученной и результате прохождения тестовых наборов и хранящейся в регистре б. Поскольку в блоке 2 па мяти хранятся только тестовые наборы и не хранятся, эталонные реакции, это приводит к..сокращению объема блока 2 памяти для хранения тестовых эталонов в два раза. По результатам сравнения блок 4 сравнения выдает сигнал исправности или неисправности контролируемого цифрового блока. Таким образом, устройство работает в двух режимах: в реж1те приема тестовых наборов и эталонной суммы и в режиме контроля.. В соответствии с этими режимами и функционирует блок 3 управления. Сигнал Прйшл поступает на вход приема триггера 7 и сохраняется на зквде до тех пгор, пока не примется в блок 2 памяти вся тестовая нйфо1Е 1ация. Триггер 7 устанавливается в един счное положение и разрешает прохождение импульсов с выхода генератора 9 импульсов через элемент И 11 на счетный вход счетяика 10, а также выдачу тестов из блока 1 ввода в блок 2 памяти (до прихода сигнала Прйет« / ик обнулен нулевым сигнелой С гЦрвых выходов триггеров 7 и 8 через элемент ИЛИ 11). Счётчик 10 начинает считать и тестовая инфорла ция, по- , ступающая с блока 1 ввода в блок 2 памяти, записывается в массив последовательных ячеек блока 2. После записи всех тестов сигнал Прием снимается, и триггр 7 устанавливается в О, устанавливается в О и счетчик 10.Режим Прием заканчивае.тдя..., . , . .,..; В режиме Контроль на вход , триггера 8 поступает единичный.им- , пульсный сигнал, который устанавлиаает триггер 8 в . Сигнал с прямого выхода триггера 8 через элементы 121 и 11 разрешает подачу импульсов на счетный вход счетчика 10. Счетчик 1U начинает считать и блОк 2 памяти Bt д§ет тесты на контролируемый ( цифровой)блок . После прохождения всех теог тбв я сравнения контрольной суммы с эталонной блок 4 сравнения через v элемент НЕ 13 устанавливает триггер 8 ; в О, счетчик 10 Сбрасывается в € и режим Контроль заканчивается. Если контрольная и эталонная суммы не совпадают, тО счетчик 10 выходит за границу массива тестов, что соответствует отсутствию сигнала на контрольном выходе блока 4 сравнения и является признаком наличия неисп- : равности в контролируемом (цифровом) блоке 14. В устройстве в блоке памяти на одйй тестовый набор приходится одна эталонная реакция. Эта тестовая инфор аци занимает в блоке памяти две ячейки. 0 предлагаемом устройстве хранятся толькб тестовые наборы и одну ячейку памяти занимает контрольная сумма. Следовательно, достигается сбкраздение объема памяти для хранения тестовой информации в предлагаемом устройстве по сравненио с известным в два раза. Это ведет к сокраще нию труяое всости изготовления и стоимости блока, памяти. цикла, т.е. время между хрзумя выборками тестовых наборов из блока памяти, в .иэ вестнс устройстве составляет ц/ оер ко реокц сроЕ.. где ц - время цикла известного устройства; - время обращения к блоку памяти за тестовым набо; . ром; . . , . время срабатывания элементов Коммутации/ время реакции контроля- .. .руемого объекта на тестовый набор; 4 - время срабатывания-блока;. сравнения; tgu - время срабатывания блока управления, т.е. время, иеобходимое на прием сйг нала из сравнения -И выдачи сигнала разре . шения в блок памяти на выборку следуквдего тестового набора Ёремя цикла в предлагаемом ycTpofirf стве составляет t« ..,-„...-, i Ц2- окр рео1 и -г-11б время сраба1ывания коМбинационного сумматора с цик-, лическим переносом и ЕЮГИСТ ра.. / Считая| что Црою4 Ч-ио , так как сманиваются и суммируются коды одинаковой разрядности, делаем вывод о том, что время цикла предлагаемого / yctpoftCTBa; коро.че времени цикла известного устройства на величину.: 4;-4cW 6r Таким образом, предлагаемое устрой ство Обеспечивает более высокое (Ллстродейс вие контроля цифровьос блоков по сравнению с известным.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1432530A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

Фиг,1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Время-импульсное делительное устройство | 1977 |

|

SU721830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-30—Публикация

1982-03-16—Подача