Изобретение относится к вычислительной технике и может быть использовано для сопряжения блоков оперативной и постоянной памяти с произвольной выборкой с общей шиной микро-ЭВМ. Цель изобретения - повышение надежности устройства.

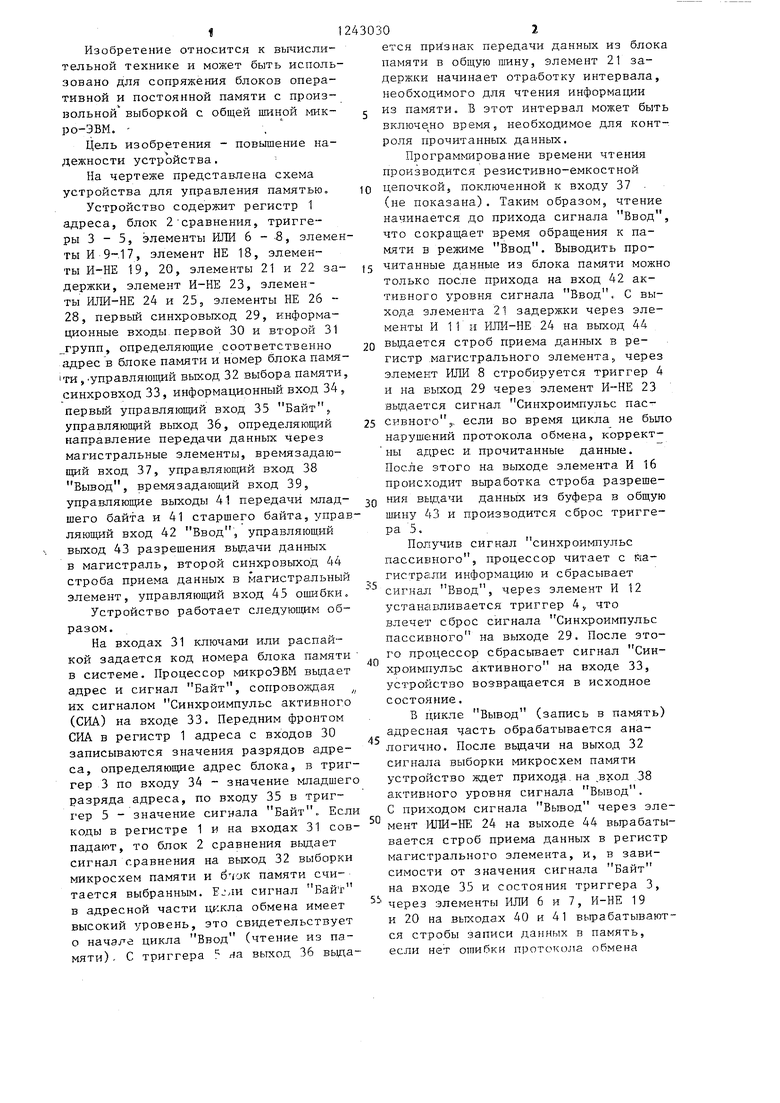

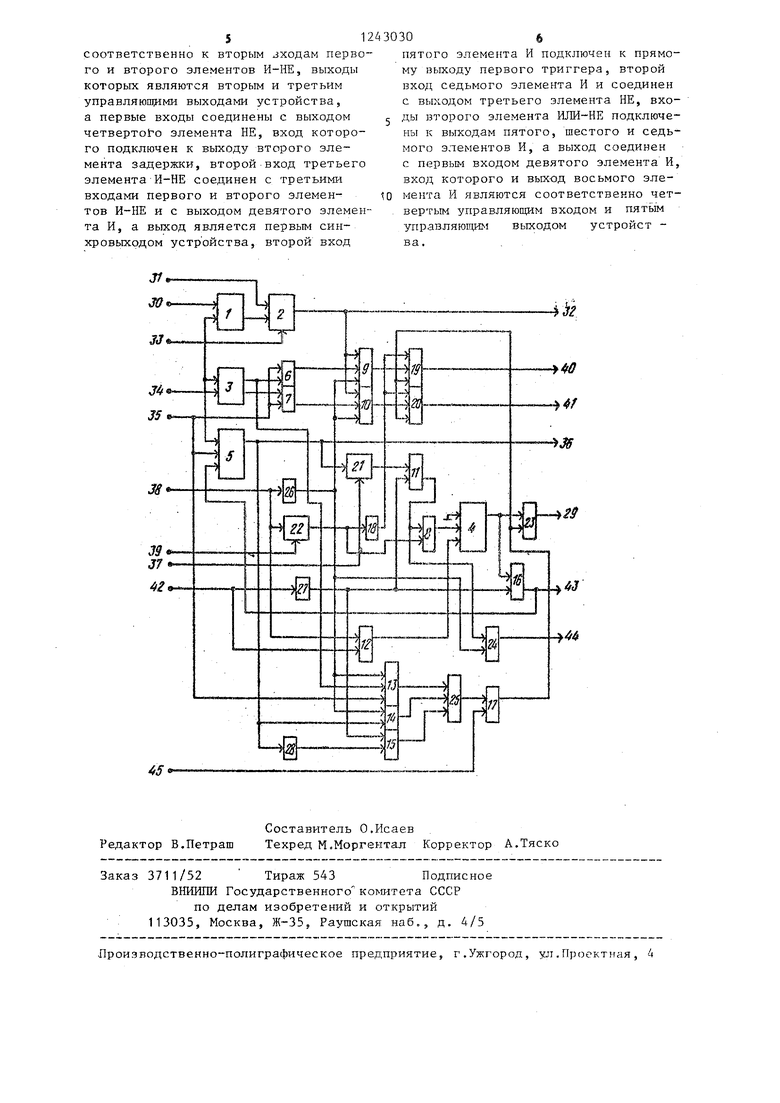

На чертеже представлена схема устройства для управления памятью.

Устройство содержит регистр 1 адреса, блок 2 сравнения, триггеры 3 - 5, :элементы ИЛИ 6 - , элементы И , элемент НЕ 18, элементы И-НЕ 19, 20, элементы 21 и 22 задержки, элемент И-НЕ 23, элементы ШШ-НЕ 24 и 25, элементы НЕ 26 - 28, первый синхровыход 29, информационные входы.первой 30 и второй 31 „групп, определяющие соответственно адрес в блоке памяти и номер блока памя- ITH, Управляющий выход 32 выбора памяти, синхровход 33, информационный вход 34, первьш управляющий вход 35 Байт % управляющий выход 36, определяющий направлеьше передачи данных через магистральные элементы, времязадаю- щий вход 37, управляющий вход 38 Вывод, времязадающий вход 39, управляющие выходы 41 передачи младшего байта и 41 старшего байта, управляющий вход 42 Ввод, управляющий выход 43 разрешения выдачи данных в магистраль, второй синхровыход 44 строба приема данных в магистральный элемент, управляющий вход 45 ошибки.

Устройство работает следующим образом.

На входах 31 ключами или распайкой задается код номера блока памяти в системе. Процессор микроЭВМ выдает адрес и сигнал Байт, сопроволщая их сигналом Синхроимпульс активного (СИА) на входе 33. Передним фронтом СИЛ в регистр 1 адреса с входов 30 записываются значения разрядов адреса, определяющие адрес блока, в триггер 3 по входу 34 - значение младшег разряда адреса, по входу 35 в триг- г ер 5 - значение сигнала Байт. Есл коды в регистре 1 и на входах 31 совпадают, то блок 2 сравнения выдает сигнал сравнения на выход 32 выборки микросхем памяти и блок памяти считается выбранным. сигнал Байт в адресной части цикла обмена имеет высокий /ровень, это св1щетельствует о начале цикла Ввод (чтение из памяти) , С триггера на выход 36 выдается признак передачи данных из блока памяти в общую пгину, элемент 21 задержки начинает отработку интервала, необходимого для чтения информации

из памяти. Б этот интервал может быть включено время, необходимое для контроля прочитанных данных.

Программирование времени чтения производится резистивно-емкостной

цепочкой, поключенной к входу 37 . (не показана). Таким образом, чтение начинается до прихода сигнала Ввод, что сокращает время обращения к па- М.ЯТИ в режиме Ввод. Выводить прочитанные данные из блока памяти можно только после прихода на вход 42 активного уровня сигнала Ввод. С выхода элемента 21 задержки через элементы И 11 и ШШ-НЕ 24 на выход 44

выдается строб приема данных в регистр .магистрального элемента, через элемент ИЛИ 8 стробируется триггер 4 и на выход 29 через элемент И-НЕ 23 вьщается сигнал Синхроимпульс пассивног о.,. если во время цикла не было наруа ений протокола обмена, коррект- ны адрес и. прочитанные данные. После этого на выходе элемента И 16 происходит выработка строба разрешеНИН вьщачи данных из буфера в общую шину 43 и производится сброс триггера 5.

Получив сигнал синхроимпульс пассивного, процессор читает с fta- гистрали информацию и сбрасывает

сигнах. Ввод, через элемент И 12 устанавливается триггер 4,, что влечет сброс сигнала Синхроимпульс пассивного на выходе 29. После этого процессор сбрасывает сигнал Синхроимпульс активного на входе 33, устройство возвращается в исходное состояние.

В цикле Вывод (запись в память) адресная часть обрабатывается аналогично. После вьдачи на выход 32 сигнала выборки микросхем памяти устройство ждет прихода.на ,вход 38 активного уровня сигнала Вывод. С приходом сигнала Вывод через элемент ШШ-НЕ 24 на выходе 44 вьфабаты- вается строб приема данных в регистр магистрального элемента, и, в зависимости от значения сигнала Байт на входе 35 и состояния триггера 3,

через элементы ИЛИ 6 и 7, И-НЕ 19 и 20 на выходах 40 и 41 вырабатываются стробы записи данных в память, если нет ошибки протокола обмена

и корректны адрес и данные, поступившие в блок. Вместе с выработкой стробов записи запускается элемент 22 задержки, программируемый по входу 39 резистивно-емкостной цепочкой (не по- казана) на время срабатывания микросхем памяти в режиме записи. После отработки задержки через элемент НЕ 18 и элементы И-НЕ 19 и 20 происходит сброс на выходах 40 и 41, стробов за- писи, через элемент ИЛИ 8 стробиру- ется триггер 4 и на выходе 29 появляется сигнал Синхроимпульс пассивного.

В устройстве имеется схема контро- ля протокола обмена, выполненная на элементах И 13 - 15 и ИЛИ-НЕ 25, которая вьивляет следующие ошибочные комбинации управляющих сигналов:

Байтое, Выв од ;

Байтц S- ВывоД( . Байт ц , где БайТц - значение сигнала в адресной части цикла обмена, записанное в триггер 5 (в - высокое значение сигнала, и - низкое) .

Выход схемы контроля протокола обмена и вход ошибки 45 объединены на элементе И 17, с выхода которого, в случае возникновения любой ошибки, блокируется вьздача стробов записи на выходы 40 и 41 и сигнала Синхроимпульс пассивного на выход 29.

Формула изобретения

Устройство для управления памятью содержащее регистр адреса, входы которого являются информационными входами первой группы устройства, а выходы соединены с входами первой группы блока сравнения, входы второй группы которого являются информационными входами второй группу устройства, а выход подключен, к первым входа первого и второго элементов И и является первым управляющим выходом устройства, один из информационных входов которого соединен с информационным входом первого триггера, прямой и инверсный выходы которого подключены соответственно к первым входам первого и второго элементов ИЛИ, а синхровход соединен с синхровходами регистра адреса и блока сравнения и является синхровходом устройства, вторые входы первого и второго элементов И подключены соответственно к выходам первого и второго элементов ИЛИ, а третьи входы соединены

0

5

Q

5

0

5

0

5

С выходом первого элемента НЕ, вход которого соединён с входом второго элемента задержки и с первым входом четвертого элемента И и является вторым управляющим входом устройства, второй вход четвертого элемента И подключен к входу второго элемента НЕ и является третьим управляюш 1м входом устройства, а выход соединен с входом установки второго триггера, информационный вход которого подключен к входу логического нуля устройства,а синхровход соединен с выходом третьего элемента ИЛИ, второй вход которого подключен к выходу второго элемента задержки, вторые входы первого и второго элементов ИЛИ являются первьш управляющим входом устройства, выход второго элемента НЕ соединён с вторым входом третьего элемента И, вторые входы первого и второго элементов задержки являются соответственно первым и вторым времязадающими входами устройства, отличающееся тем, что, с целью повьшения надежности устройства, в него введены третий триггер, первый, второй и третий элементы И-НЕ, пятый, шестой, седьмой, восьмой и девятый элементы И, третий и четвертый элементы НЕ, причем син- хровод третьего триггера соединен с синхровходом устройства, информационный вход подключен к первому управляющему входу устройства и к третьему входу пятого элемента И, выход соединен с вторым входом шестого элемента И, с входом третьего элемента НЕ,, с первым входом первого элемента задержки и является четвертым управляюш 1м выходом устройства, а вход установки третьего триггера подключен к выходу восьмого элемента И, первый вход которого соединен с инверсным выходом второго триггера и с первым входом третьего элемента И-НЕ, а второй вход подключен к первому входу седьмого элемента И и к выходу элемента НЕ, первый вход третьего элемента И соединен с выходом первого элемента задержки, а выход подключен к первому входу третьего элемента ИЛИ и к первому входу первого элемента ШШ-НЕ, второй вход которого соединен с первыми входами пятого и шестого элементов И и с выходом первого элемента НЕ, а выход является вторым син- хровыходом устройства, выходы первого и второго элементов И подключены

51

соответственно к вторым входам перво го и второго элементов И-НЕ, выходы которых являются вторым и третьим управляющими выходами устройства, а первые входы соединены с выходом четвертого элемента НЕ, вход которого подключен к выходу второго элемента задержки, второй вход третьего элемента И-НЕ соединен с третьими входами первого и второго элементов И-НЕ и с выходом девятого элемен та И, а выход является первым син- хровыходом устройства, второй вход

Редактор В.Петраш

Составитель О.Исаев

Техред М.Моргентал Корректор А.Тяско

Заказ 3711/52 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35. Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

430306

пятого элемента И подключай к прямому ныходу первого триггера, второй вход седьмого элемента И и соединен с выходом третьего элемента НЕ, вхо- с ды второго элемента ИЛИ-НЕ подключены к выходам пятого, шестого и седьмого элементов И, а выход соединен с первым входом девятого элемента И, вход которого и выход восьмого эле- 0 мента И являются соответственно четвертым управляющим входом и пятьм управляющим выходом устройст - ва. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения, блоков оперативной и постоянной памяти с произвольной выборкой с общей шиной микроЭВМ. Целью изобретения является повышение надежности устройства. Устройство содержит регистр адреса, блок сравнения, триггеры, элементы И, НЕ, И-НЕ, ИЛИ-НЕ, синхровход, управ- пяющие входы Байт, Ввод, Вывод, времязадающие входы, вход ошибки, выходы выбора памяти, стробов записи чладшего и старшего байтов, строба разрешения выдачи данных в магистраль и строба приема данных в маги- :тральный элемент. Устройство обеспечивает управление режимом работы микросхем памяти и магистральных элементов и контроль корректности протокола обмена по общей шине с учетом результатов контроля передачи данных по информационной магистрали. 1 йл. (О

| Малые ЭВМ и их применение./Под ред | |||

| Б.Н.Наумова | |||

| М.: Статистика, 1980, с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

| Искроудержатель для паровозов | 1920 |

|

SU588A1 |

| Котел для водяного отопления с внутренним перегревателем воды для побуждения циркуляции в сети и с регулятором наружной температуры котла | 1924 |

|

SU573A1 |

Авторы

Даты

1986-07-07—Публикация

1984-09-21—Подача