Изобретение относится к импульсной технике и можут быть использовано при построении хронизаторов, цифровых синтезаторов частоты, электромузыкальных инструментов и других устройств, в которых требуются делители частоты с любым чтением коэффициентом К деления частоты следования входных (тактовых) импульсов.

Цель изобретения - упрощение делителя частоты.

I

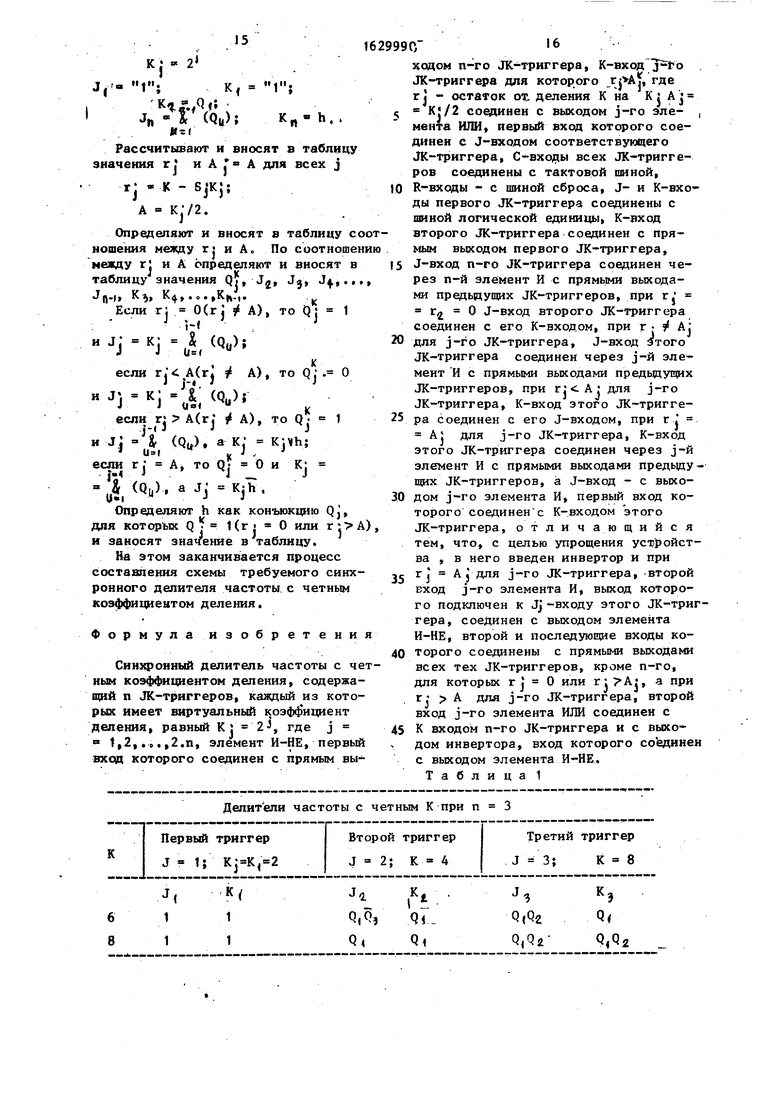

На чертеже приведена электрическая функциональная схема синхронного делителя частоты с четным коэффициентом деления К 60 (с числом JK-триг- геров ).

Делитель частоты содержит с первого по шестой JK-триггеры 1-6, с перво- го по пятый элементы И 7-11, элемент ИЛИ-НЕ 12, инвертор 13, первый и второй элементы ИЛИ 14 и 15, входную шину 16 и шину 17 сброса, которые соединены соответственно с тактовыми входами и с входами сброса всех JK- триггеров 1-6. J- и К-входы первого JK-триггера 1 соединены с шиной логической единицы. Прямой выход шестого JK-триггера 6 соединен с первым входом элемента И-НЕ 12, выход которого соединен с входом инвертора 13 и с первым входом первого элемента И 7, выход которого соединен с J-входом третьего JK-триггера, выход третьего элемента И 9 соединен с J-входом четвертого JK-триггера 4 и с первым входом первого элемента ИЛИ 14, вы- .ход которого соединен с К-входом четвертого JK-триггера 4„

Выход четвертого элемента И 10 соединен с J-входом пятого JK-триггеоэto

со

СО СО

pa 5 и с первым входом второго эле- мента ИЛИ 15, выход которого соединен с К-входом пятого JK-триггера 5. Прямой выход первого JK-триггера 1 соединен с первыми входами второго, третьего четвертого и пятого элементов И8-1Г, с вторым входом элемента ИЛИ-НЕ 12 и с J- и К-входами второго JK-триггера 2, прямой выход которого соединен с вторыми входами второго, третьего, четвертого и пятого элементов И8-11 и с третьим входом элемента И-НЕ 12,

Второй вход первого элемента И7 соединен с выходом второго элемента И8 и с Е-входом третьего JK-триггера 3, прямой выход которого соединен с третьими входами третьего, четвертого и пятого элементов И9-11„ Прямой выход четвертого JK-триггера А соединен с четвертыми входами четвертог и пятого элементов И 10,11 и элемент ИЛИ-НЕ 12, пятый вход которого соединен с прямым выходом пятого JK- триггера 5 и пятым входом пятого элемента И 11, выход которого соединен с J-входом шестого JK-триггера 6, К-вход которого соединен с вторыми входами первого и второго элементов ИЛИ 14 и 15 и с выходом инвертора 13

Устройство работает в соответствии с логическими уравнениями для J- и К-входов JK-триггеров 1-6 в функции выходных сигналов Qyj-Qg этих JK-триггеров. При этом JK-триггеры 1-6 при появлении импульса на шине 16 переключаются в противоположное состояние, если на их J- и К-входах одновременно присутствуют высокие уровни (логические единицы - 1); устанавливаются в единичное состояние, если высокий уровень присутствует лишь на J-входе; устанавливаются в нулевое состояние, если высокий уровень присутствует лишь на К-вхо- де; сохраняет прежнее состояние, если на их J- и К-входах одновременно присутствуют низкие уровни (логического нуля - О).

Известны синхронные делители частоты с четным коэффициентом деления содержащие по три JK-триггера, кото- торые работают в двоичном коде с весми разрядов

(... -4-2-1,

кратными степени числа 2„

Поскольку схема делителя частоты на JK-триггерах (ниже и в таблицах под названием триггер имеется ввиду JK-триггер) определяется логическими уравнениями Jj- и К:-входов его

0

5

триггеров, то для построения требуемого делителя частоты на триггерах достаточно знать эти уравнения. В табл.1 приведены логические уравнения для JJ- и Kj-входов триггеров,

которые составлены по схемам Мб, М8, приведенным в табл.603б для делителей частоты на триггерах при и имеющих и , где j-условный порядковый номер триггера; j 1,2, ..., n; jmq)(n.B этой таблице для каждого j-ro триггера введен условный коэффициент

t

Kj 2J

деления частоты f входных тактовых (считываемых) импульсов.

Если рассмотреть работу делителя частоты, коэффициент К деления частоты которого равен

h

К 2

30

то на выходе каждого j-ro триггера будет сигнал формы меандр, частота

Ч

которого равна

35

Jj-f/K},

а длительность импульса уровня логической единицы на выходе каждого ,j-ro JK-триггера равна

40

-J

Kj/2,

Если же -взять делитель частоты с коэффициентом

45

К t 2

п

0

п

деления частоты f, не равном 2, то в последнем периоде сигнала на выходе каждого j-ro триггера сигнал меандр будет искаженным; если длительность последнего периода сигнала на выходе j-ro JK-триггера меньше т.е.

Kj/2,

55

t Kj/2,

то этот триггер в последнем К-м состоянии делителя частоты будет находиться в нулевом состоянии, сигнал на прямом выходе Q: этого триггера будет равен логическому нулю

„1-..

Если длительность последнего К-го периода будет больше Ki/2, т.е

,

то в К-м состоянии делителя частот на прямом выходе Qj j-ro триггера будет присутствовать уровень логической единицы

К

Q; 1.

J

При равенстве к

KJ/2

значение нулю

Q. будет равно логическому

i

О

Далее в тексте и во всех таблицах параметр К-/2 обозначается А или, опуская индекс, А

Если взять частное S;

KJ/23

)

от деления

К на К}, то целая часть покажет количество полных периодов на выходе j-ro триггера, а остаток от деления г , определит длительность t последнего периода.

Во всех предыдущих выражениях и далее условный показатель степени К показывает, что данный параметр определяется для последнего К-го состояния делителя частоты.

Так как рассматриваются только длители частоты с. четным коэффициентом К деления частоты, то для первого триггера всегда

rj - г, - 0.

Он всегда в последнем состоянии делителя будет находиться в состоян логической единицы

К

Qi

i,

а для последнего n-го триггера остаток г„ всегда равен (кроме )

rj -rn , этот триггер будет иметь

1 .

для всех триггеров все п триггеров будут

1

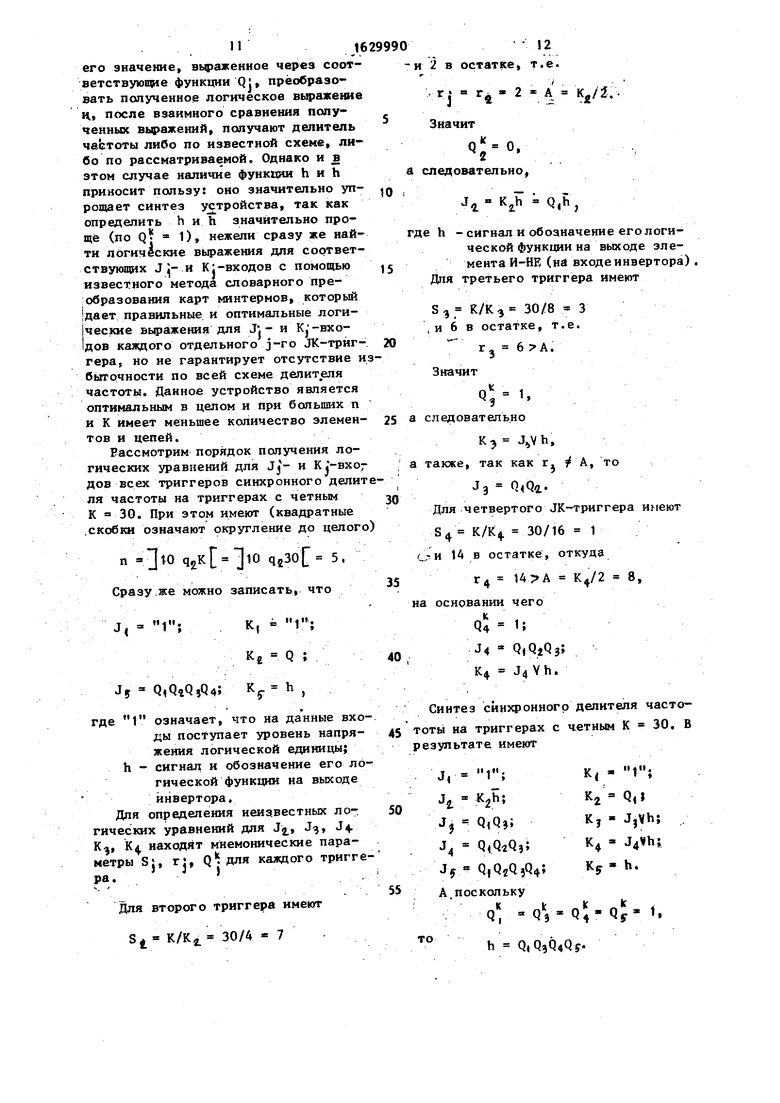

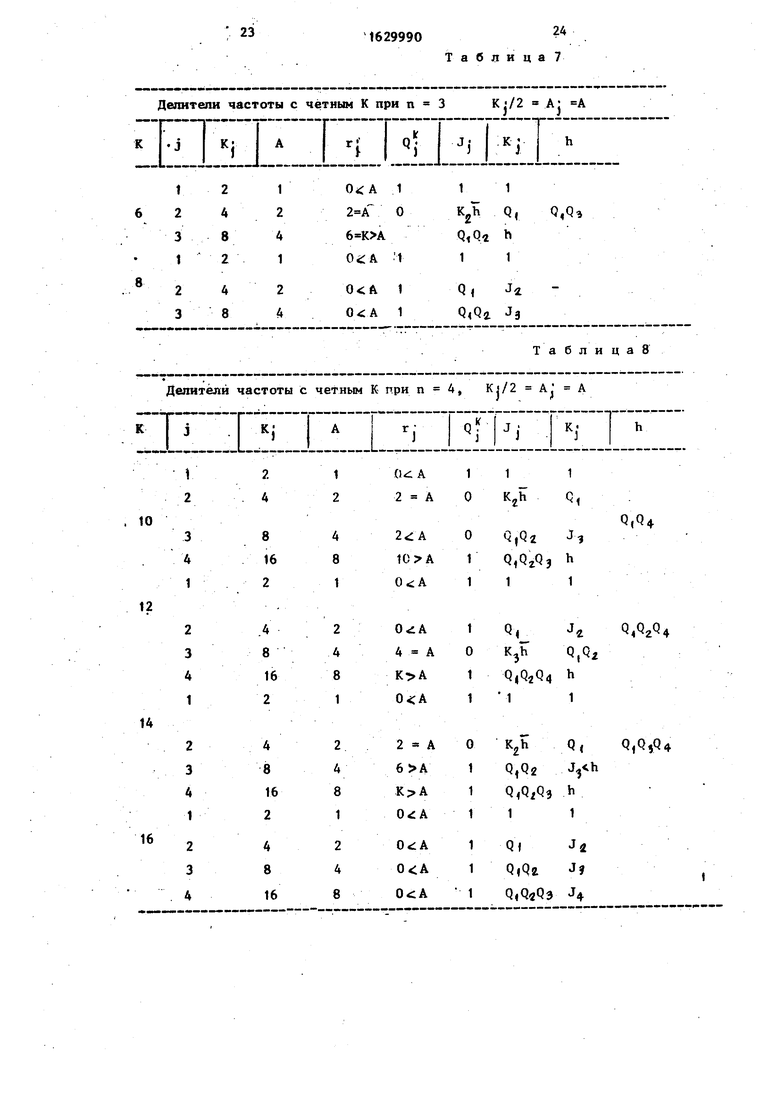

В табл.2 приведены перечисленные параметры для всех триггеров при п 3.

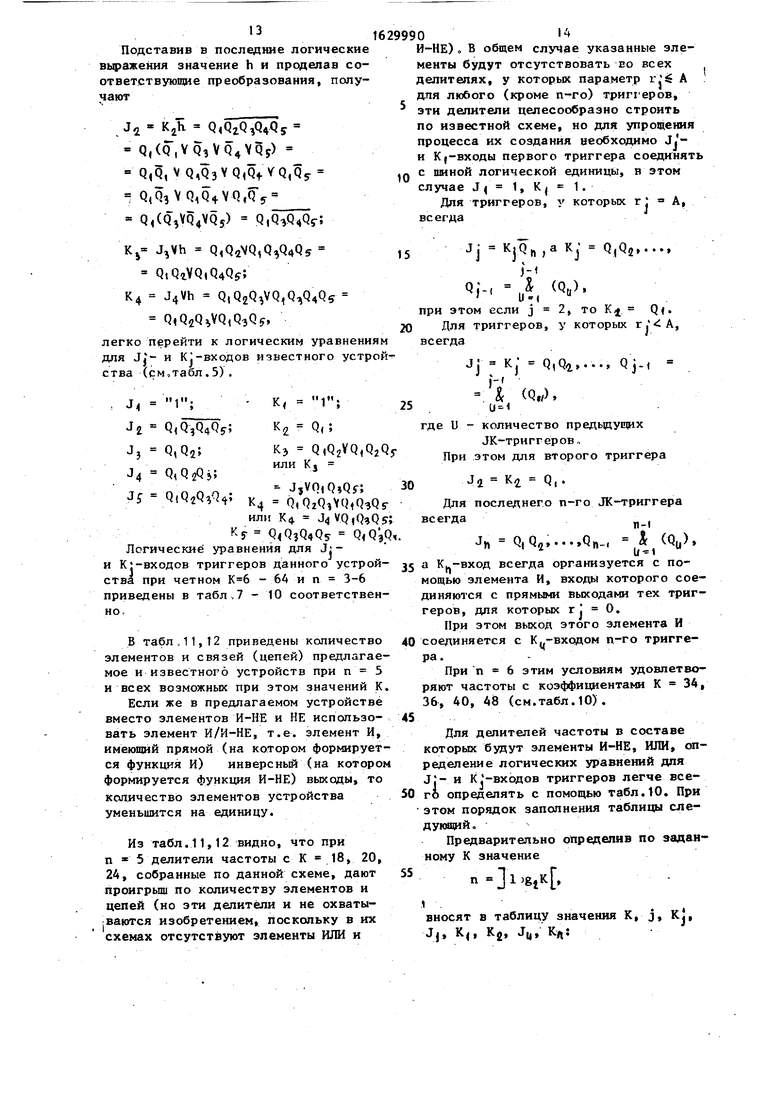

В табл.3 приведены значения J:- и Kj-входов триггеров при . В .табл.4 приведены значения

5

частного Sj деления К на ном К и п 4 .

К/К К

и остатка г j от

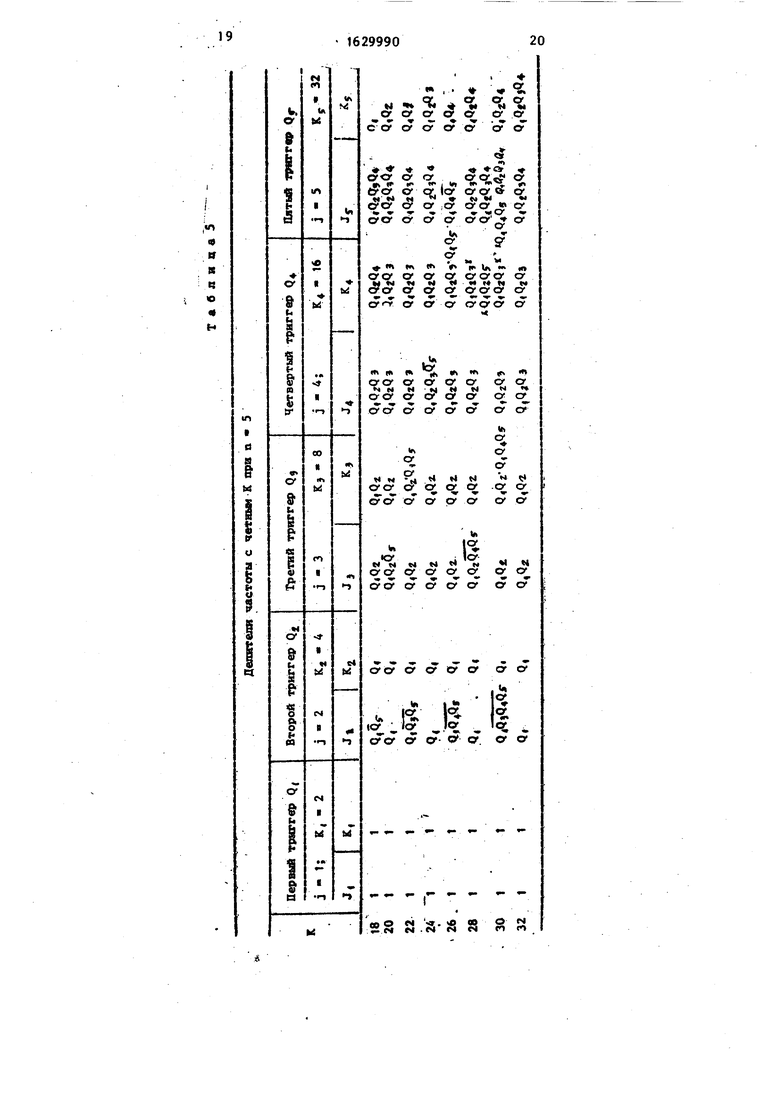

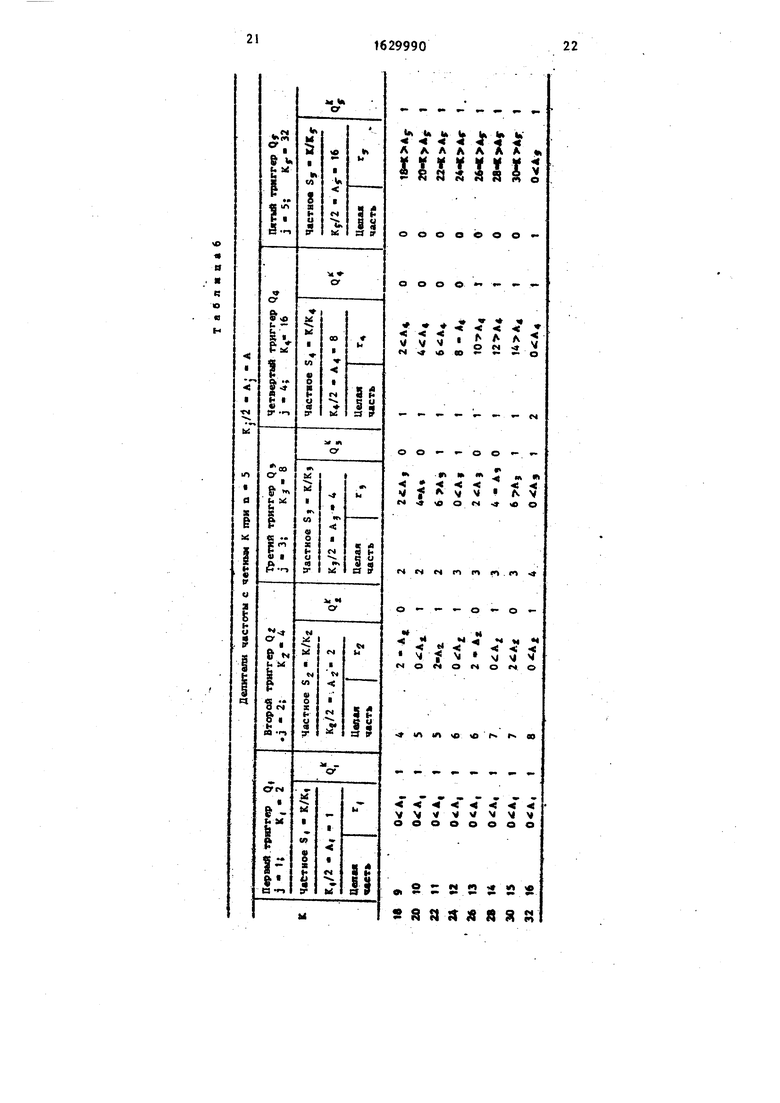

, а также Q1: при четВ табл.5 приведены логические уравнения для J. - и К--входов триггеров синхронных делителей частоты

с четным К 18-32 при п 5, полученных с помощью метода словарного преобразования карт минтермов, а в табл.6 даны значения параметров Sj, г , Q для каждого j-ro триггера уст5 ройства.

Дальнейший анализ делителей частоты на JK-тригграх при увеличении п и соответственно К можно не проводить, ибо уже из имеющихся данных

о при п 3,4,5 легко увидеть недостатки известных делителей частоты на триггерах, полученных с помощью классического метода синтеза последо- вательностных цифровых автоматов - делителей частоты - метода словарного преобразования карт минтермов, который дает правильные (без избыточности) результаты для каждого отдельного JK-триггера делителя частоты, но в общем для всего устройства он не гарантирует отсутствие иэбыточностис при больших значениях п и К.

0

По данным табл.1,3,5 легко выявить общие признаки рассматриваемых делителей частоты с четным К, которые не зависят от значений п и К:

при любых п и четных К J(- и входы первого триггера соединены с шиной логической единицы, т.е.

50

п 1 и

1

V - 1.

к. ( - i ;

К.-вход второго триггера во всех делителях частоты с четным К всегда соединен с прямым выходом первого триггера, т.е.

К4-

J.-нходы последнего n-го триггера во всех случаях соединен через собственный элемент- И с прямыми выходами всех предыдущих (у которых j мерьте п) триггеров

где .п - условный порядковьй номер тех триггеров, для которых

Р

1;

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

Изобретение относится к импульсной технике и может использоваться при построении хронизаторов, цифровых синтезаторов частоты и электромузыкальных инструментов. Цель изобретения - упрощение устройства достигается введением инвертора и организацией новых функциональных связей Приведен пример выполнения устройства с коэффициентом деления 60, Рассмотрены примеры синтеза устройств с различными коэффициентами деления,, 1 ил., 12 табл.

Jn Q f «Qn-«

Дополнительные общие признаки вы являются из сопоставления данных табл.1 и 2, 3 и 4, 5 и 6 по значениям исходных величин К, j, К j и рассчитанных по ним Аj A Kj/2, t j (или по значению Q:): при остатке гл 0 от деления К на К для второго триггера вход его соединен с собственным

|К -входом

при остатке г. Ф А для j-ro тригге ра Jj-вход его соединен с выходом собственного элемента И, входы ко торого соединены соответственно с прямыми выходами всех предыдущих (имеющих меньшее значение j) триггеров

J

Q

QIJ-I

при г| А для j-ro триггера Kj- вход его соединен с выходом соб ствённого элемента И, входы которого соединены соответственно с прямыми выходами всех, предыдущих триггеров

Ki

QI

QH;

при гj А для j-ro триггера Kf-вход его соединен с сдбствен ным J -зходом

Ki

Jj;

при этом у последнего n-го триггера К -вход соединен с выходом собственного элемента И, входы которого соединены с прямыми выходами тех триггеров, для которых Q 1, исключая n-й триггере Математически это можно зйписать следующим образом:

«-«и

8с

(Qp)m- )

10

15

25

30

m - количество триггеров,

для которых QJ 1, включая и n-й триггер; индекс (ш-1) при (Qp) указывает на исключение из рассмотрения именно n-го триггера;

f(n-m)- количестве триггеров, для

которых Q1- 0. Для р-го триггера остаток rj г„ 0 или rj . При для 20 j-ro триггера Кj-вход его соединен с выходом собственного элемента ИЛИ, первый вход которого соединен с собственным J. -входом, второй - с выходом (т-1) входового элемента И, входы

которого соединены соответственное выходами тех триггеров, для которых Q-K 1, исключая j-триггер Ji .w

где i. ф j - условный порядковый номер тех триггеров, для которых Qi 1, индекс (га-1) при Q указывает

на исключение из рассмотрения именно j-ro триггера

Для t-ro триггера остаток г, г 0 или г J г A J при г { А для j-ro триггера J:-вход его соединен с выходом собственного двухвходово- го элемента И, первый вход которого соединен с собственным Kl-входом, а второй - с выходом элемента И-НЕ, входы которого соединены соответственно с прямыми выходами тех триггеров, для которых

J

)

исключая те из указанных триггеров, прямые выходы которых соединены через собственный элемент И с К -входом

n-6-m л

.«фш . .

Вместо элемента-И-НЕ может быть использован элемент ИЛИ. В этом.случае входы элемента ИЛИ соединяются с инверсными выходами тех же триггеров

П-Е-

J - К , - V

J m-e

где q j - условный порядковый номер тех триггеров, для которых

(Qjm

)

л 1 Ч

m | - количество переменных Q вошедших в логическое выражение для К,.

Для q-ro триггера остаток г, г, 0 или г г а А .

При четном К первый () и последний (j n) триггеры, независимо от значений n и К, будут иметь Q 1 и Qц 1 соответственно.

Из приведенного перечня элементов и связей и данных табл.1,3,5 видна сложность известного устройства при больших значениях гг и К.

Рассмотрим на примере делителя частоты с К 26, каким образом можно прийти к упрощению устройства. Для этого делителя (см,табл 5)

К 26; n 5;

2 Qh(Q4- -

Т - 1.

J j - 1 ,

J3 Q,Qa; J4 Q1QiQ3 K4 K2 Q(;

fcg QiQz; ч QiQaQj-Q,;

5 Q QtQ;Q4i Kf - QiQ4- ,

В триггере имеется внутренняя связь через элемент И прямого выхода Q триггера с К-входом, а инверсного выхода Q - аналогичная связь с J-входом. Поэтому ничего не изменится в работе синхронного делителя частоты на триггерах, если в логическом выражении для К. -входов j-ro триггера введем собственную функцию Qj, а для J. -входов инверсию Qj -Q j. Проделаем это только для KI-входов но не всех, а лишь для К и Ку, поскольку именно в этом случае получается упрощение устройства.

Тогда вместо

4 QiQeQi QiQs КУ Q,Q4

имеют

к - (Q4Q5;

KS- Q,Q4Q5 Получают общий член

hl

4 h

что приводит к упрощению устройства, так как вместо двух элементов И с 20 логическими функциями на выходах

QiQs

соответственно, можно использовать один элемент И с выходной функцией

h . Тогда К,

к,

-J4 Vh;

-h .

Общим для Qj, входящих в логическое выражение для h, является то,что для них

Q -..

ИЛИ Г

О и г j А .

Именно из этого и определяется содержание выражения для hi Для общности можно вместо

40

J2

принять

J-L Qih

ибо эти выражения равнозначны. Действительно:

- Q,h Q, Q(Q,VQVVQP

,Q«r

Q,(Q4VQ5) Q,Но это приводит к упрощению лишь при больших К внутри данного п. Например, при п , К 20,- К 24 упрощения не получается. Поэтому при малых К внутЈИ данного n необходимо вместо h и h. подставить

1116

его значение, выраженное через соответствующие функции Q|, преобразовать полученное логическое вьфажение К после взаимного сравнения полученных выражений, получают делитель частоты либо по известной схеме, либо по рассматриваемой. Однако и в этом случае наличие функции h и h приносит пользу: оно значительно упрощает синтез устройства, так как определить h и li значительно проще (по Q 1), нежели сразу же найти логические выражения для соответствующих J f- и К:-входов с помощью известного метода словарного преобразования карт минтермов, который 1дает правильные и оптимальные логические выражения для J . - и К: -входов каждого отдельного j-ro JK-триг- гера, но не гарантирует отсутствие ибыточности по всей схеме делителя частоты. Данное устройство является оптимальным в целом и при больших п и К имеет меньшее количество элементов и цепей.

Рассмотрим порядок получения логических уравнений для JJ- и К. -вхо дов всех триггеров синхронного делит

Г;

ля частоты на триггерах с четным К 30. При этом имеют (квадратные скобки означают округление до целого

n qc3o 5, Сразу же можно записать, что

К, - Ке « Q ;

Jj Q QtQsQ4i Kf h ,

где 1 означает, что на данные входы поступает уровень напряжения логической единицы; h - сигнал и обозначение его логической функции на выходе инвертора.

Для определения неизвестных логических уравнений для J, J, J+ K.J, К4. находят мнемонические параметры Si, г , Q для каждого триггера,

I

Для второго триггера имеют St K/Kfc 30/4 7

2 в остатке, rj- rf- 2 Значит

12

т.е.

V2

;«.

а следовательно,

J где h

Kzh

Q.h,

- сигнал и обозначение его логической функции на выходе элемента И-НЕ (ни входе инвертора) . Для третьего триггера имеют

К/К

° 1 )

и 6 в остатке,

30/8 3 т.е.

6 А.

Значит

ч.

25 а следовательно

К

V/h,

а также, так как г, j А, то

J3 - . Для четвертого JK-триггера имеют S4 К/К 4. 30/16 1 с,-и 14 в остатке, откуда

Г4 К4/2 - 8,

на основании чего

q$ - 1;

J« - QjQiQjJ

К4 J4 Vh.

Синтез синхронного делителя частототы на триггерах с четным К 30. В результате имени50

55

то

h QtQ3Q4Qy

13

Подставив в последние логические выражения значение h и проделав соответствующие преобразования, получают

Ju - K2h Q,QZQ,Q4Q5

-Q(Q,VQ,VQ4VQF) Q«Q, VQ,Q3YQ,Qf YQ,Q5- QtQ3VQ,,(ry

-Q,(Q,VQ4VQ5) Q,Q3Q4Qs-;

К,

J,Vh

.s- «,, - Q,,Q,Q4Qs

QtQiVQ(

К4 J4Vh Q,Q2Q3VQ,Q,Q4Q5 ,Q3Qf,

легко перейти к логическим уравнениям для Jj- и Кj-входов известного устройства (см,табл.5) .

Т - 1

J4

11 Г ;

к2 Q,;

Кз QfQzVQiQzQ

ИЛИ Kj

JjVQjChQj-;

jЈ - , J3 Q,Q2 J4 QiQeQ ;

Jf-Q. . или K4 J4 VQ,Q,Q5;

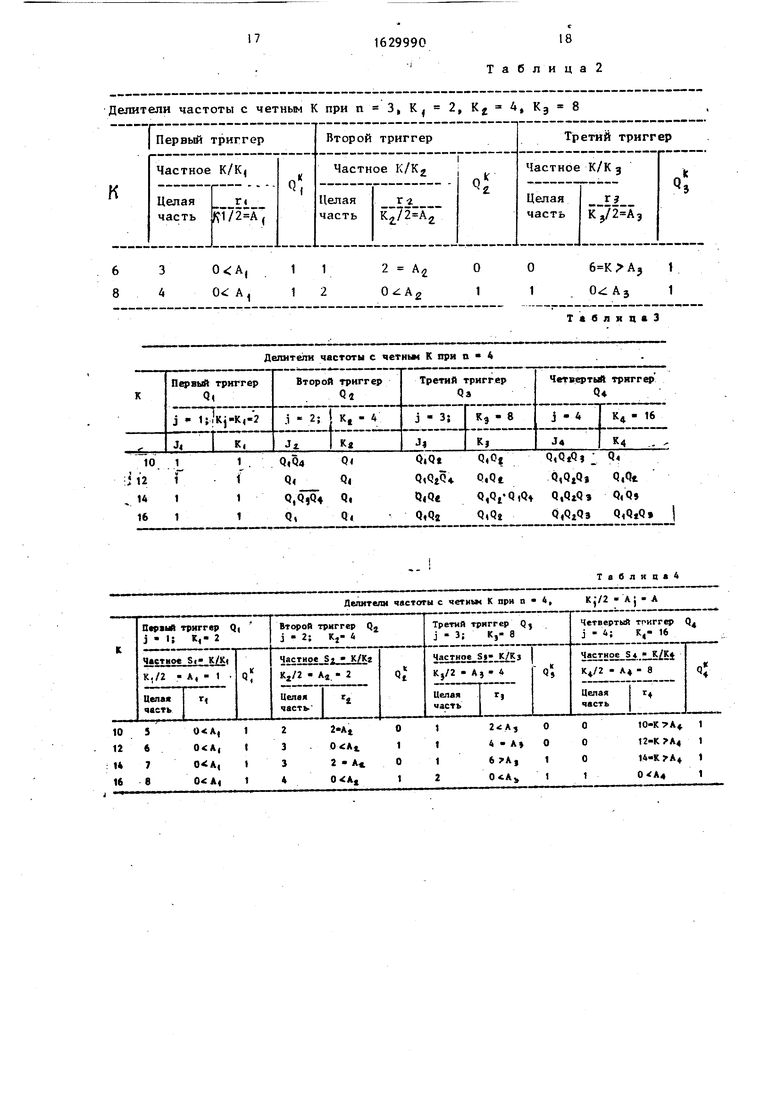

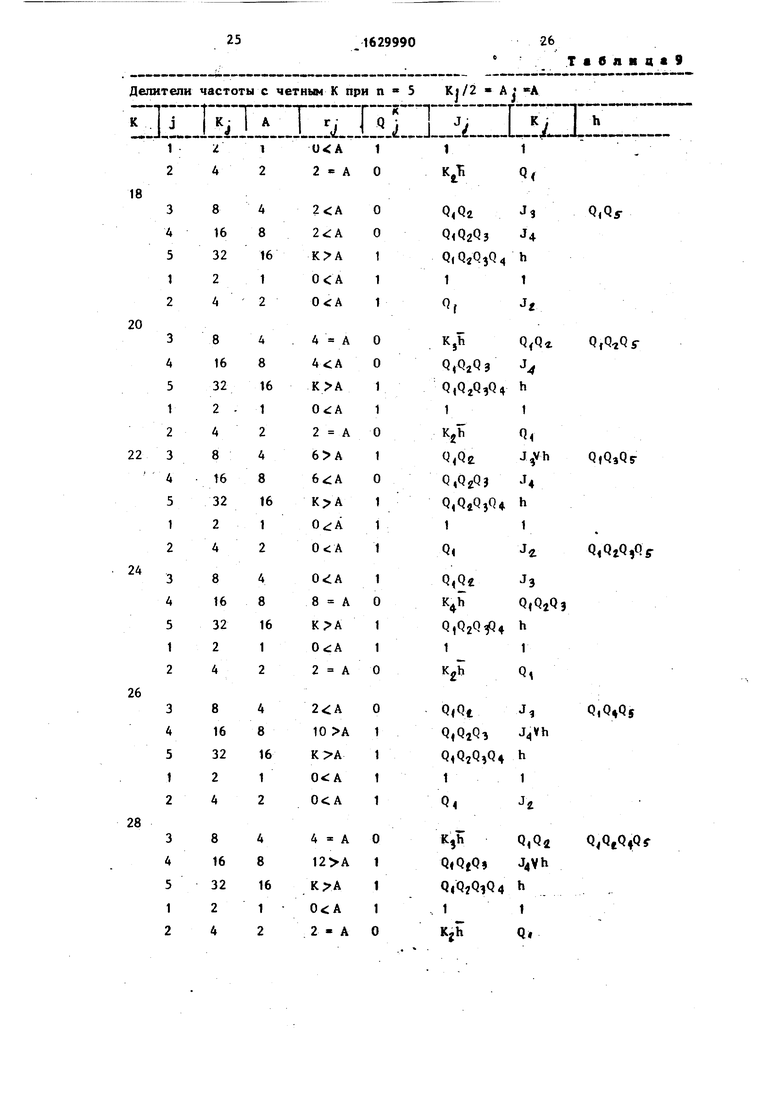

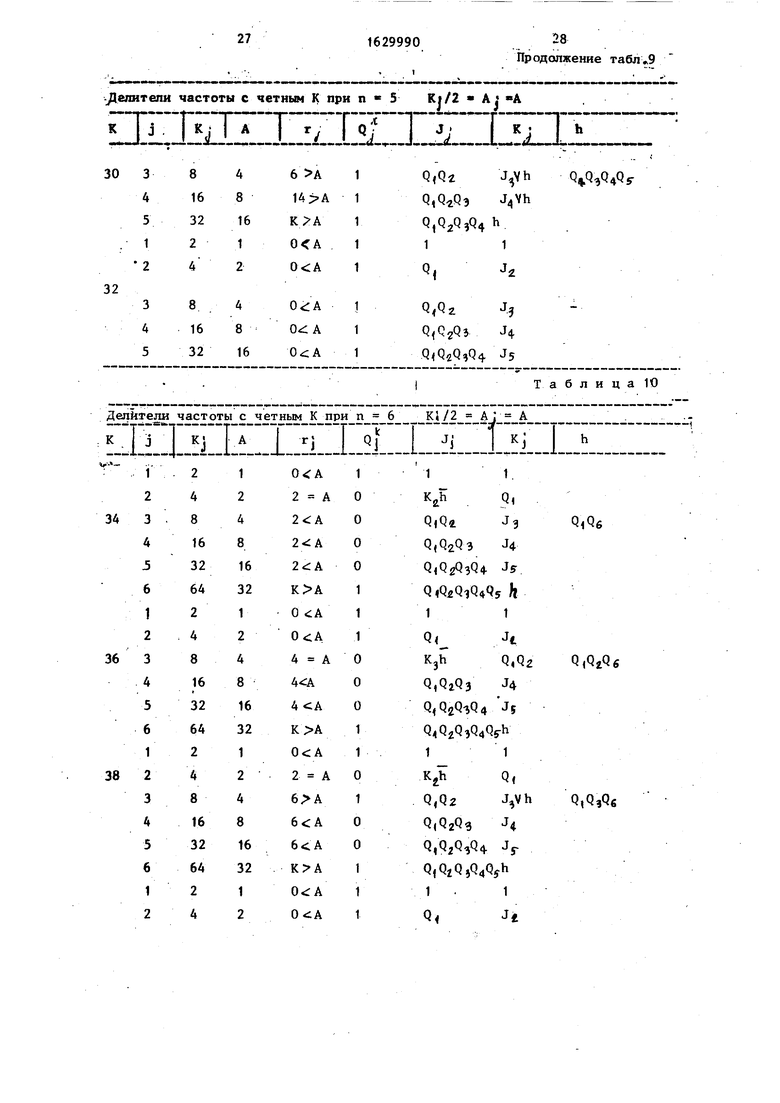

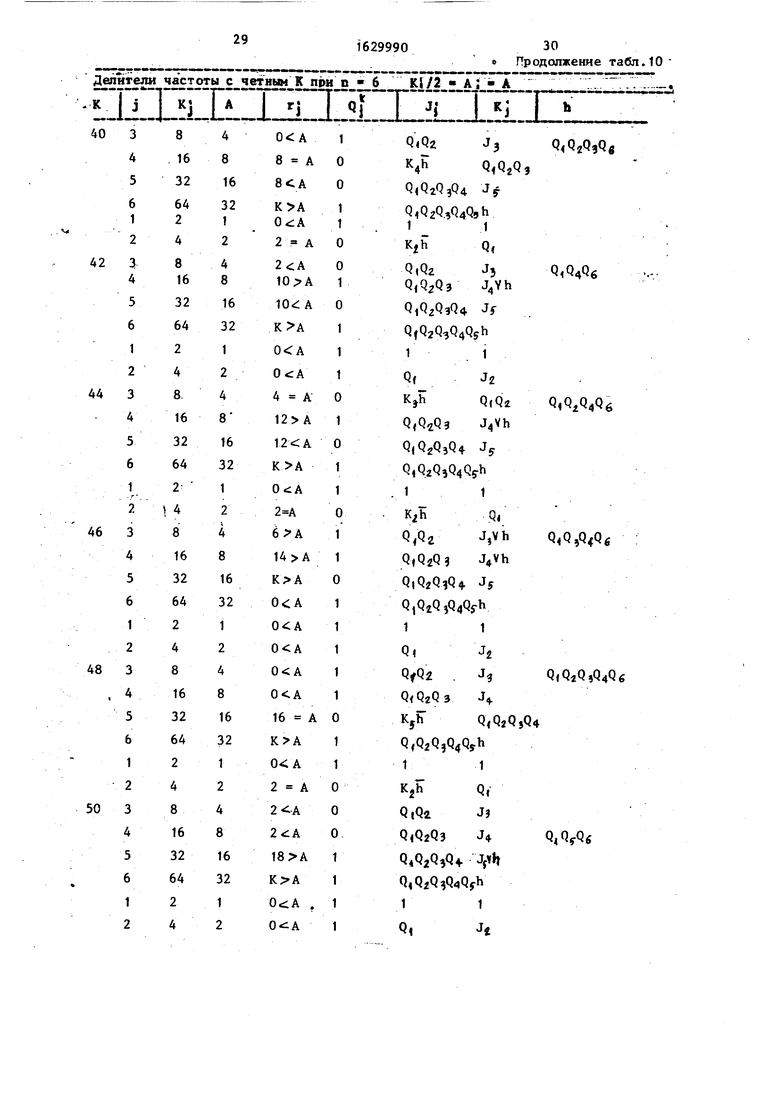

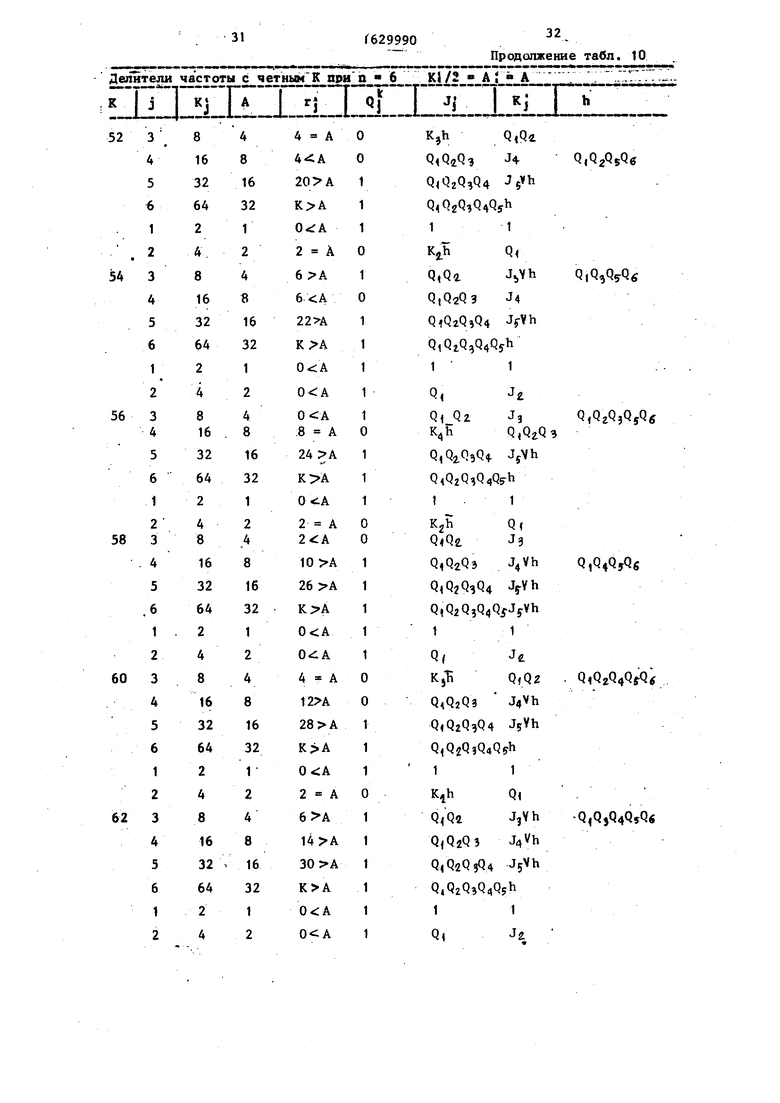

КУ Q3Q4Q5 Q«QiQ Логические уравнения для J:- и Кj-входов триггеров данного устрой- ства при четном - 64 и п 3-6 приведены в табл,7 - 10 соответственно

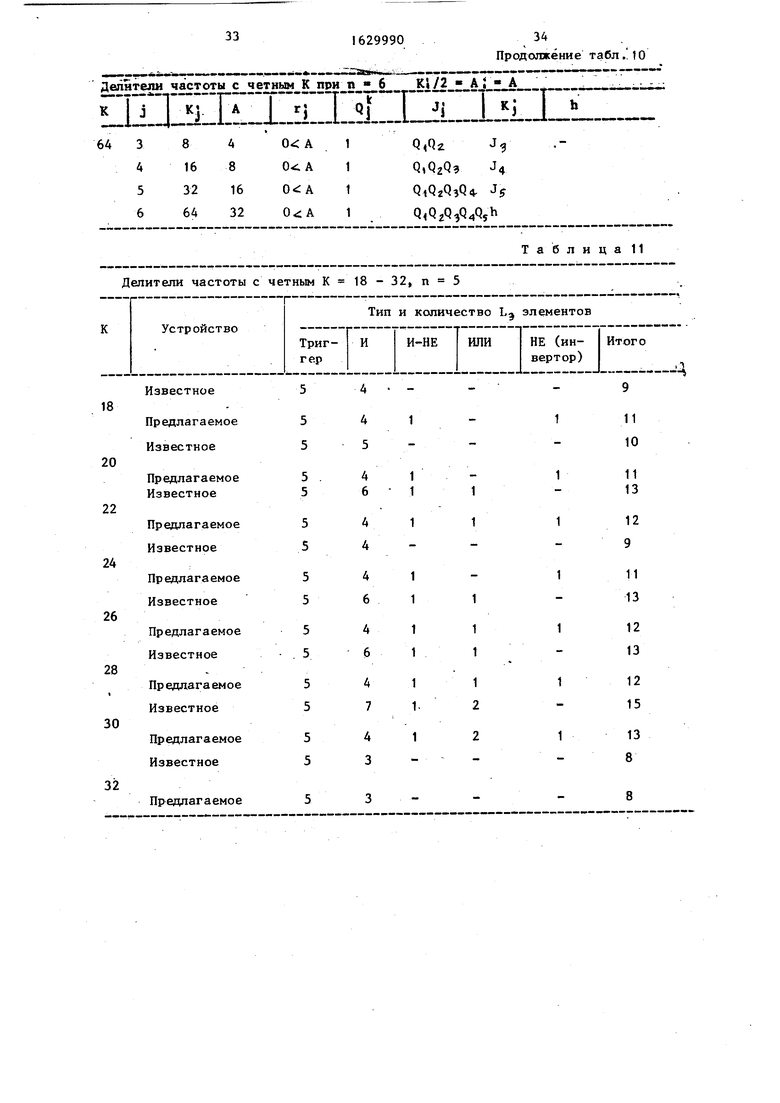

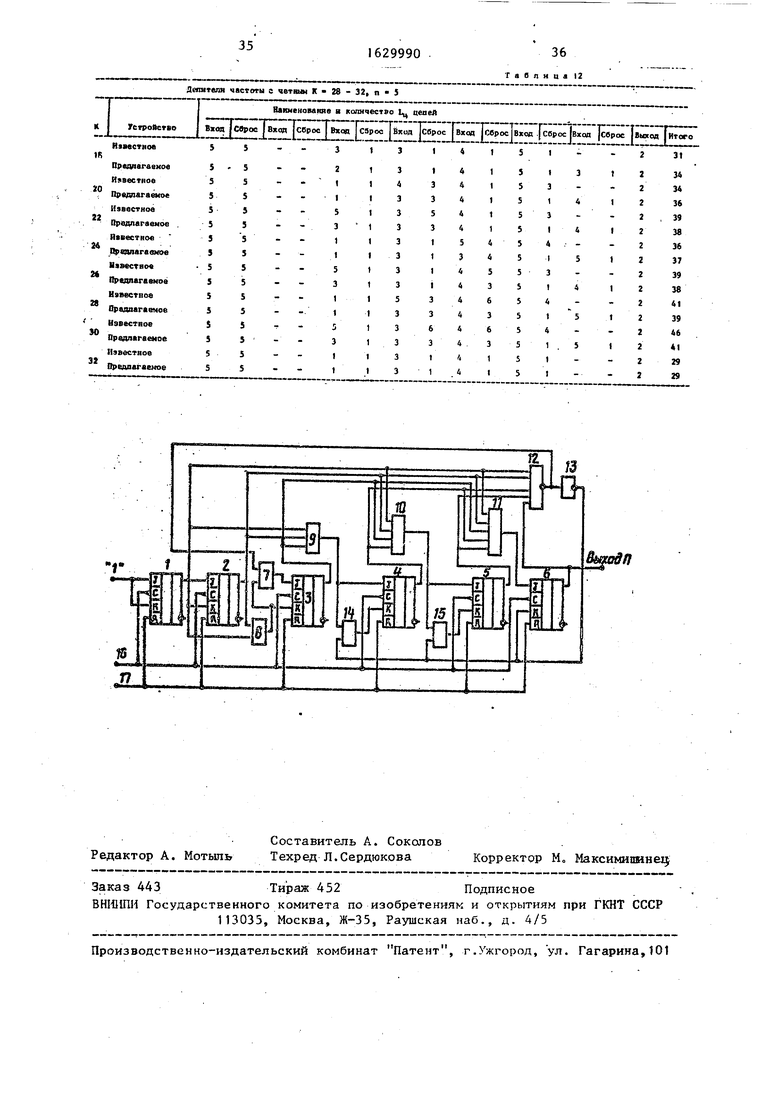

В табл 11,12 приведены количество элементов и связей (цепей) предлагаемое и известного устройств при п 5 и всех возможных при этом значений К.

Если же в предлагаемом устройстве вместо элементов И-НЕ и НЕ использо- вать элемент И/И-НЕ, т.е. элемент И, имеющий прямой (на котором формируется функция И) инверсный (на котором формируется функция И-НЕ) выходы, то количество элементов устройства

уменьшится на единицу.

Из табл.11,12 видно, что при п 5 делители частоты с К 18, 20, 24, собранные по данной схеме, дают проигрыш по количеству элементов и цепей (но эти делители и не охватываются изобретением, поскольку в их схемах отсутствуют элементы ИЛИ и

1629990

14

И-НЕ). В общем случае указанные элементы будут отсутствовать во всех делителях, у которых параметр rjЈ A дпя любого (кроме n-го) триггеров, эти делители целесообразно строить по известной схеме, но для упрощения процесса их создания необходимо J/- и К|-входы первого триггера соединять с шиной логической единицы, в этом

случае J ( 1, К

Для триггеров, у которых г

всегда

А,

Jj )a Kj Q;-, - V (QB),

при этом если j 2, то К Q.

Для триггеров, у которых г., всегда

Qi-t

j

5

0

0

5 0

5

Jj - Kj Q,Qa,..

& QW,

где И - количество предыдущих

ЛК-триггеров„ При этом для второго триггера

J2 К2 Q,.

Для последнего n-го ЛК-триггера всегдап(

Jh Q, Q4,...,Qn,

а К -вход всегда организуется с помощью элемента И, входы которого соединяются с прямыми выходами тех триггеров, для которых г . - О.

При этом выход этого элемента И соединяется с Кц-входом n-го триггера.

При п 6 этим условиям удовлетворяют частоты с коэффициентами К 34, 36, 40, 48 (см.табл.10).

Для делителей частоты в составе которых будут элементы И-НЕ, ИЛИ, определение логических уравнений для Jj- и К. -входов триггеров легче всего определять с помощью табл.10. При этом порядок заполнения таблицы следующий.

Предварительно определив по заданному К значение

,

1

вносят в таблицу значения К, j, Kl, Jj, К, Kj, Ju, Кд:

К

1й; К,

. I (

К„-Ь,

Рассчитывают и вносят в таблицу значения г} и А Г в А для всех j

J

J К SjKJ;

К-/2.

Определяют и вносят в таблицу соотшения между т; и А. По соотношению

г) определяют

К т

2

жду rj и А блицу значения Q.,

И -Ъ 4 Кц-|- Если г; 0(rl j A),

и вносят в

5 f

к

то Q

М

J

Jj

j

если г

J

J если

„I «ь

(rj # А), „,

то

Qj

1

. О

1

Ki- -,ГР

A(rj

# А), то Q 1

Jj

j-i J J Ч u&( Qt,, a Kj KjKh;

то Qj 0

и

J

a

если rj A,

- .

Определяют h как конъюкцию t(r- 0

Jj

Kjh

Qj, для которых Q 1 t(r О или r A

JI -J

и заносят значение в таблицу.

На этом заканчивается процесс составления схемы требуемого синхронного делителя частоты с четным коэффициентом деления.

Формула изобретени

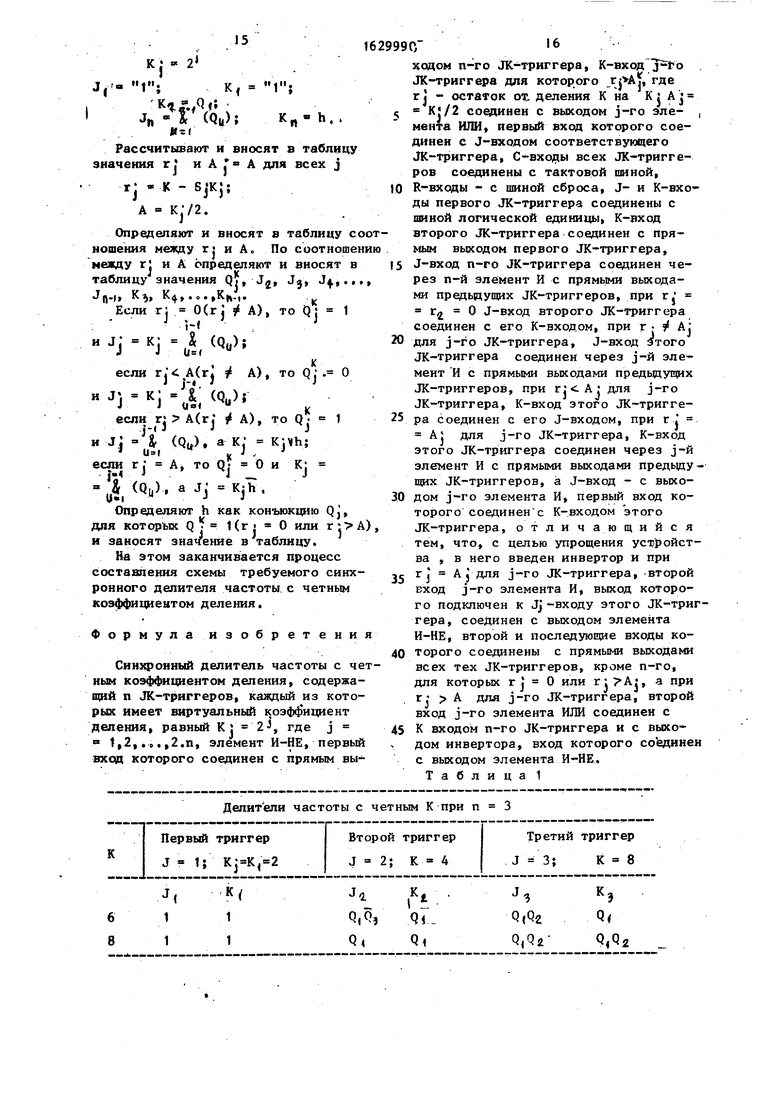

Синхронный делитель частоты с ченым коэффициентом деления, содержащий п JK-триггеров, каждый из которых имеет виртуальный коэффициент деления, равный К: 2J, где j t,2,.0.,2.n, элемент И-НЕ, первый вход которого соединен с прямым выДелители частоты с четным К при п 3

ходом п-го JK-триггера, К-вход JK-триггера для которого где rj - остаток оъ деления К на К: Aj К /2 соединен с выходом j-ro эле- , мента ИЛИ, первый вход которого соединен с J-входом соответствующего JK-триггера, С-входы всех JK-триггеров соединены с тактовой шиной, R-входы - с шиной сброса, J- и К-вхо- ды первого JK-триггера соединены с шиной логической единицы, К-вход второго JK-триггера соединен с прямым выходом первого JK-триггера, J-вход п-го JK-триггера соединен через n-й элемент И с прямыми выходами предыдущих JK-триггеров, при г} г 0 J-вход второго JK-триггера соединен с его К-входом, при г У Aj для j-ro JK-триггера, J-вход этого JK-триггера соединен через j-й элемент И с прямыми выходами предыдущих JK-триггеров, при г:сА: для j-ro JK-триггера, К-вход этого JK-тригге5 ра соединен с его J-входом, при г

0

5

0

5

1

А| для j-ro JK-триггера, К-вход этого JK-триггера соединен через j-й элемент И с прямыми выходами предьщу - ших JK-триггеров, а J-вход - с выходом j-ro элемента И, первый вход которого соединен с К-входом этого JK-триггера, отличающийся тем, что, с целью упрощения устройства , в него введен инвертор и при г j Aj для j-ro JK-триггера, второй вход j-ro элемента И, выход которого подключен к JJ-входу этого JK-триггера, соединен с выходом элемента И-НЕ, второй и последующие входы которого соединены с прямыми выходами всех тех JK-триггеров, кроме п-го, для которых г } 0 или г; Aj, а при

r j A

и или , для j-ro JK-триггера, второй

вход j-ro элемента ИЛИ соединен с К входом п-го JK-триггера и с выходом инвертора, вход которого соединен с выходом элемента И-НЕ. Таблица 1

Та6лица2

Делители частоты с четным К при п 5

К}-/2 - Aj- А

23

Делители частоты с четным К при п 4,

I

2

1 2

3 4 1

2 3

4

1

2 3 4 1

2 3 4

2 4

8

16

2

4 8 16 2

4 8 16 2

4 8 16

1 2

4 8 1

2 4 8 1

2 4 8 1

2 4 8

1629990

24 Таблица

Таблицав

1 О

О

1

1

1 о 1 1

о 1 1 1

1 1

кгь

1

s

QfQz Ji Q,QZQ3 h 11

Q,Q4

L

г V

W4

Q.Q

Q4Q2Q4 h 11

K2h

Q Q,Q2

h 11

Q(Q,Q4

Qf Q«Qz

J2 J

1 Q«Q2Qa J4

Т«бяиц 9

31

Г629990

32 Продолжение табл. 10

Делители частоты с четным К 18-32,

Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое Известное

Предлагаемое

11 10

11 13

12 9

11 13

12 13

12 15

13 8

8

| Синхронный делитель частоты | 1986 |

|

SU1385291A1 |

| Логические,цепи в цифровой технике | |||

| /Под ред | |||

| Б,А, Калабекова, - М.: Связь, 1977, с | |||

| Нагревательный прибор для центрального отопления | 1920 |

|

SU244A1 |

Авторы

Даты

1991-02-23—Публикация

1987-04-07—Подача