1

Изобретение относится к вычислительной технике и может быть использовано в динамических оперативных запоминающих устройствах (ДОЗУ).

Цель изобретения - повышение быстродействия устройства.

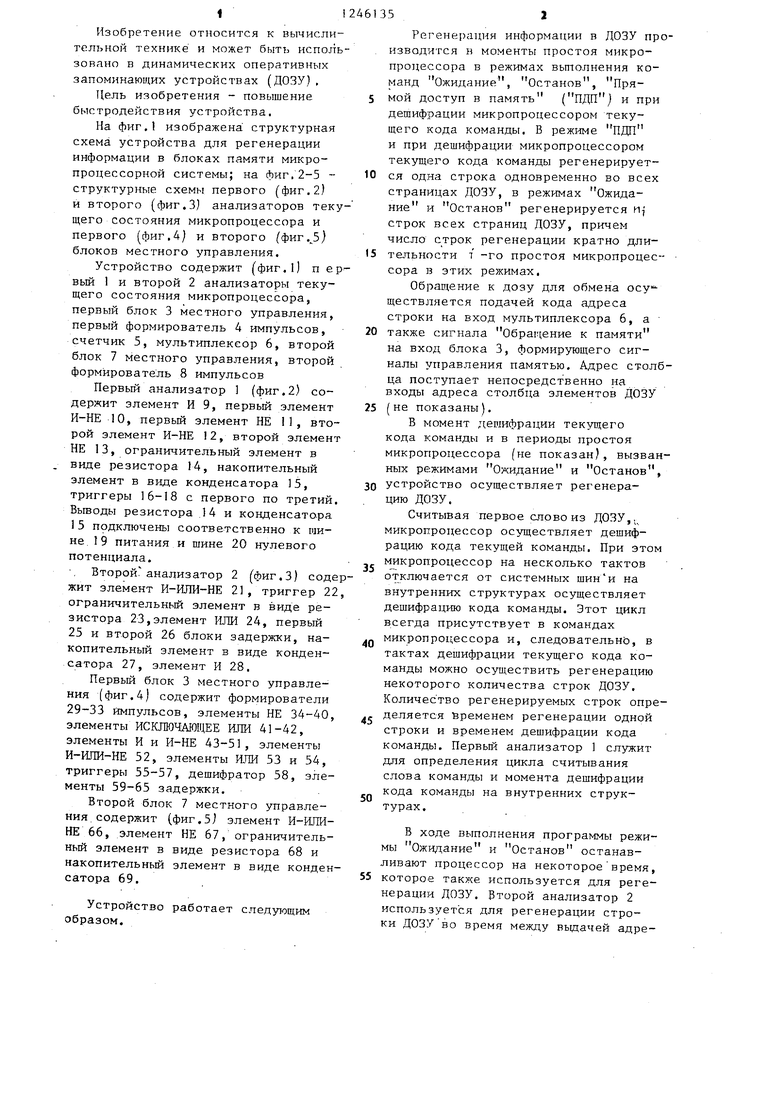

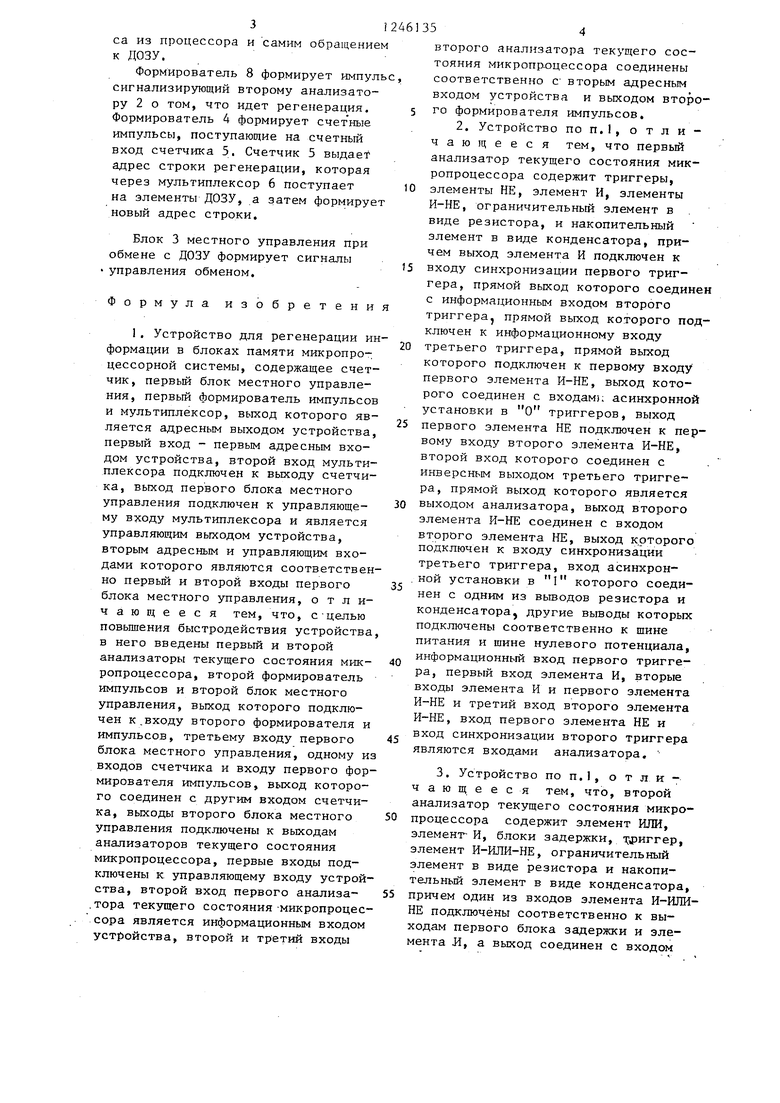

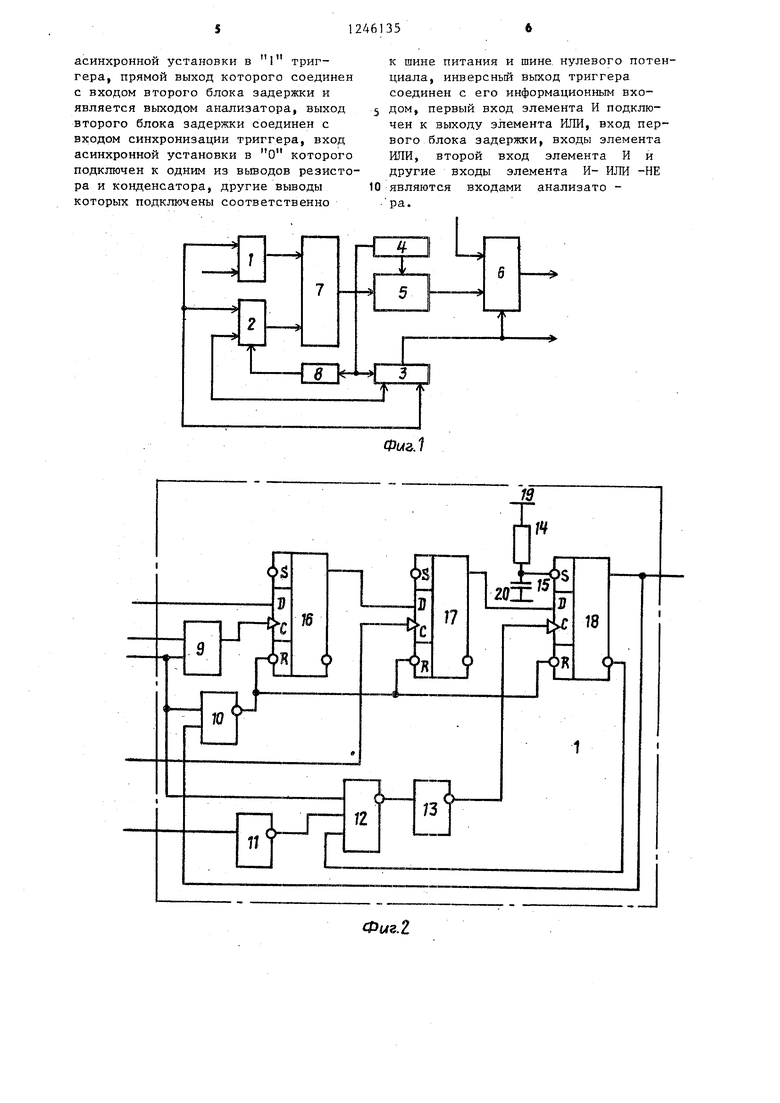

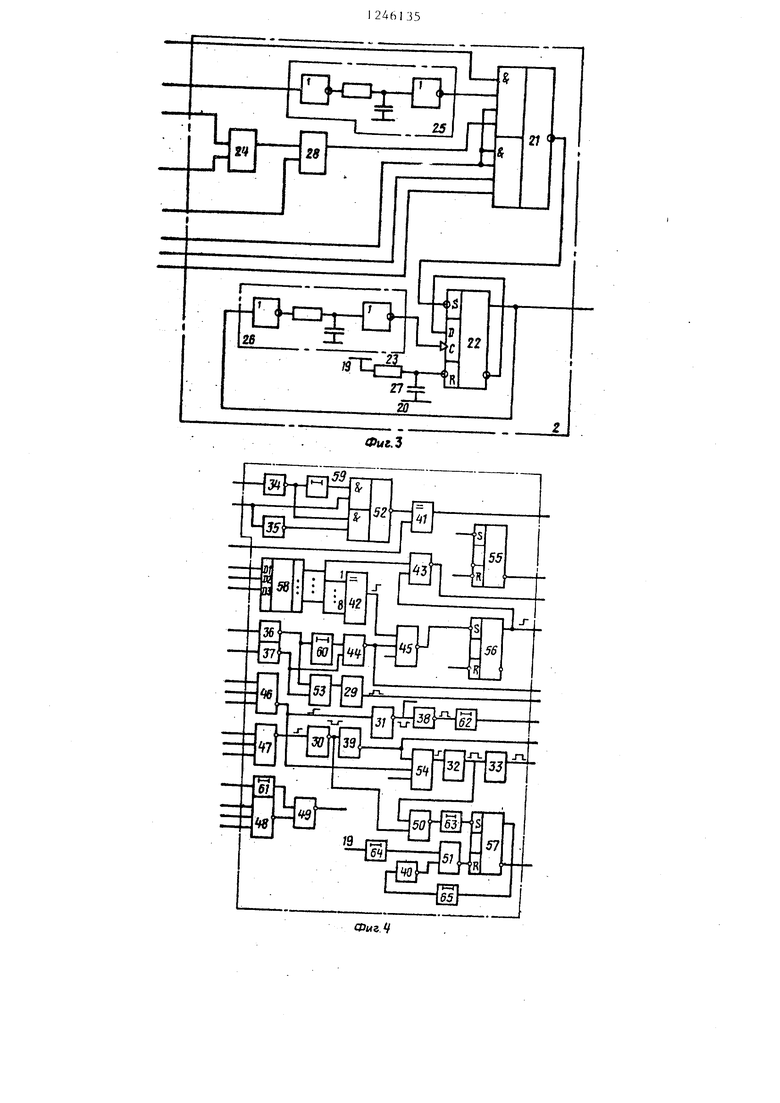

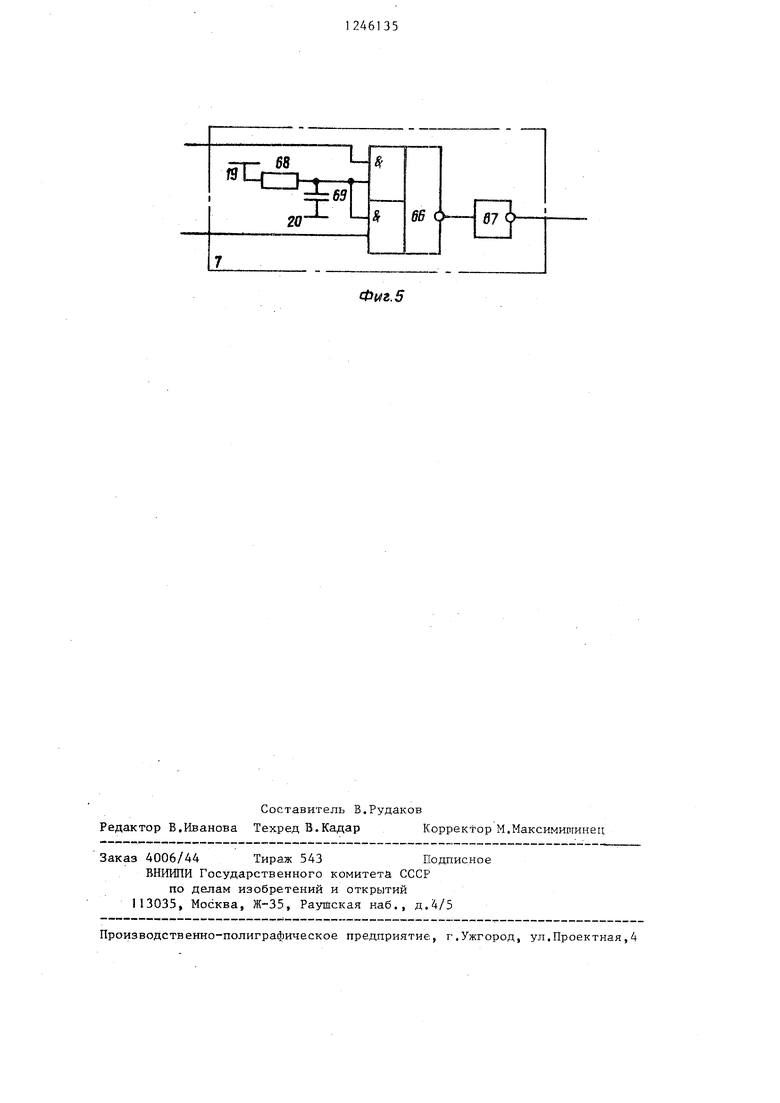

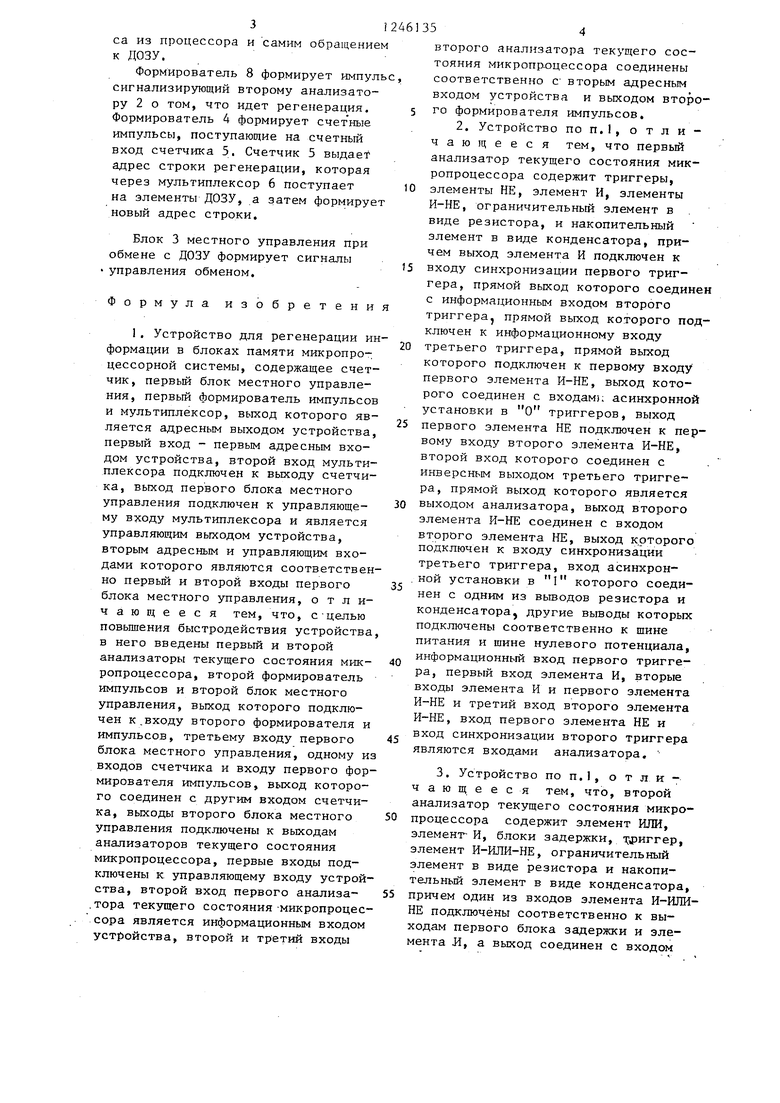

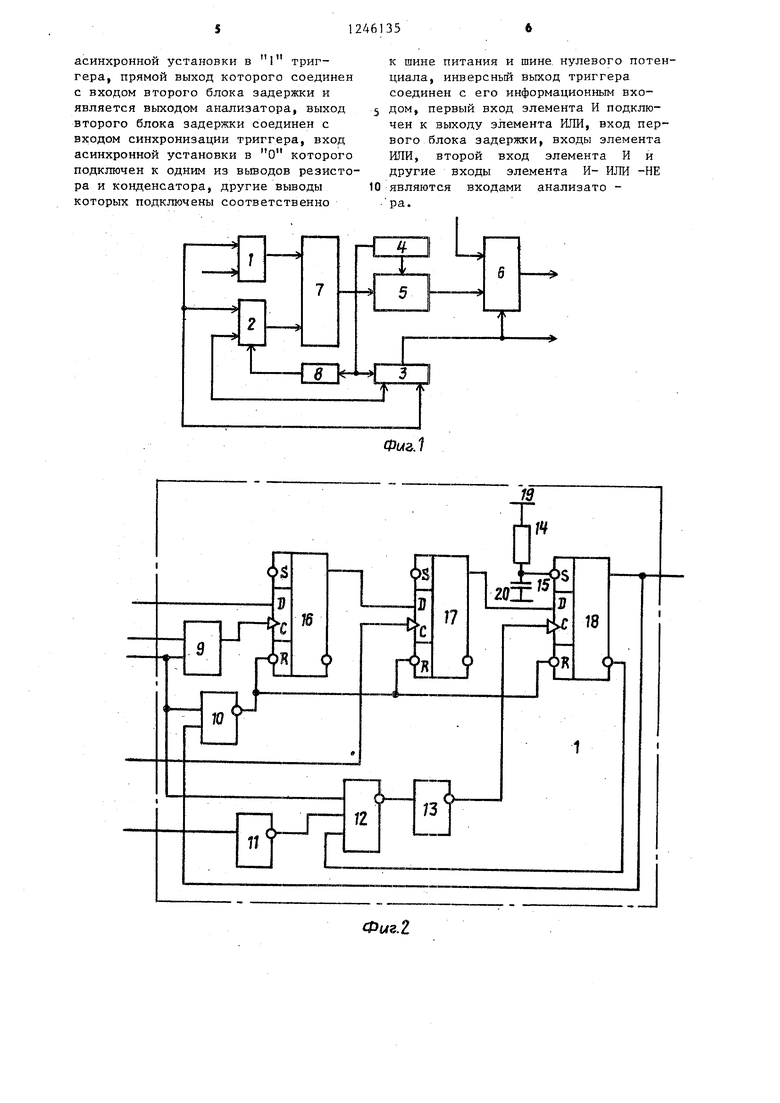

На фиг. изображена структурная схема устройства для регенерации информации в блоках памяти микропроцессорной системы; на фиг.2-5 - структурные схемы первого (фиг.2) и второго (фиг.З) анализаторов текущего состояния микропроцессора и первого (фиг.4) и второго (фиг.5) блоков местного управления.

Устройство содержит (фиг.1) п ер вый 1 и второй 2 анализаторы текущего состояния микропроцессора, первый блок 3 местного управления, первый формирователь 4 импульсов, счетчик 5, мультиплексор 6, второй блок 7 местного управления, второй формирователь 8 импульсов

Первый анализатор 1 (фиг.2) содержит элемент И 9, первый элемент И-НЕ 10, первый элемент НЕ II, второй элемент И-НЕ 12, второй элемент НЕ 13, ограничительный элемент в виде резистора 14, накопительный элемент в виде конденсатора 15, триггеры 16-18 с первого по третий Вьгооды резистора 14 и конденсатора 15 подключены соответственно к шине 1 9 питания и шине 20 нулевого потенциала.

Второй анализатор 2 (фиг.З) содежит элемент И-ИЛИ-НЕ 21, триггер 22 ограничительньй элемент в виде резистора 23,элемент ИЛИ 24, первый 25 и второй 26 блоки задержки, накопительный элемент в виде конденсатора 27, элемент И 28.

Первый блок 3 местного управления (фиг.4) содержит формирователи 29-33 импульсов, элементы НЕ 34-40 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 41-42, элементы И и И-НЕ 43-51, элементы И-ИЛИ-НЕ 52, элементы ИЛИ 53 и 54, триггеры 55-57, дешифратор 58, элементы 59-65 задержки.

Второй блок 7 местного управле- ния содержит (фиг.5 элемент И-ИЛИ- НЕ 66, .элемент НЕ 67, ограничительный элемент в виде резистора 68 и накопительный элемент в виде конденсатора 69.

Устройство работает следутощим образом.

461352

Регенерация информации в ДОЗУ производится в моменты простоя микропроцессора в режимах вьтолнения команд Ожидание, Останов, Пря- 5 мой доступ в память (ПДП) и при дешифрации микропроцессором текущего кода команды. В режиме ПДД и при дешифрации микропроцессором текущего кода команды регенерирует- 10 ся одна строка одновременно во всех страницах ДОЗУ, в режимах Ожидание и

Останов регенерируется и,

строк всех страниц ДОЗУ, причем число строк регенерации кратно длительности 1 -го простоя микр.опроцес-- сора в этих режимах.

Обращение к дозу для обмена осуществляется подачей кода адреса строки на вход мультиплексора 6, а также сигнала Обращение к памяти на вход блока 3, формирующего сигналы З правления памятью. Адрес столбца поступает непосредственно на входы адреса столбца элементов ДОЗУ

(не показаны).

В момент депшфрации текущего кода команды и в периоды простоя микропроцессора (не показан), вызванных режимами Ожидание и Останов, устройство осуществляет регенерацию ДОЗУ.

Считывая первое слово из ДОЗУ,;, микропроцессор осуществляет дешифрацию кода текущей команды. При этом микропроцессор на несколько тактов отключается от системных шин и на внутренних структурах осуществляет дешифрацию кода команды. Этот цикл всегда присутствует в командах микропроцессора и, следовательнЬ, в тактах дешифрации текущего кода команды можно осуществить регенерацию некоторого количества строк ДОЗУ. Количество регенерируемых строк определяется бременем регенерации одной строки и временем дешифрации кода команды. Первый анализатор 1 служит для определения цикла считывания слова команды и момента дешифрации кода команды на внутренних структурах,

В ходе выполнения программы режимы Ож:идание и Останов останавливают процессор на некоторое время, которое также используется для регенерации ДОЗУ. Второй анализатор 2 используется для регенерации строки ДОЗУ во время между выдачей адре3J2461

са из процессора и самим обращением к ДОЗУ.

Формирователь 8 формирует импульс, сигнализирующий второму анализатору 2 о том, что идет регенерация. 5 Формирователь 4 формирует счетные импульсы, поступаюпше на счетный вход счетчика 5. Счетчик 5 выдает адрес строки регенерации, которая через мультиплексор 6 поступает ю на элементы ДОЗУ, а затем формирует новый адрес строки.

Блок 3 местного управления при обмене с ДОЗУ формирует сигналы управления обменом.

Формула изобретени

1, Устройство для регенерации информации в блоках памяти микропро-, цессорной системы, содержащее счетчик, первый блок местного управления, первый формирователь импульсов и мультиплексор, выход которого яв- ляется адресным выходом устройства, первый вход - первым адресным входом устройства, второй вход мультиплексора подключен к выходу счетчика, выход первого блока местного управления подключен к управляюще- му ВХОДУ мультиплексора и является управляющим выходом устройства, вторым адресным и управляющим входами которого являются соответственно первый и второй входы первого блока местного управления, о т л и- чающееся тем, что, с целью повьшения быстродействия устройства в него введены первый и второй анализаторы текущего состояния мик- ропроцессора, второй формирователь импульсов и второй блок местного управления, выход которого подключен к,входу второго формирователя и импульсов, третьему входу первого блока местного управления, одному и входов счетчика и входу первого формирователя импульсов, выход которого соединен с другим входом счетчика, выходы второго блока местного управления подключены к выходам анализаторов текущего состояния микропроцессора, первые входы подключены к управляющему входу устройства, второй вход первого анализа- .тора текущего состояния -микропроцессора является информационным входом устройства, второй и третий входы

5

5

0

, 0 5 0 5

354

второго анализатора текущего состояния микропроцессора соединены соответственно с вторым адресным входом устройства и выходом второго формирователя импульсов.

2, Устройство по п.I, отличающееся тем, что первый анализатор текущего состояния микропроцессора содержит триггеры, элементы НЕ, элемент И, элементы И-НЕ, ограничительный элемент в . виде резистора, и накопительный элемент в виде конденсатора, причем выход элемента И подключен к входу синхронизации первого триггера, прямой выход которого соединен с информационным входом второго триггераJ прямой выход которого подключен к информационному входу третьего триггера, прямой выход которого подключен к первому входу первого элемента И-НЕ, выход которого соединен с входами асинхронной установки в О триггеров, выход первого элемента НЕ подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с инверсным выходом третьего триггера, прямой выход которого является выходом анализатора, выход второго элемента И-НЕ соединен с входом

второго элемента НЕ, выход которого подключен к входу синхронизации третьего триггера, вход асинхрон- .ной установки в I которого соединен с одним из вьшодов резистора и конденсатора, другие выводы которых подключены соответственно к шине питания и шине нулевого потенциала, информационный вход первого триггера, первый вход элемента И, вторые входы элемента И и первого элемента И-НЕ и третий вход второго элемента И-НЕ, вход первого элемента НЕ и вход синхронизации второго триггера являются входами анализатора.

3. Устройство по п.I, отличающееся тем, что, второй анализатор текущего состояния микропроцессора содержит элемент ИЛИ, элемент-И, блоки задержки, )иггер, элемент И-ИЛИ-НЕ, ограничительный элемент в виде резистора и накопительный элемент в виде конденсатора, причем один из входов элемента И-ИЛИ- НЕ подключены соответственно к выходам первого блока задержки и элемента Ji, а выход соединен с входом

асинхронной установки в l триггера, прямой выход которого соединен с входом второго блока задержки и является выходом анализатора, выход второго блока задержки соединен с входом синхронизации триггера, вход асинхронной установки в О которого подключен к одним из вьюодов резистора и конденсатора, другие выводы которых подключены соответственно

к шине питания и шине нулевого потенциала, инверсньй выход триггера соединен с его информационным вхо5 ДОМ, первый вход элемента И подключен к выходу элемента ИЛИ, вход первого блока задержки, входы элемента ИЛИ, второй вход элемента И и другие входы элемента И- ИЛИ -НЕ

10-являются входами анализато - ра.

ФмаЛ

Фмг.2

29

28

25

21

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

Изобретение относится к вычислительной технике и может быть использовано в оперативных запоминающих устройствах динамического типа. , Цель изобретения - повышение быстродействия устройства. Устройство содержит первый и второй анализаторы текущего состояния микропроцессора, первый и второй блоки местного управления, первый и втор й формирователи импульсов, счетчик и мультиплексор. Работа устройства заключается в том, что регенерация информации производится в моменты простоя микропроцессора в режимах выполнения команд Ожидание, Останов, Прямой доступ в память и при дешифрации микропроцессором текущего кода команд.-Состояние микропроцессора определяется анализаторами, адрес регенерации формируется счетчиком. Использование устройства в вычислительной системе позволяет повысить ее производительность за счет исключения специальных остановов микропроцессора для регенерагдаи, 2 3.п. ф-лы, 5 ил. О iS (Л

2В

$

м

г

с

22

27:

Составитель В.Рудаков Редактор В.Иванова Техред В.Кадар Корректор М.Максимишинец

Заказ 4006/44 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Ф«г.5

| Устройство для регенерации информации в блоке памяти | 1980 |

|

SU951389A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией в блоках оперативной памяти | 1980 |

|

SU942137A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-23—Публикация

1984-04-10—Подача