f2

(/)

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1988 |

|

SU1541615A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к вычислительной технике и может быть использовано для настройки, отладки с пециализированных микроЭВМ. Целью изобретения является уменьшение времени отладки. Устройство содержит регистр 1 адреса останова, блок 2 останова по адресу, блок 3 останова по обращению к стеку, блок 4 останова по признаку начала команды, элемент ИЛИ 5, группу схем 6 сравнения, регистр 7 зоны останова, первый элемент И 8, группу элементов ИЛИ 9, второй элемент И 10, блок 11 готовности. Изобретение позволяет повысить эффективность и сократить сроки отладки за счет обеспечения адресного останова при обращении к определенной области памяти. 5 ил. a $

/У- 272f

//

/3iwr-

Зв fiSfM/na. ff/Kfts/nojmt . Pue.i

Изобретение относится к вычислительной технике л может быть использовано для настройки, отладки и проверки работы специализированных мик- роЭВМ.

Цель изобретения - уменьшение времени отладки за счет обеспечения адресного останова при обращении к определенной области памяти в зависи- мости от типа выполняемого цикла. I На фиг. 1 представлена функциона- I льная схема устройства; на фиг. 2 - 4 - схемы блоков адресного останова соответственно по обращению к памяти или внешним устройствам, по обращению к стеку и по признаку начала команды; I на фиг. 5 - одна из возможных реали- ; заций схемы адресного останова по зо- :не памяти.

1: Устройство для отладки микроЭВМ (фиг. 1) содержит регистр 1 адреса I останова, блок 2 останова по адресу, ;блок 3 останова по обращению к стек- ; лу и блок А адреса останова по приз- наку начала команды, элемент ИЛИ 5, группу схем 6 сравнения, регистр 7 зоны адресов, первый злемент И 8, .; группу элемен-Гов ИЛИ 9, второй эле- мент И 10, блок 11 готовности, вход 12 адреса устройства, выходы отлаживаемой микроэвм: разрешения ввода 13, разрешения вывода 14, разрешения чтения памяти 15, разрешения записи в ;память 16, разрешения обращения к сте Iку 17, признака начала команды 18, (синхронизации микропроцессора 19, I тактового генератора 20; рход 21 готовности отлаживаемой микроЭВМ и входы устройства: вход 22 останова по адресу, вход 23 пуска, вход 24 задания режимов. Блоки 2 и 3 связаны между собой двусторонней шиной 25. Группа схем 6 сравнения содержит N элементов сравнения 6.1,...,6.1,..., 6.N-1, 6.N, где N - количество зон останова. Все разряды регистра 1 адреса останова разделены на (N-1) групп, каждая i-я группа содержит га- разрядов (т; 1.2,...,т.), при зтом N-я группа содержит старшие разряды регистра 1. Аналогично разделен на группы разрядов вход 12 адреса устройства. Выходы каждой i-й группы регистра 1 и входы 12 подключены к входам i-й схемы 6 сравнения. Группа элементов ИЛИ 9 содержит N-1 элементов ИЛИ 9.1,. . . ,9..i,... ,9.N-1, при этом первые входы каждого элемента ИЛИ 9.л

подключены к выходу схемы 6 сравнения 6.1 (J i).

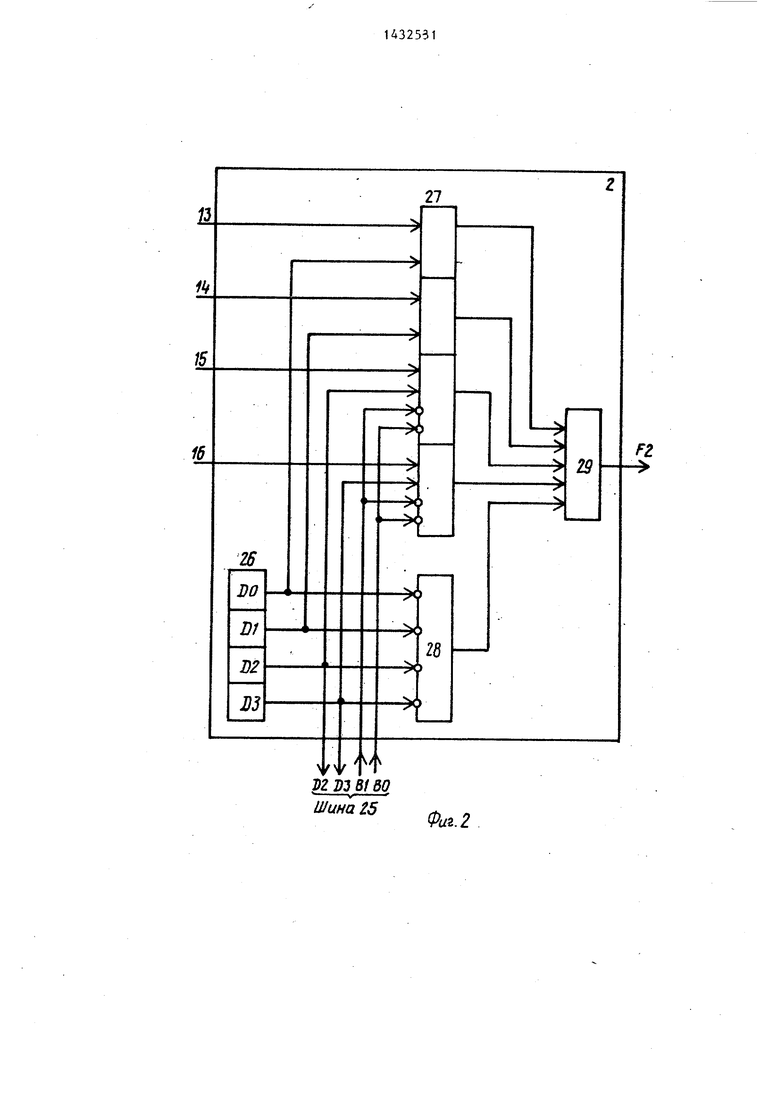

Блок 2 останова по адресу (фиг.2) содержит первый режимный регистр 26, группу элементов И 27, элемент И 28 и элемент ИЛИ 29. Разряды DO, D1, D2 и D3 режимного регистра 26 задают соответственно режимы адресного останова в циклах ввода, вывода, чтения памяти и записи в память.

Блок 3 останова по обращению к стеку (фиг. 3) содержит второй режимный регистр 30, группу элементов И 31 и элемент ИЛИ 32. Разряды ВО и В1 второго режимного регистра 30 задают режимы адресного останова при обращении соответственно к стековой области памяти и к памяти, не явля-, ющейся стековой зоной.

Выходы ВО, B1,.D2 и D3 режимных регистров 30 образуют двустороннюю шину 25.

Блок 4 останова по признаку начала команды (фиг. 4) содержит третий режимный: регистр 33, группу элементов И 34 и элемент ИЛИ 35. Разряды СО и С1 регистра 33 задают режимы адресного останова при чтении кода команды и чтения операндов команды.

Алгоритм функционирования блоков 2-4 представлен в виде логических функций F2, F3 и F4 соответственно. Сигналы, которые подаются на входы этих блокрб с выходов отлаживаемой ч микроэвм, обозначены следующим образом: РВв - разрешение ввода (вход 13) РВыв - разрешение вывода (вход 14), РЧт - разрешение чтения памяти (вход 15), РЗ - разрешение записи в память (вход 16), РСт - разрешение обращения к стеку (вход 17), НК - признак начала команды (вход 18). Тогда логические функции F25 F3 и F4, описывающие работу блоков 2-4, имеют следующий вид:

F2 РВв ООУ РВыв П1 У P4Tj 2jJO Flv

РЗп-03 ВО В1У D6-DbD2 D3;(1

F3 РСт РЗп ОЗ BOV fcT P3n-D3-B1V

РСт РЧт П2 BOY РСт РЧт.02 В1; (2

F4 HK COV RK-CI.

(3)

Регистр 7 зоны адресов, группа . схем 6 сравнения, группа элементов ИЛИ 9 и второй элемент И 10 представляют собой программированную схему

сравнения, обеспечивающую останов по определенной области памяти. Единичный сигнал на выходе .1-го разряда регистра 7 обеспечивает адресный останов при обращении к памяти, или внешним устройствам, адреса которых определены старшими j+l,...,Ы-й группами разрядов адреса, т.е., сигнал сравнения на выходе элемента И Ю не зависит от младших разрядов адреса, входящих в группы 1, . .., j .

На фиг. 5 показан пример конкретной реализации программируемой схемы сравнения. Она состоит из четырех четырехразрядных схем 6,1, 6.2, 6.3 и 6.4 сравнения, трех двухвходовых элементов ИЛИ 9.1, 9.2 и 9.3, четыре входового элемента И 10 и трехразрядного регистра зоны адресов (показаны разряды регистра АО-, А1 и А2) . Когда все разряды регистра зоны адресов в нулевом состоянии, сравниваются все 16 разрядов входных слов (режим непосредственного сравнения). Если раз- 25 на входе 22 устройства, при появле- ряд АО регистра зоны адресов находит- нии на входе 12 кодов, принадлежащих

ся в единичном состоянии, сравниваются только старшие 12 разрядов входных слов и определяется их принадлежность одной и той же 16-байтной зоне. При единичном состоянии разряда А1 и разряда А2 регистра зоны адресов определяется принадлежность входных слов одной и той же 256-байтной и 4096-байтной зоне соответственно. Такая организация позволяет организоват режимы останова по различным зонам адресов, причем размер зона задается оператором.

Устройство для отладки микроЭВМ обеспечивает следующие аппаратные режимы отладки: общий останов по адресу либо зоне, останов по адресу либ зоне адресов при записи в ОЗУ микро- ЭВМ, при записи в стек, при записи в область ОЗУ, не являющуюся стеком; останов по адресу либо зоне адресов при чтении памяти, при чтении стека, при чтении области памяти, не являющейся стеком; останов по адресу либо зоне адресов при вводе информации из внешнего устройства, останов по адресу либо зоне адресов при выводе информации во внешнее устройство, останов по адресу либо зоне адресов при чтении кода команды, останов по адресу либо зоне адресов при чтении операндов команды, а также комбинации в Bbmie перечисленных режимов, шаговый

режим поциклового прохождения про:- раммы, шаговый режим Покомандного ппохождения программы.

Устройство для отладки микроЭВМ в указанных вьш1е режимах работает следующим образом.

Общий режим останова по адресу производится при установленных в ну-.

левое состояние всех разрядов регистра 7 зоны адресов, первого 26, второго 30 и третьего 33 режимных регистров. При наличии высокого уровня на входе 22 устройства и при равенст-

ве адресов, приходящих на входы схем 6 сравнения из шины 12 адреса и регистра 1 адреса останова, единичный уровень появляется на первом входе блока 11, что ведет к появлению сигнала низкого уровня на входе 21 готовности отлаживаемой микроЭВМ, вызывающего ее останов. Общий останов по зоне адресов происходит при установке в единичное состояние сигнала

0

5

0

одной зоне, определяемой установкой соответствующего разряда регистра 7 зоны адресов в единичное состояние и при нулевом состоянии разрядов DO,...,D3 первого режимного регистра 26. При этом на все входы первого элемента И 8 поступаю.т сигналы высокого уровня, и первьй вход блока 11 готовности устанавливается в единичное состояние, после чего по синхронизирующему сигналу в цепи 19 на выходе 21 .готовности Появляется сигнал низкого уровня.

Останов по адресу либо зоне а,цре- сов при записи и нтении памяти, запи си и чтении стека, записи и чтении областей памяти, не являющейся стеком, вводе и выводе информации во

5 внешнее устройство производится при появлении соответствующих одноименных сигналов на входах 13-17 и установленных в единичное состояние соответствующих режиму останова разряQ дов первого 26 и второго 30 режимных регистров. При этом сигнал высокого- уровня поступает на второй вход первого элемента И 8 через элемент ИЛИ 9 с выходов блока 2 и (или) в соответс ствии с логическими выражениями (1) и (2). Например, режим останова по зоне адресов при записи в память, не являющуюся стеком, организовывается путе1# установки в единичное состояние сигнала на входе 22 устройства, разрядов D3 первого режимного регистра 26, В1 второго режимного регистра 30 и одного из разрядов регистра 7 зоны адресов, задающего требуемый размер зоны. На регистре 1 адреса останова устанавливается один из адресов интересующей зоны. При сравнении старших разрядов входа 12 адреса и регистра 1 адреса останова на первом входе первого элемента И 8 формируется сигнал высокого уровня. В соответствии с выражением (2) выход блока 3

ляются соответственно входами пуска, задания режимов, синхронизации, так- товым и признака начала команды устройства, выход блока готовности является выходом останова устройства, отличающееся тем, что, с целью уменьшения времени отладки в . устройство введены блок останова по обращению к стеку, блок адреса останова по признаку начала команды, регистр зоны адресов, группа схем сравнения, группа элементов ИЛИ, второй элемент И, элемент ИЛИ, причем перF3 устанавливается в единичное состо- 15 вый, второй и третий входы блока осяние и сигнал высокого уровня прихо- дит на второй вход первого элемента И 8; первый вход блока 11 готовности устанавливается в единичное состоя- ни,, а на вхЬде 21 готовности отлаживаемой микроэвм устанавливается сигнал низкого уровня, по которому микроэвм переходит в режим ожидания (останова).

Режим останова по адресу либо по зоне адресов при чтении кода команды организовьшается установкой в единичное состояние разрядов D3 первого режимного регистра 26 и третьего режимного регистра 33 и соответствующе установке регистров зоны адресов 7 и адреса останова 1.

Останов по адресу либо зоне адресов при чтении операндов команды достигается установкой в единичное состояние разрядов D3 первого режимного регистра 26 и С1 третьего режимного регистра 33.

Формула изобретения

Устройство для отладки микроЭВМ, содержащее блок останова по адресу, регистр адреса останова, блок готовности, первый элемент И, причем первый - четвертый входы блока останова по адресу соединены соответственно с выходами разрещения ввода,разрешения вы45 (, N-1, N - количество зон оста- нова) соединены с соответствующими входами второго элемента И, выход KOторого соединен с третьим входом первого элемента И, каждый i-й выход

вода,разрешения чтения и разрешения записи устройства, вход останова по адресу регистра зон останова соединен с устройства соединен с первым входом пер- (1+1)-ми входами всех элементов ИЛИ вого элемента И, выход которого сое- группы, блок останова по адресу через динен с первым входом блока готовнос- двустороннюю магистраль соединен с ти, второй - шестой входы которого яв блоком останова по обращению к стеку.

ляются соответственно входами пуска, задания режимов, синхронизации, так- товым и признака начала команды устройства, выход блока готовности является выходом останова устройства, отличающееся тем, что, с целью уменьшения времени отладки в . устройство введены блок останова по обращению к стеку, блок адреса останова по признаку начала команды, регистр зоны адресов, группа схем сравнения, группа элементов ИЛИ, второй элемент И, элемент ИЛИ, причем первый, второй и третий входы блока останова по обращению к стеку являются входами устройства и подключены со- ответственно к выходам разрешения обращения к стеку, разрешения записи

и разрещения чтения отслеживаемой микроэвм, выход блока ос.танова по обращению к стеку соединен с первым входом элемента ИЛИ, вход признака начала команды устройства соединен с

входом блока останова по признаку начала команды, выход которого соединен с вторым входом элемента ИЛИ, выход блока останова по адресу соединен с третьим входом элемента--ШШ, выход которого соединен с вторым входом первого элемента И, выход каждого разряда регистра адреса останова, соединен с первым входом соответствующей схемы сравнения группы, каждый адресньй вход устройства соединен с вторым входом соответствующей схемы сравнения группы, каждая схема сравнения группы, кроме схемы сравнения старших разрядов адреса группы, соединена

с входом соответствующего элемента ШШ группы, выход схемы сравнения старших разрядов адреса группы соединен с (i+1)-M входом второго элемента И, выходы i-x элементов ИЛИ группы

(, N-1, N - количество зон оста- нова) соединены с соответствующими входами второго элемента И, выход KOF- торого соединен с третьим входом первого элемента И, каждый i-й выход

регистра зон останова соединен с (1+1)-ми входами всех элементов ИЛИ группы, блок останова по адресу через двустороннюю магистраль соединен с блоком останова по обращению к стеку.

Шина 25

Фаг. 2

Шина 25

Фаг.

Фиг.Ч

Шина адреса 12

Фиг.5

| Патент США № 4308581, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-09-08—Подача