мяти содержит элементы НР, ключи, дифференциальные усилители (ДУ), шину питания, тактовые шины, шину нулевого потенциала. Первые и вторые входы ДУ являются входами ячейки памяти. Третьи входы ДУ соединены с выходами ключей, входы которых соединены с шинами питания и с тактовыми

Изобретение относите; к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании аналого- цифровых больших интегральных схем, в Качестве компаратора, накопителей

и ТоПо

Цель изобретения - повьшение быстродействия и надежности компаратора.

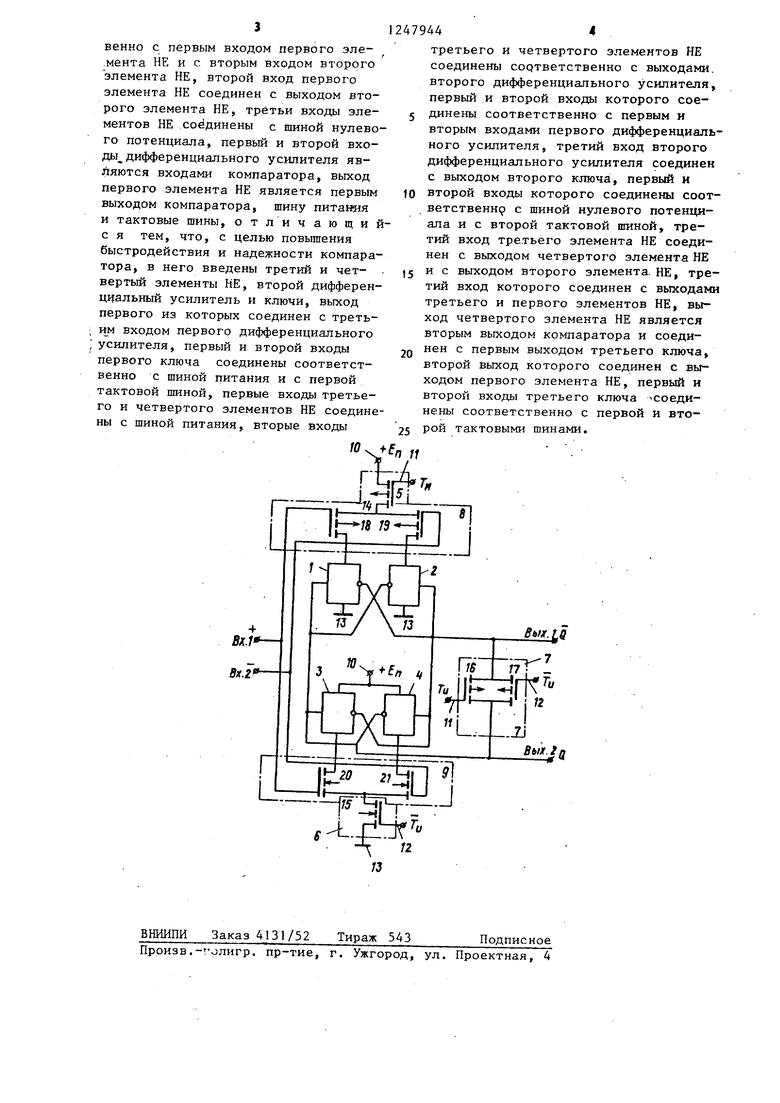

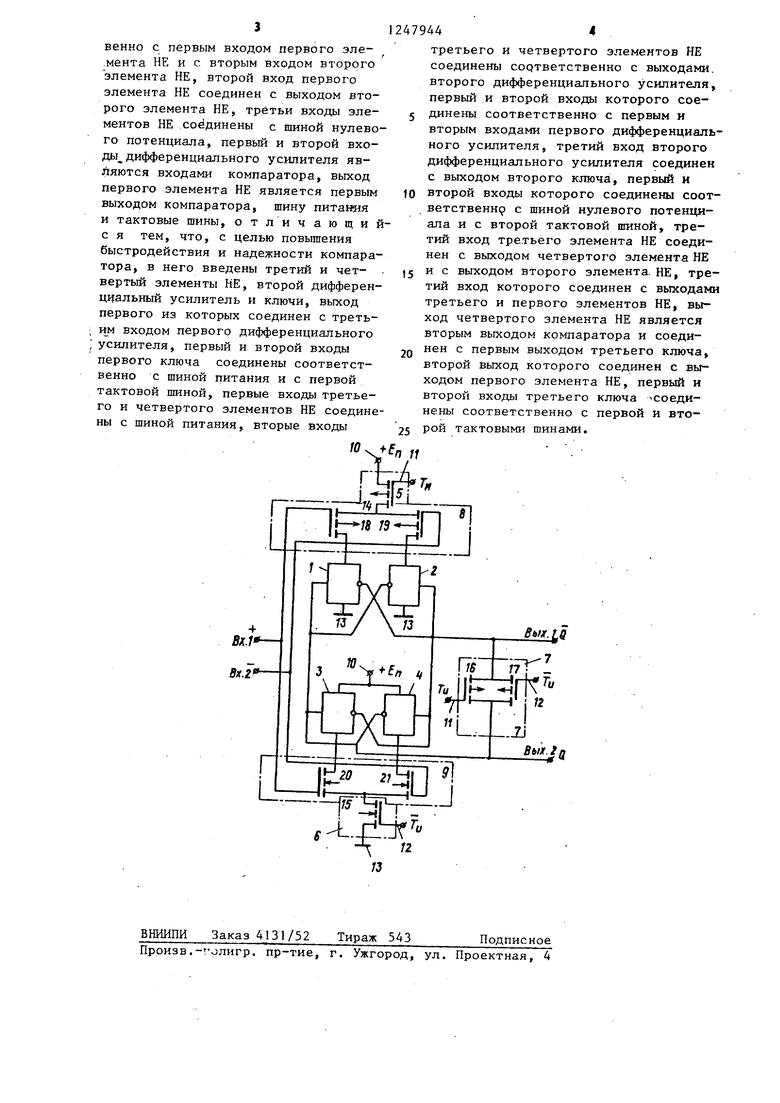

На чертеже изображена функциональ ная схема компаратора

Схема содержит элементы НЕ -4, ключи 1-4, ключи 5-7, дифференциальные усилители 8 и 9, шину 10 питания тактовые шины 11 и 12, шину 13 нуле- вого потенциала. Ключи 5-7 выполнены на транзисторах 14-17, дифференциальные усилители 8 и 9 - на транзисторах 18-21 о

Предлагаемый компаратор работает следующим образом.

При наличии тактового импульса Т на шине 12 ключи 5 и 6 закрыты, а ключ 7 открыт и на выходах компа- ратора поддерживается примерно половина напряжения питания +Е. С приходом отрицательного фронта импульса синхронизации ключи 5 и 6 открываются, а ключ 7 закрывается.

В зависимости от того, на каком входе (Вх.1 или Вх.2) выше потенциал, ток питания элементов НЕ 1 и 4, 2 и 3 оказывается различным, поэто- му один из элементов НЕ 1 или 2 устанавливается в состояние с высо- КИМ потенциалом на выходе, а тот из элементов НЕ 3 или 4, которьй питается большим током, устанавливается в состояние с низким потенциалом на .выходе. В результате переходного прО цесса большее напряжение на входе

шинами. Выходы ДУ соединены с одними из входов элементов НЕ, причём элементы НЕ соединены перекрестными связями. Выходы элементов НЕ явля- ются выходами устройства и соединены с выходами ключа, входы которого соединены с тактовыми шинами . 1 ил.

Вх.1 приводит к появлению на Вых.2 высокого потенциала, а на - низкого потенциала. Данное состояние сохраняется до окончания тактового импульса Т О.

При Tf, I компаратор устанавливается в исходное состояние.

Наличие ключа 7 способствует быстрому установлению исходного состояния, т.е. повьш1ает и быстродействие, так как компаратор, тактируется по отрицательному фронту импульса синхронизации.

Компаратор содержит два канала сравнения входных напряжений. Выход из строя одного из каналов не нарушает его ра боту в целом, при этом может сравнивать любые напряжения в диапазо не от О до напряжения питания, при этом его чувствительность на границах отпирания одного из каналов вьш1е за счет работы другого канала при больших токах стока (при

ЕП ОТр.И U(,-rn,p)

Компаратор обладает меньшим про- лезанием сигнала синхронизации на ее входы за счет наличия двух противоположных по знаку сигналов помехи от каждого канала, которые скла- дагваются и взаимно компенсируют друг друга. В результате этого амплитуда помехи уменьшается в 2-10 раз- что приводит к повьш1ению надежности, .

Формула изобретения

Компаратор, содержащий первьй элемент НЕ, выход которого соединен с первым входом второго элемента НЕ, первый дифференциальный усилитель, выходы которого соединены соответст3

венно с первым входом первого элемента НЕ и с вторым входом второго элемента НЕ, второй вход первого элемента НЕ соединен с выходом второго элемента НЕ, третьи входы элементов НЕ соединены с шиной нулевого потенциала, первый и второй входы дифференциального усилителя являются входами компаратора, выход первого элемента НЕ является первым выходом компаратора, шину питания и тактовые шины, отличающий с я тем, что, с целью повышения быстродействия и надежности компаратора, в него введены третий и четвертый элементы НЕ, второй дифферен- ццальный усилитель и ключи, выход первого из которых соединен с треть- входом первого дифференциального усилителя, первый и второй входы первого ключа соединены соответственно с шиной питания и с первой тактовой шиной, первые входы третьего и четвертого элементов НЕ соединены с шиной питания, вторые входы

479444

третьего и четвертого элементов НЕ соединены соответственно с выходами, второго дифференциального усилителя, первый и второй входы которого сое- 5 динены соответственно с первым и

вторым входами первого дифференциального усилителя, третий вход второго дифференциального усилителя соединен с выходом второго ключа, первый и to второй входы которого соединены соот- ветственН9 с шиной нулевого потенциала и с второй тактовой шиной, третий вход третьего элемента НЕ соединен с выходом четвертого элемента НЕ и с выходом второго элемента. НЕ, третий вход которого соединен с выходами третьего и первого элементов НЕ, выход четвертого элемента НЕ является вторым выходом компаратора и соединен с первым выходом третьего ключа, второй выход которого соединен с выходом первого элемента НЕ, первый и второй входы третьего ключа соеди- нены соответственно с первой и вто- 25 рой тактовыми шинами.

15

20

Л

.J

Вх.2

25 1 1

- Лг-ь-лВ I

-Я Гтг-:,.sr±

Л « ;j

/J

«

Пб г«||1 | Н 1 12

Г7Т IrVfu

/I

L.

...ZJ

Bbix.JQ

.sr±

Л « ;j

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр | 1981 |

|

SU1024989A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Элемент с тремя состояниями | 1983 |

|

SU1148113A1 |

| Цифровой измеритель добротности | 1988 |

|

SU1647456A1 |

| Компаратор | 1980 |

|

SU949627A1 |

| Кодек адаптивного дельта-модулятора | 1986 |

|

SU1378063A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам, и может быть использовано при создании аналого-цифровых БИС в качестве компараторов, накопителей.и т.д. Цель изобретения - расширение области при- 1менения ячейки памяти, которая достигается введением новых элементов и новых связей, позволяющих увеличить ее динамический диапазон. Ячейка пац kl СО 4 «

ВНИИПИ Заказ 4131/52 Тираж 543

Подписное

Произв.-т олигр. пр-тие, г. Ужгород, ул. Проектная, 4

Подписное

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-30—Публикация

1984-01-26—Подача