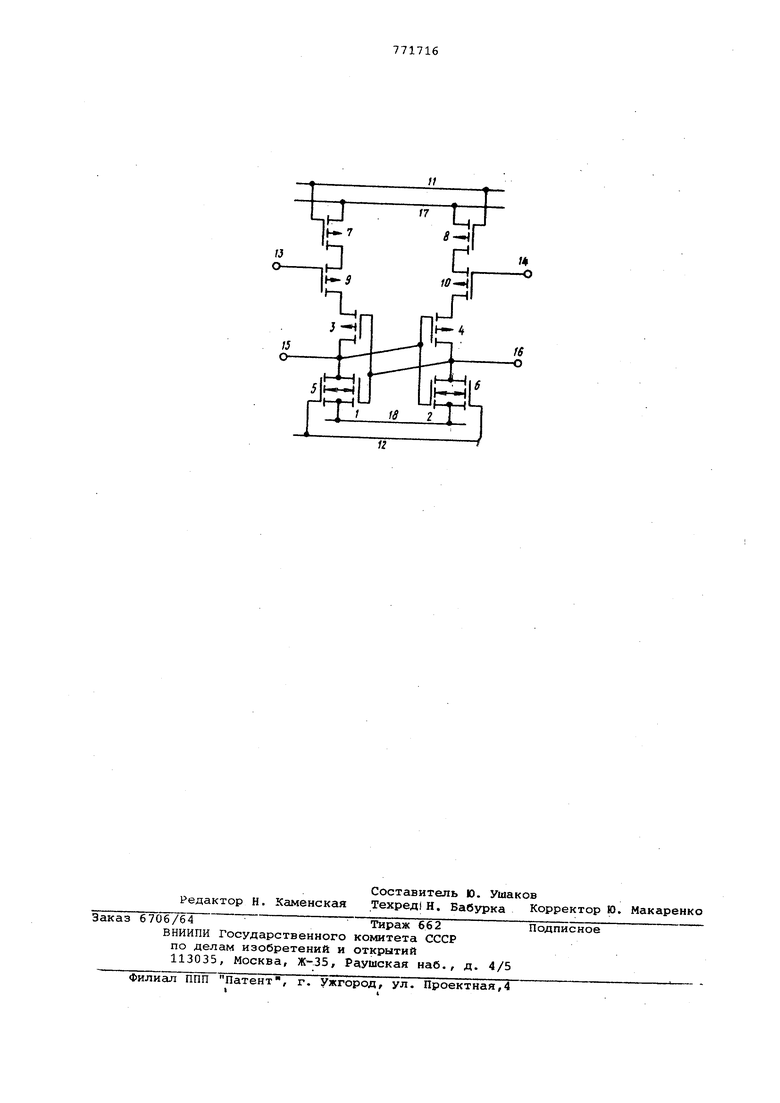

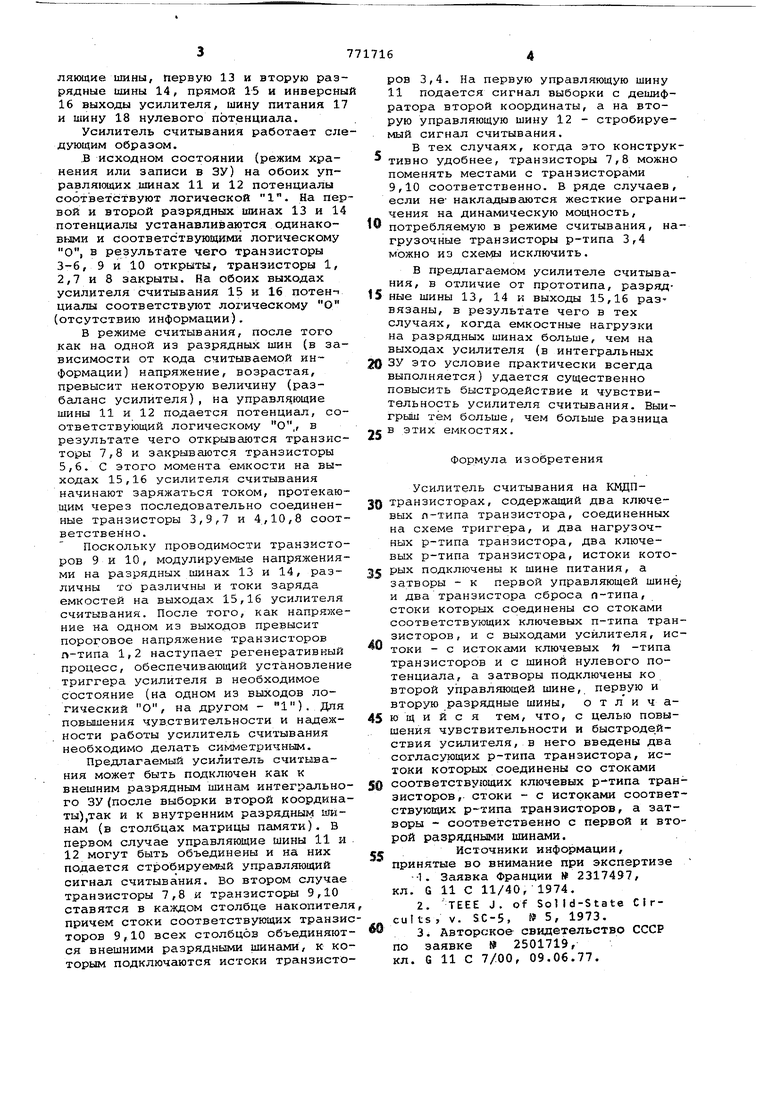

Изобретение относится к области вычислительной техники и может быть использовано при построении микромощных интегральных запоминающих устройств КМДП-транзисторах. Известны усилители считывания С11и ( построенные в виде инверторов или триггеров на КМДП-транзисторах, вхо ды и выходы которых закорачиваются помощью отдельного транзистора. Недостатком их является сложност управления и критичность к фазовым соотношениям между управляющими сиг Нсшами. Наиболее близким к данному является. усилитель считывания,содержащий два нагрузочных р-типа транг транзистора и два ключевых п-типа транзистора, соединенных по схеме триггера, два ключевых р-типа транзистора, истоки которых подключены к шине питания, а затворы - к первой управляющей шине, и два тран зистора сброса -И -типа, стоки которых соединены со стоками соответствующих ключевых п-типа транзисторов и с выходами усилителя, истоки - с истоками ключевых п-типа транзисторов, а затворы подключены ко второй управляющей шине,первую и вторую раз рядные шины, совмещенные с выходами усилите.пя, к которым подключены стоки ключевых р-типа транзисторов 3. Недостатком этого усилителя является низкие чувствительность и быстродействие, за счет совмещения выходов и разрядных шин, имеющих большую емкостную нагрузку. Целью изобретения является повы шение чувствительности и быстродействия усилителя считывания. Поставленная цель достигается тем, что в усилитель считывания н КМД-транзисторах введены два согласующих р-типа транзистора, истоки которых соединены со стоками соответствующих ключевых р-типа транзисторов, стоки - с истоками соответствующих нагрузочных р-типа транзисторов,, а затворы - соответственно с первой и второй разрядными шинами. На чертеже приведена электрическая схема усилителя, который содержит два ключевых п-типа транзистора 1 и 2, соединяющих на схеме триггера, два нагрузочных р-типа транзистора 3 и 4, два транзистора сброса п-типа 5 и 6, два ключевых р-типа транзистора 7 и 8, два согласуквдих р-типа транзистора 9 и 10, первую 11 и вторую 12 управляющие шины, первую 13 и вторую разрядные шины 14, прямой 15 и инверсны 16 выходы усилителя, шину питания 17 и шину 18 нулевого потенциала.

Усилитель считывания работает следующим образом.

.В исходном состоянии (режим хранения или записи в ЗУ) на обоих управляющих шинах 11 и 12 потенциалы соответствуют логической 1. На первой и второй разрядных шинах 13 и 14 потенциалы устанавливаются одинаковыми и соответствующимк логическому О, в результате чего транзисторы 3-6, 9 и 10 открыты, транзисторы 1, 2,7 и 8 закрыты. На обоих выходах усилителя считывания 15 и 16 потен-i циалы соответствуют логическому О (отсутствию информации).

В режиме считывания, после того как на одной из разрядных шин (в зависимости от кода считываемой информации) напряжение, возрастая, превысит некоторую величину (разбаланс усилителя), на управля.ющие шины 11 и 12 подается потенциал, соответствующий логическому О,, в результате чего открываются транзисторы 7,8 и закрываются транзисторы 5,6. С этого момента емкости на выходах 15,16 усилителя считывания начинают заряжаться током, протекающим через последовательно соединенные транзисторы 3,9,7 и 4,10,8 соответственно.

Поскольку проводимости транзисторов 9 и 10, модулируемые напряжениями на разрядных шинах 13 и 14, различны то различны и токи заряда емкостей на выходах 15,16 усилителя считывания. После того, как напряжение на одном из выходов превысит пороговое напряжение транзисторов п-типа 1,2 наступает регенеративный процесс, обеспечивающий установление триггера усилителя в необходимое состояние (на одном из выходов логический О, на другом - 1). Для повышения чув.ствительности и надежности работы усилитель считывания необходимо делать симметричным.

Предлагаемый усилитель считывания может быть подключен как к внешним разрядным шинам интегрального ЗУ (после выборки второй координаты),так и к внутренним разрядным шинам (в столбцах матрицы памяти). В первом случае управляющие шины 11 и 12 могут быть объединены и на них подается строб ируемый управляющий сигнал считывания. Во втором случае транзисторы 7,8 и транзисторы 9,10 ставятся в каждом столбце накопителя причем стоки соответствующих транзисторов 9,10 всех столбцов объединяются внешними разрядными шинами, к которым подключаются истоки транзисторов 3,4. На первую управляющую шину 11 подается сигнал выборки с деашфратора второй координаты, а на вторую управляющую шину 12 - стробируемый сигнал считывания.

В тех случаях, когда это конструктивно удобнее, транзисторы 7,8 можно поменять местами с транзисторами 9,10 соответственно. В ряде случаев, если не- накладываются жесткие ограничения на динамическую мощность, 0 потребляемую в режиме считывания, нагрузочные транзисторы р-типа 3,4 можно из схемы исключить.

В предлагаемом усилителе считываНИН, в отличие от прототипа, разрядные шины 13, 14 и выходы 15,16 развязаны, в результате чего в тех случаях, когда емкостные нагрузки на разрядных шинах больше, чем на выходах усилителя (в интегральных

0 ЗУ это условие практически всегда выполняется) удается существенно повысить быстродействие и чувствительность усилителя считывания. Выигрыш тем больше, чем больше разница

в этих емкостях.

Формула изобретения

Усилитель считывания на КМДП0 транзисторах, содержащий два ключевых л-типа транзистора, соединенных на схеме триггера, и два нагрузочных р-типа транзистора, два ключевых р-типа транзистора, истоки которых подключены к шине питания, а

затворы - к первой управляющей шинёу и два транзистора сброса п-типа, стоки которых соединены со стоками соответствующих ключевых п-типа транзисторов, и с выходами усилителя, ис токи - с истоками ключевых t -типа транзисторов и с шиной нулевого потенциала, а затворы подключены ко второй управляющей шине, первую и вторую разр5здные шины, о т л и ч а5 ю Щ и и с я тем, что, с целью повышения чувствительности и быстродействия усилителя, в него введены два согласующих р-типа транзистора, истоки которых соединены со стоками

0 соответствующих ключевых р-типа транзисторов, стоки - с истоками соответствующих р-типа транзисторов, а затворы - соответственно с первой и второй разрядными шинами.

Источники информации,

принятые во внимание при экспертизе

1. Заявка Франции №2317497, кл. G 11 С 11/40, 1974.

2. ТЕЕЕ J. of Solid-state Circutts , V. SC-5, 5, 1973. 3. Авторское свилетельство СССР по заявке 2501719, кл. G 11 С 7/00, 09.06.77.

/;

17

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

Авторы

Даты

1980-10-15—Публикация

1978-09-29—Подача