Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах для преобразования декартовых прямоугольных координат точки в полярные координаты.

Целью изобретения является иовып1ение быстродействия за счет реализации алгоритма цифрового интегрирования на комбинационных логических элементах, заменой операции деления эквивалентной операцией сдвига и выполнением всех операций над параллельными кодами.

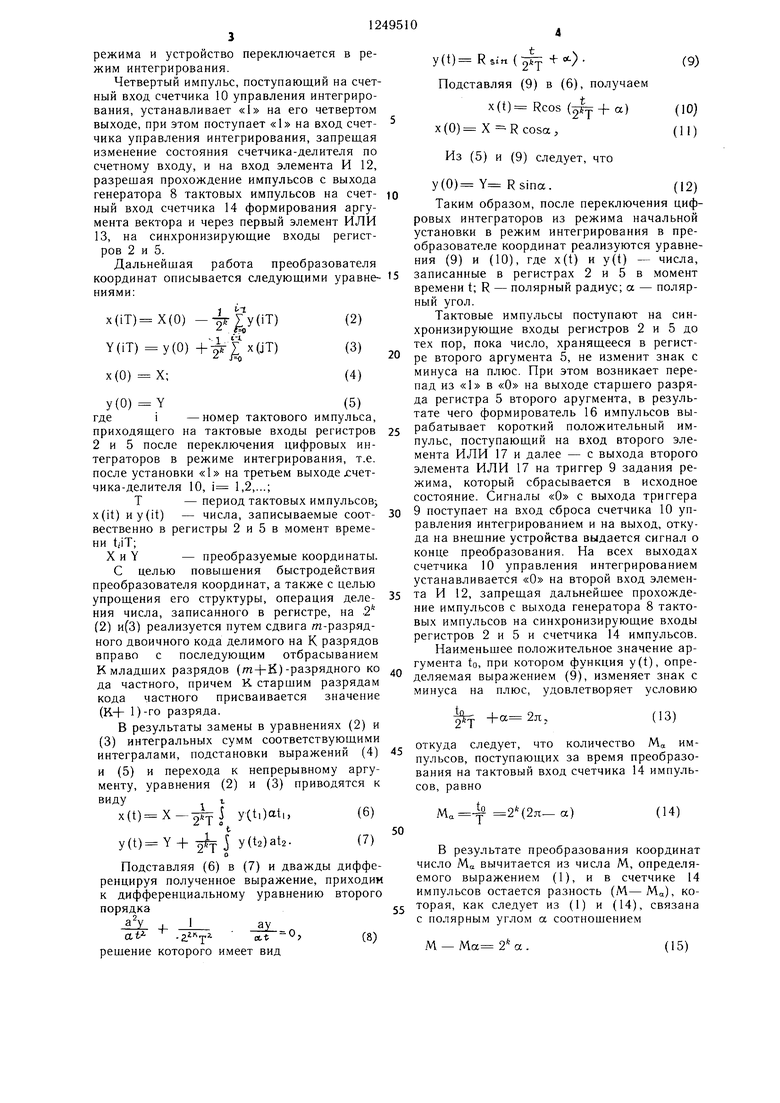

На чертеже представлена функциональная схема устройства.

Устройство содержит первый мультиплексор 1, регистр 2 первого аргумента,

ров подаются параллельные т-разрядные обратные двоичные коды преобразуемых декартовых прямоугольных координат X и Y. Преобразование начинается после прихода импульса запуска на вход установки триггера 9 задания режима. Передний фронт импульса запуска (перепад из «О в «1) устанавливает триггер 9 задания- режима в состояние «1. Сигнал «1 с выхода триггера 9 поступает на вход сброса счетчика 10 управления интегрированием. По переднему фронту очередного тактового импульса, поступающего с выхода генератора 8 тактовых импульсов на счетный вход счетчика 10, на первом выходе счетчика устанавливается логическая «1. Перепад из

ратор 8 тактовых импульсов, триггер 9 задания режима, счетчик 10 управления инпервый сумматор 3, второй мультиплексор 5 в «1, поступающий с первого выхода счет- 4, регистр 5 второго аргумента, группачика 10 на вход триггера 11 блокировки,

элементов НЕ 6, второй сумматор 7, гене- сбрасывает его в состояние «О, что приводит

к блокировке триггера 9 задания режима (сигнал «О, поступающий с выхода второго

тегрированием, триггер 11 блокировки, эле- триггера 11 на вход блокировки тригге- мент И 12, первый элемент ИЛИ 13, счет- ра 9, запрещает срабатывание первого триг- чик 14 формирования аргумента вектора, дешифратор 15 нуля, формирователь 16 импульсов, второй элемент ИЛИ 17, выход 18 модуля вектора устройства, выход 19 аргугера от входных импульсов), а также к переключению устройства в режим начальной установки (сигнал «О поступает с выхода триггера 11 блокировки на управляюмента вектора устройства, выход 20 призна- 25 Щие входы мультиплексоров и 4, в результате чего на входы регистров 2 и 5 с выходов соответствующих мультиплексоров подаются коды преобразуемых координат). Второй (от начала преобразования) тактовый импульс, поступающий с выхода ге- 30 нератора 8 тактовых импульсов на тактовый вход счетчика 10 управления интегрирования, устанавливает «1 на его втором выходе, к которому подключены вход первого элемента ИЛИ 13 и вход разрешения записи счетчика 14 импульсов. Поскольку на

ка завершения вычислении устройства, входы 21 записи начального кода устройства, вход 22 абсциссы устройства и вход 23 ординаты устройства.

Устройство функционирует следующим образом.

В исходном состоянии генератор 8 тактовых импульсов вырабатывает прямоугольные импульсы, поступающие на счетный вход счетчика 10 управления интегрированием и первый вход элемента И 12. Тригтате чего на входы регистров 2 и 5 с выходов соответствующих мультиплексоров подаются коды преобразуемых координат). Второй (от начала преобразования) тактовый импульс, поступающий с выхода ге- 30 нератора 8 тактовых импульсов на тактовый вход счетчика 10 управления интегрирования, устанавливает «1 на его втором выходе, к которому подключены вход первого элемента ИЛИ 13 и вход разрешения записи счетчика 14 импульсов. Поскольку на

гер 9 задания режима находится в состоя- 35 другой вход первого элемента ИЛИ 13 поНИИ «О. Выходной сигнал триггера 9, поступая на вход сброса счетчика 10 управления интегрирования, устанавливает «О на всех его выходах, при этом тактовые импульсы на состояние счетчика не влияют. ,„ т-1 , 40

Триггер 11 блокировки находится в состоянии «1. Выходной триггера 11, поступая на управляющие входы мультиплексоров, подключает входы первого 2 и второго 5 регистров соответственно к выходам персту пает «О с выхода элемента И 12, импульс, формируемый на втором выходе счетчика 10 управления интегрирования, через первый элемент ИЛИ 13 поступает на синхронизирующие входы регистров 2 и 5; по переднему фронту этого импульса в регистр 2 первого аргумента записывается код абсциссы, а в регистр 5 второго аргумента записывается код ординаты. Импульс, поступающий с второго выхода счетчика 10 упМ л.

(1)

вого 3 и второго 7 сумматоров. Устройство 45 Р вления интегрированием на вход разреше- находится в режиме интегрирования, но ин- нния записи счетчика 14 формирования аргу- тегрирования не происходит, поскольку ло-мента вектора, производит запись в счетгический сигнал «О, поступающий с чет- чик числа вертого выхода счетчика 10 управления интегрированием на вход элемента И 12, запрещает прохождение импульсов с выхода генератора 8 тактовых импульсов на сипхро- низирующие входы регистров 2 и 5. Выходной код счетчика 14 формирования аргумента вектора ие изменяется, так как на вход счетчика, подключенный к выходу элемента И 12, импульсы не поступают.

К моменту начала преобразования на входы первого 1 и второго 4 мультиплексо50 где К - коэффициент нормирования.

По переднему фронту третьего тактового импульса, поступающего на тактовый вход счетчика 10 управления интегрирования, устанавливается «1 на третьем выходе. Перепад из «О в «1, возникающий на

55 входе триггера 11 блокировки, устанавливает «1 на его выходе, в результате чего снимается блокировка с триггера 9 задания

ров подаются параллельные т-разрядные обратные двоичные коды преобразуемых декартовых прямоугольных координат X и Y. Преобразование начинается после прихода импульса запуска на вход установки триггера 9 задания режима. Передний фронт импульса запуска (перепад из «О в «1) устанавливает триггер 9 задания- режима в состояние «1. Сигнал «1 с выхода триггера 9 поступает на вход сброса счетчика 10 управления интегрированием. По переднему фронту очередного тактового импульса, поступающего с выхода генератора 8 тактовых импульсов на счетный вход счетчика 10, на первом выходе счетчика устанавливается логическая «1. Перепад из

триггера 11 на вход блокировки тригге- ра 9, запрещает срабатывание первого триг-

гера от входных импульсов), а также к переключению устройства в режим начальной установки (сигнал «О поступает с выхода триггера 11 блокировки на управляюЩие входы мультиплексоров и 4, в результате чего на входы регистров 2 и 5 с выходов соответствующих мультиплексоров подаются коды преобразуемых координат). Второй (от начала преобразования) тактовый импульс, поступающий с выхода ге- нератора 8 тактовых импульсов на тактовый вход счетчика 10 управления интегрирования, устанавливает «1 на его втором выходе, к которому подключены вход первого элемента ИЛИ 13 и вход разрешения записи счетчика 14 импульсов. Поскольку на

другой вход первого элемента ИЛИ 13 по другой вход первого элемента ИЛИ 13 посту пает «О с выхода элемента И 12, импульс, формируемый на втором выходе счетчика 10 управления интегрирования, через первый элемент ИЛИ 13 поступает на синхронизирующие входы регистров 2 и 5; по переднему фронту этого импульса в регистр 2 первого аргумента записывается код абсциссы, а в регистр 5 второго аргумента записывается код ординаты. Импульс, поступающий с второго выхода счетчика 10 упМ л.

(1)

к числа

чик числа

где К - коэффициент нормирования.

По переднему фронту третьего тактового импульса, поступающего на тактовый вход счетчика 10 управления интегрирования, устанавливается «1 на третьем выходе. Перепад из «О в «1, возникающий на

входе триггера 11 блокировки, устанавливает «1 на его выходе, в результате чего снимается блокировка с триггера 9 задания

режима и устройство переключается в режим интегрирования.

Четвертый импульс, поступающий на счетный вход счетчика 10 управления интегрирования, устанавливает «1 на его четвертом выходе, при этом поступает «1 на вход счет- чика управления интегрирования, запрещая изменение состояния счетчика-делителя по счетному входу, и на вход элемента И 12, разрещая прохождение импульсов с выхода генератора 8 тактовых импульсов на счет- ный вход счетчика 14 формирования аргумента вектора и через первый элемент ИЛИ 13, на синхронизирующие входы регистров 2 и 5.

Дальнейшая работа преобразователя координат описывается следующими уравне- ниями:

}

1-1

x(iT)X(0) -iFly(iT)

Y(iT)y(0) x(jT) яь

x(0) X;

(2) (3) (4) (5)

y(0)Y

гдеi -номер тактового импульса,

приходящего на тактовые входы регистров 2 и 5 после переключения цифровых интеграторов в режиме интегрирования, т.е. после установки «1 на третьем выходе чет- чика-делителя 10, i 1,2,...;

Т- период тактовых импульсовx(it) и у (it) - числа, записываемые соот- вественно в регистры 2 и 5 в момент времени t;iT;

X и У- преобразуемые координаты.

С целью повышения быстродействия преобразователя координат, а также с целью упрощения его структуры, операция деления числа, записанного в регистре, на .2 (2) и(3) реализуется путем сдвига т-разряд- ного двоичного кода делимого на К разрядов вправо с последующим отбрасыванием К младших разрядов (т+К)-разрядного ко да частного, причем К старшим разрядам кода частного присваивается значение (К+ 1)-го разряда.

В результаты замены в уравнениях (2) и (3) интегральных сумм соответствующими интегралами, подстановки выражений (4) и (5) и перехода к непрерывному аргументу, уравнения (2) и (3) приводятся к

видуг

x(t)X yCti)at,,(6)

(t)Y+ 2 y(t2)at2.

Подставляя (6) в (7) и дважды дифференцируя полученное выражение, приходим к дифференциальному уравнению второго

-b

1

aiL

CLt

0,

решение которого имеет вид

5

0

5

5

0

Q

y(t) Rsin(2rj; + )-(9)

Подставляя (9) в (6), получаем

x(t) Rcos ()(10)

x(0) X Rcosa,(11)

Из (5) и (9) следует, что

У(0) У Rsina.(12)

Таким образом, после переключения цифровых интеграторов из режима начальной установки в режим интегрирования в преобразователе координат реализуются уравнения (9) и (10), где x(t) и y(t) - числа, записанные в регистрах 2 и 5 в момент времени t; R - полярный радиус; а - полярный угол.

Тактовые импульсы поступают на синхронизирующие входы регистров 2 и 5 до тех пор, пока число, хранящееся в регистре второго аргумента 5, не изменит знак с минуса на плюс. При этом возникает перепад из «1 в «О на выходе старшего разряда регистра 5 второго аругмента, в результате чего формирователь 16 импульсов вырабатывает короткий положительный импульс, поступающий на вход второго элемента ИЛИ 17 и далее - с выхода второго элемента ИЛИ 17 на триггер 9 задания режима, который сбрасывается в исходное состояние. Сигналы «О с выхода триггера 9 поступает на вход сброса счетчика 10 управления интегрированием и на выход, откуда на внешние устройства выдается сигнал о конце преобразования. На всех выходах счетчика 10 управления интегрированием устанавливается «О на второй вход элемента И 12, запрещая дальнейшее прохождение импульсов с выхода генератора 8 тактовых импульсов на синхронизирующие входы регистров 2 и 5 и счетчика 14 импульсов.

Наименьшее положительное значение аргумента to, при котором функция y(t), определяемая выражением (9), изменяет знак с минуса на плюс, удовлетворяет условию

V 24

+а 2л,

:i3)

откуда следует, что количество М импульсов, поступающих за время преобразования на тактовый вход счетчика 14 импульсов, равно

55

М,

50

,- 2 (2.4- а)

(14)

В результате преобразования координат число Ма вычитается из числа М, определяемого выражением (1), и в счетчике 14 импульсов остается разность (М-Ма), которая, как следует из (1) и (14), связана с полярным углом а соотношением

(8)

М - Ма 2 а .

(15)

Из (10) и (13) следует, что в момент изменения знака числа в регистре 5 второго аргумента с минуса на плюс в регистре 2 первого аргумента будет записано число

x{t(,)R.(16)

Таким образом, по окончании преобразования на выход устройства с выхода регистра 2 первого аргумента поступает параллельный т-разрядный обратный двоичный код полярного радиуса R, а на другой выход устройства с выхода счетчика 14 формирования аргумента вектора поступает код числа, равного произведению полярного угла а на постоянный коэффициент.

Дешифратор 15 нуля предназначен для установки преобразователя в исходное состояние при обнулении счетчика 14 формирования аргумента вектора. Когда на выходе счетчика 14 формирования аргумента вектора устанавливается код пуля, на выходе дешифратора 15 нуля вырабатывается положительный импульс, который через второй элемент ИЛИ 17 поступает на вход триггера 9 задания режима и сбрасывает триггер в состояние «О.

Формула изобретения

Устройство для вычисления модуля и аргумента вектора, содержащее генератор тактовых импульсов, счетчик формирования аргумента вектора, дешифратор нуля, триггер задания режима, два элемента ИЛИ и элемент И, причем выход генератора тактовых импульсов соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика формирования аргумента вектора, вход установки триггера задания режима является входом загтуска устройства, отличающееся тем, что, с целью по- вь шения быстродействия, в пего введены два мультиплексора, регистры первого и второго аргументов, два сумматора, счетчик, группа элементов НЕ, три;тер блокировки и формирователь импульсов, причс.м первые информационные входы первого и второго мультиплексоров являются входами абсциссы и ординаты устройства соответственно, вторые информационные входы первого и второго мультп.чексоров соединены с выходами первого и второго сум.маторов соответственно, управляющие входы первого и второго мультиплексоров соединены с Bbj- ходом триггера блокировки, выходы первого и второго мультиплексоров соединены с информационными входами регистров первого и второго аргументов соответственно.

0

5

0

5

0

5

ВЫХОДЫ регистров первого и второго аргументов соединены с входами первых слагаемых первого и второго сумматоров соответственно, выходы (п- К) старпгих разрядов регистров первого и второго аргументов (п - разрядность абсциссы и ординаты; К - нормирующий коэффициент аргумента вектора) соединены с входами (п- К) младщих разрядов входа второго слагаемого второго сумматора и входами элементов НЕ группы соответственно, выходы элементов НЕ группы соединены с входами (п- К) младших разрядов входа второго слагаемого первого сумматора, входы К стар- HJHx разрядов входов вторых слагаемых первого и второго сумматоров соединены с входами (К+1) разрядов вторых информационных входов первого и второго сумматоров соответственно, синхронизирующие входы регистров первого и второго аргументов соединены с выходом первого элемента ИЛИ, первый вход которого соединен с выходом второго разряда счетчика, выходы первого и третьего разрядов которого соединены соответственно с первыми и вторыми входами установки триггера блокировки, выход четвертого разряда счетчика соединен с входом запрещения прохождения тактовых импульсов этого счетчика и вторым входом первого элемента И, выход которого соеди- пен с вторым входом первого элемента ИЛИ, вход сброса счетчика соединен с выходом триггера задания режима, синхровход которого соединен с выходом триггера блокировки, а вход сброса триггера задания режима соединен с выходом второго элемента ИЛИ, первый вход которого через формирователь импульсов соединен с выходом знакового разряда регистра второго аргумента, второй вход второго элемента ИЛИ соединен с выходом дeuJифpaтopa нуля, вход которого сое/чинен с выходом счетчика формирования аргумента вектора, вход блокировки которого соединен с выходом второго разряда счетчика, счетный вход которого соединен с выходом генератора тактовых импульсов, а выходы регистра первого аргумента и счетчика формирования аргумента вектора являются выходами соот- ветствепно модуля и аргумента вектора устройства, выход триггера задания режима является выходом признака завершения вычислений устройства, входы начального кода которого соединены с информационными входами счетчика формирования аргумента вектппа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для преобразования координат | 1989 |

|

SU1695294A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для преобразования координат | 1985 |

|

SU1295386A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

Изобретение относится к вычислительной технике и позволяет сократить время вычисления модуля и аргумента вектора. Устройство содержит первый и второй мультиплексоры 1 и 4, регистры 2 и 5 нер- вого и второго аргументов соответственно, первый и второй сумматоры 3 и 7, группу элементов НЕ 6, генератор 8 тактовы.ч импульсов, триггер 9 задания режима, счетчик 10 управления интегрированием, триггер 11 блокировки, элемент И 12, первый 13 и второй 17 элементы ИЛИ, счетчик 14 формирования аргумента вектора, дешифратор 15 нуля, формирователь 16 импульсов. Значения абсциссы и ординаты вводятся в устройство с входов 22 и 23 абсциссы и ординаты соответственно, а значения модуля и аргумента формируются па выходах 18 и 19 устройства. О завершении вычислений можно судить но появлению сигнала на выходе 20 устройства. I ил. 18 К & (П N3 ;о О1

Ре.чакгор Л. Ворович Заказ 4325;49

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

1 13035. Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления параметров вектора | 1980 |

|

SU943716A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-02—Подача