Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля блоков памяти.

Цель изобретения - повышение быстродействия устройстьа.

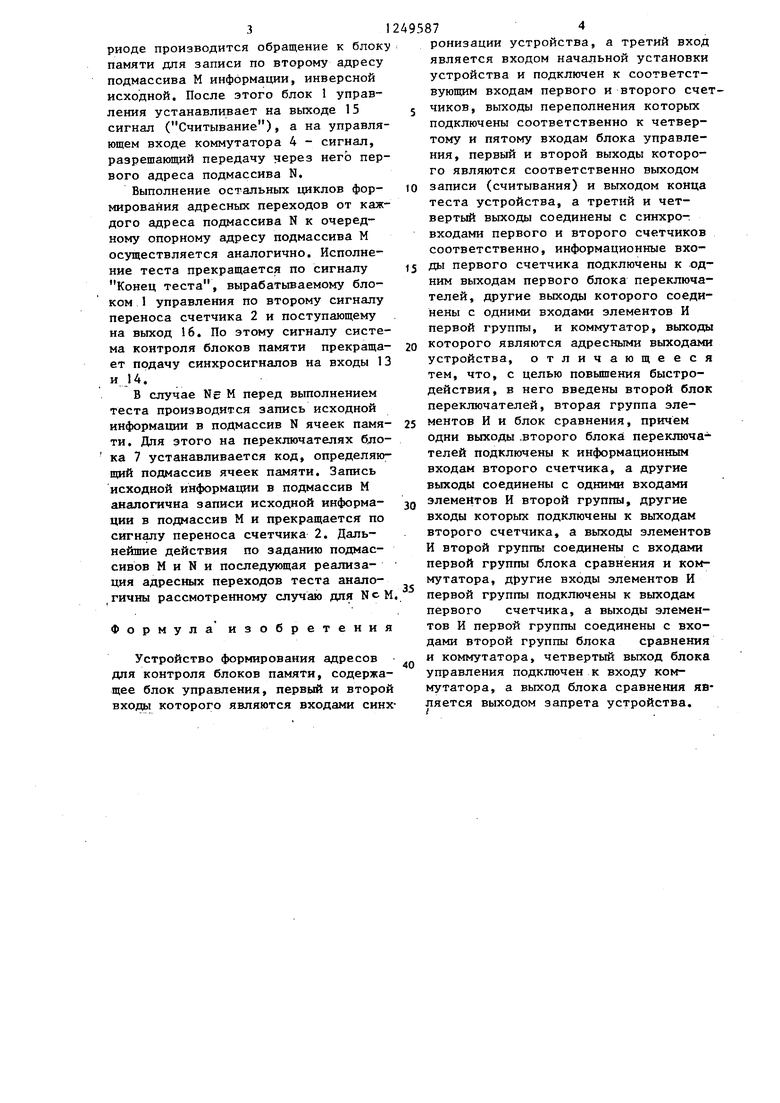

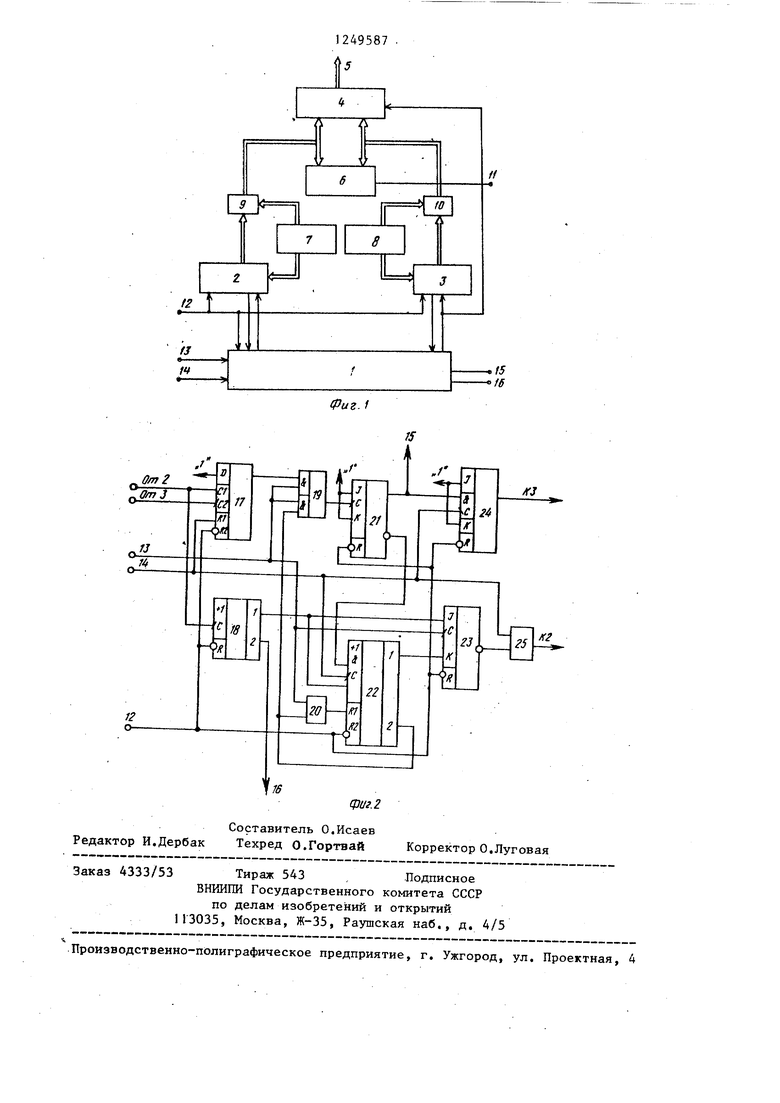

На фиг, I представлена схема устройства формирования адресов для контроля бло.ков памяти; на фиг, 2 - схема блока управления. ,

Устройство (фиг. 1) содержит блок 1 управления, первый 2 и второй 3 счетчики, коммутатор 4, адресные выходы 5, блок 6 сравнения, первый 7 и второй 8 блоки переключателей, первую 9 и. вторую .10 группы злементов И, выход П запрета, вход 12 начальной установки, первый 13 и второй 14 входы синхронизации, выходы записи (считывания) 15 и конца теста 16,

Блок управления (фиг, 2) содержит первый триггер 17, первый счетчик 18 элемент 2И-ИЛИ 19, первый элемент И 20, второй триггер 21, второй счетчик 22, третий 23 и четвертый 24 триггеры и второй элемент И 25.

Устройство работает следующим образом.

Предварительно производится установка педмассивов опорных и текущих адресов М и N, При этом возможны случаи, когда NCM и NcM.B первом случае подмассивы задаются соответственной установкой К-х переключателей блоков 7 и 8 (,.,,,п, где п - разрядность счетчиков 2 и 3) в положение 1, или О, или в нейтральное. При установке переключателей в положение 1 или О соответствующие разряды счетчиков 2 и 3 устанавливаются в состояние 1 или О в соответствии с выбранным положением К-х переключателей, а на входы К-х элементов И групп 9 и 10 подаются соответственно сигналы 1 или О. Нейтральное положение К-х переключателей определяет разряды счетчиков 2 и 3, работающие в счетном режиме и разрешает прохождение сигналов с выходов К-х разрядов счетчиков 2 и 3 через К-е элементы И блоков 9 и 10 на информационные вход коммутатора 4 и блока 6 сравнения.

Згтем на вход 12 подается сигнал начальной установки. При этом разряды счетчиков 2 и .3, определенные дпя работы в счетном режиме, устанавливаются в нулевое состояние, блок 1 управления устанавливает на выходе

5

0

5

0

5

0

5

0

5

15 сигнал Запись, а на управляющем входе коммутатора 4 - сигнал разрешения передачи на выходы 5 кода адреса, формируемого на выходах элементов И группы 9, На входы 13 и 14 синхронизации от системы контроля блоков памяти, в составе которого работает устройство формирования адресов, подаются тактовые импульсы в течение всего теста,

В первом цикле работы счетчика 2 по сигналам блока 1 управления увеличивается содержимое счетчика 2 и на выходы 5 выдается через коммутатор 4 последовательность адресов под- массива М ячеек памяти для записи в них исходной информации теста. После поступления с выхода счетчика 2 сигнала переноса на выходах 5 формируется код первого адреса подмассива М для записи по нему информации, инверсной исходной. Далее блок 1 управления устанавливает на выходе 15 сигнал Считывание, а на управляющем входе коммутатора 4 - сигнал, разрешающий передачу на выходы 5 кода адреса, формируемого на выходах элементов И группы 10,

Далее устройство выполняет первый цикл формирования адресных переходов , в котором осуществляются переходы от каждого адреса подмассива к первому адресу подмассива М, Дпя этого в каждом периоде обращения к блоку памяти блок 1 управления меняет уровень сигнала на управлякицем входе коммутатора 4, в соответствии с чем на выходы 5 через коммутатор 4 поочередно поступают коды адресов подмассивов М и N, По спаду сигнала блока управления, поступающего на счетный вход счетчика 3, увеличивается его содержимое.

Блок 6 сравнения при наличии равенства кодов на его входах вырабаты,- вает на выходе 11 сигнал, запрещающий в устройстве контроля останов по несравнению считанной с одинаковых адресов информации. После поступления сигнала переноса счетчика 3 блок 1 управления устанавливает на выходе 15 сигнал Запись, а на уп- равляюшем входе коммутатора 4 - сигнал разрешения передачи через него адреса подмассива М для записи исходной информации по первому адресу подмассива М, после чего по сигналу блока 1 управления увеличивается содержимое счетчика 2. В следующем периоде производится обращение к блоку памяти для записи по второму адресу подмассива М информации, инверсной исходной. После этого блок 1 управления устанавливает на выходе 15 5 сигнал (Считывание), а на управляющем входе коммутатора 4 - сигнал, разрещающий передачу через него первого адреса подмассива N.

Выполнение остальных циклов фор- 10 мирования адресных переходов от каждого адреса подмассива N к очередному опорному адресу подмассива М осуществляется аналогично. Исполнение теста прекращается по сигналу 15 Конец теста, вырабатываемому блоком 1 управления по второму сигналу переноса счетчика 2 и поступающему на выход 16. По этому сигналу система контроля блоков памяти прекраща- 20 ет подачу синхросигналов на входы 13 и 14.

В случае NC М перед выполнением теста производится запись исходной информации в поДмассив N ячеек памя- 25 ти. Для этого на переключателях бло- ка 7 устанавливается код, определяющий подмассив ячеек памяти. Запись исходной информации в подмассив М аналогична записи исходной информа- зо ции в подмассив М и прекращается по сигналу переноса счетчика 2. Дальнейшие действия по заданию подмас- сивов М и N и последующая реализация адресных переходов теста анало- гичны рассмотренному случаю для NC.M.

35

Формула изобретения

Устройство формирования адресов для контроля блоков памяти, содержащее блок управления, первый и второй входа которого являются входами синх5

0 5 0

5 о

ронизации устройства, а третий вход является входом начальной установки устройства и подключен к соответствующим входам первого и второго счетчиков, выходы переполнения которых подключены соответственно к четвертому и пятому входам блока управления, первый и второй выходы которого являются соответственно выходом записи (считывания) и выходом конца теста устройства, а третий и четвертый выходы соединены с синхро- входами первого и второго счетчиков соответственно, информационные входы первого счетчика подключены к одним выходам первого блока переключателей, другие ВЕлходы которого соединены с одними входами элементов И первой группы, и коммутатор, выходы которого являются адресными выходами устройства, отличающееся тем, что, с целью повыщения быстродействия, в него введены второй блок переключателей, вторая группа элементов И и блок сравнения, причем одни выходы .второго блока переключателей подключены к информационным входам второго счетчика, а другие выходы соединены с одними входами элементов И второй группы, другие входы которых подключены к выходам второго счетчика, а выходы элементов И второй группы соединены с входами первой группы блока сравнения и коммутатора, другие входы элементов И первой группы подключены к выходам первого счетчика, а выходы элементов И первой группы соединены с входами второй группы блока сравнения и коммутатора, четвертый выход блока управления подключен к входу коммутатора, а выход блока сравнения является выходом запрета устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство подсчета кодов | 1987 |

|

SU1534457A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1133622A1 |

| Устройство для поиска данных | 1989 |

|

SU1658170A2 |

| Система упорядочения информации | 1975 |

|

SU608161A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля блоков памяти. Целью изобретения является повьшение быстродействия. Устройство содержит блок управления, первый и второй счетчики, блок сравнения, первый и второй блоки переключателей, коммутатор, первую и вторую группы элементов И, В устройстве обеспечивается формирование адресных последовательностей для динамических тестов типа Галоп с возможностью управления подмассива- ми текущих и опорных адресов, задаваемых соответственно первым и вторым блоками переключателей. При совпадении текущего и опорного адресов блок сравнения выдает сигнал запрета останова во внешнюю систему контроля. 2 ил. (/ С ел 00

Редактор И.Дербак

Составитель О.Исаев Техред О.Гортвай

Заказ 4333/53 Тираж 543.Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор О.Луговая

| Устройство формирования адресов для контроля блоков памяти | 1977 |

|

SU665330A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Разработка полупроводниковых оперативных запоминающих устройств |И пульта для их контроля и наладки | |||

| Отчет ЮИ | |||

| / Руководитель работы Ю.М.Шамаев, № гос | |||

| Буквопечатающий телеграфный аппарат | 1933 |

|

SU34017A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1986-08-07—Публикация

1984-06-13—Подача