I

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и является усовершенствованием изобретения по авт. св. № 1051585.

Цель изобретения - повышение достоверности контроля.

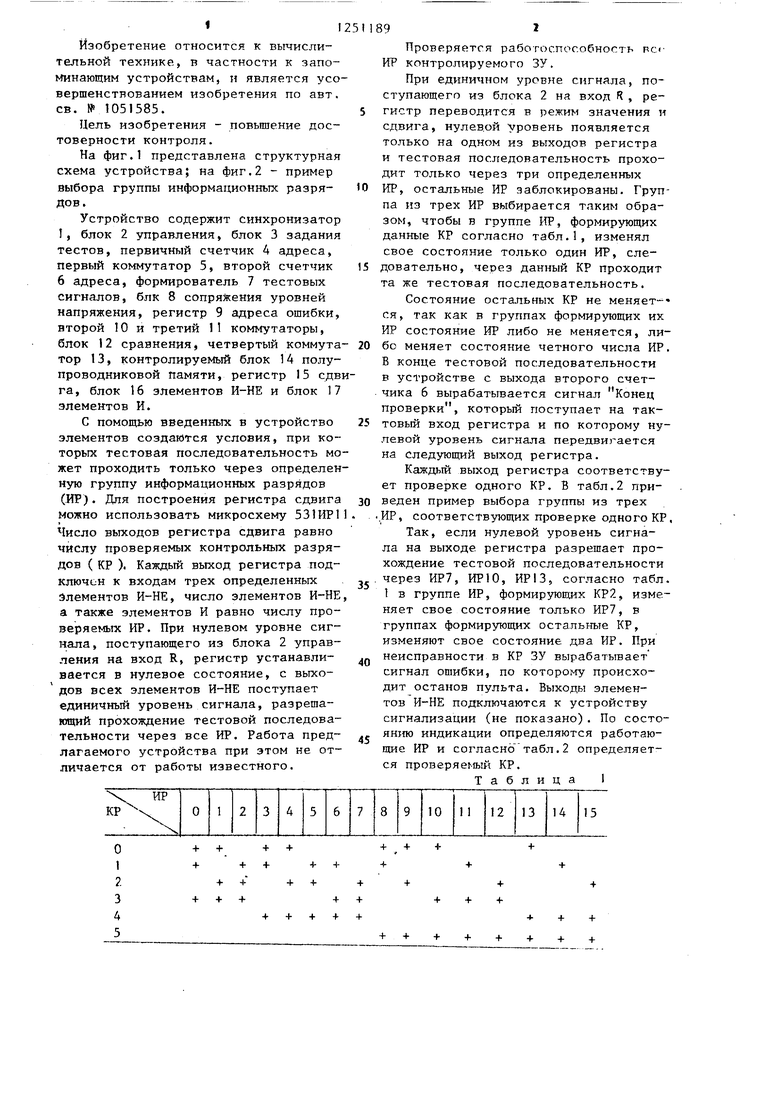

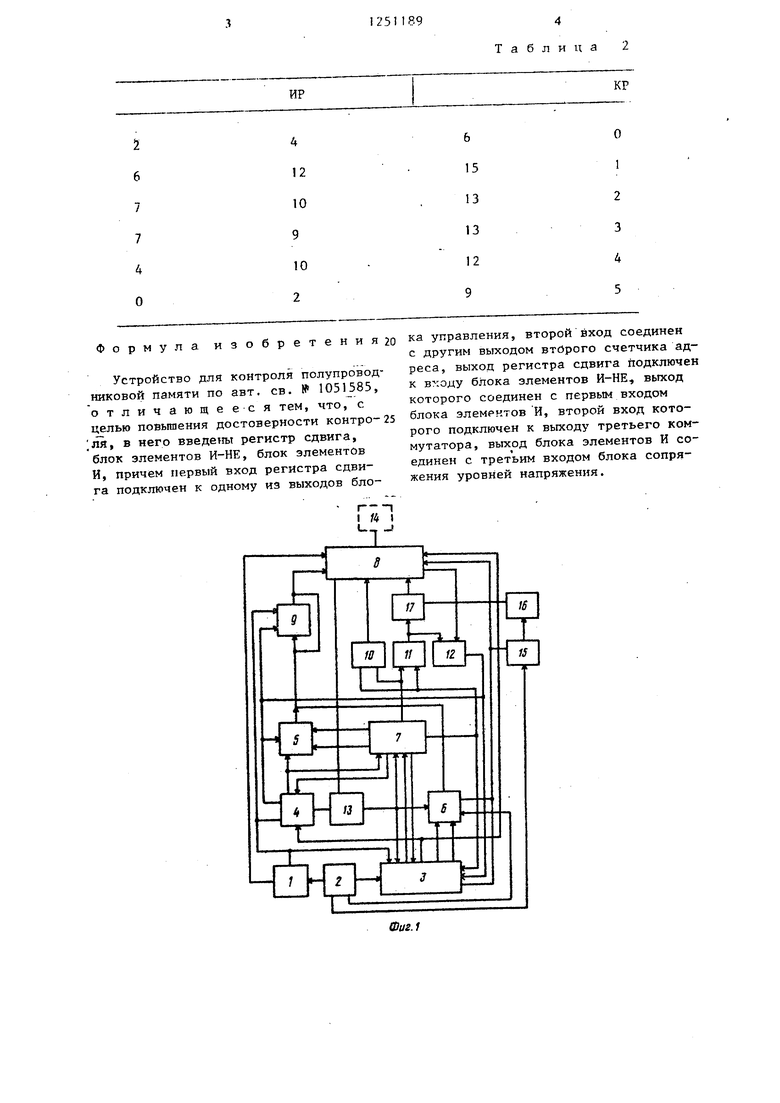

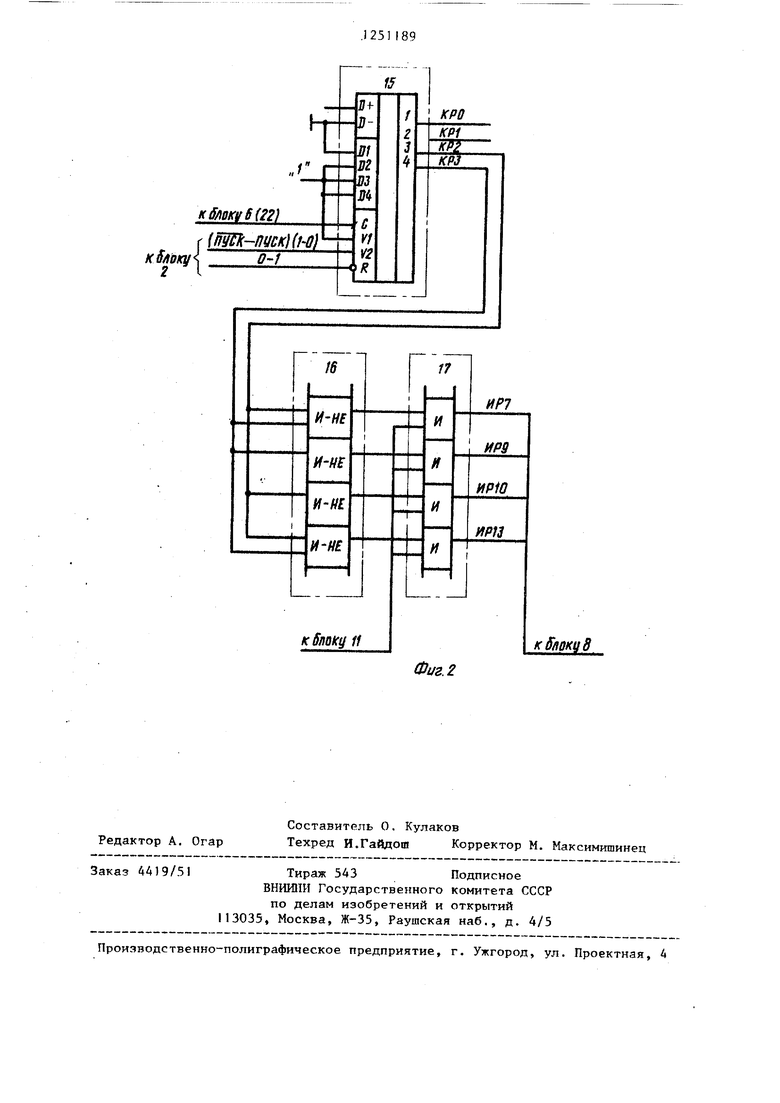

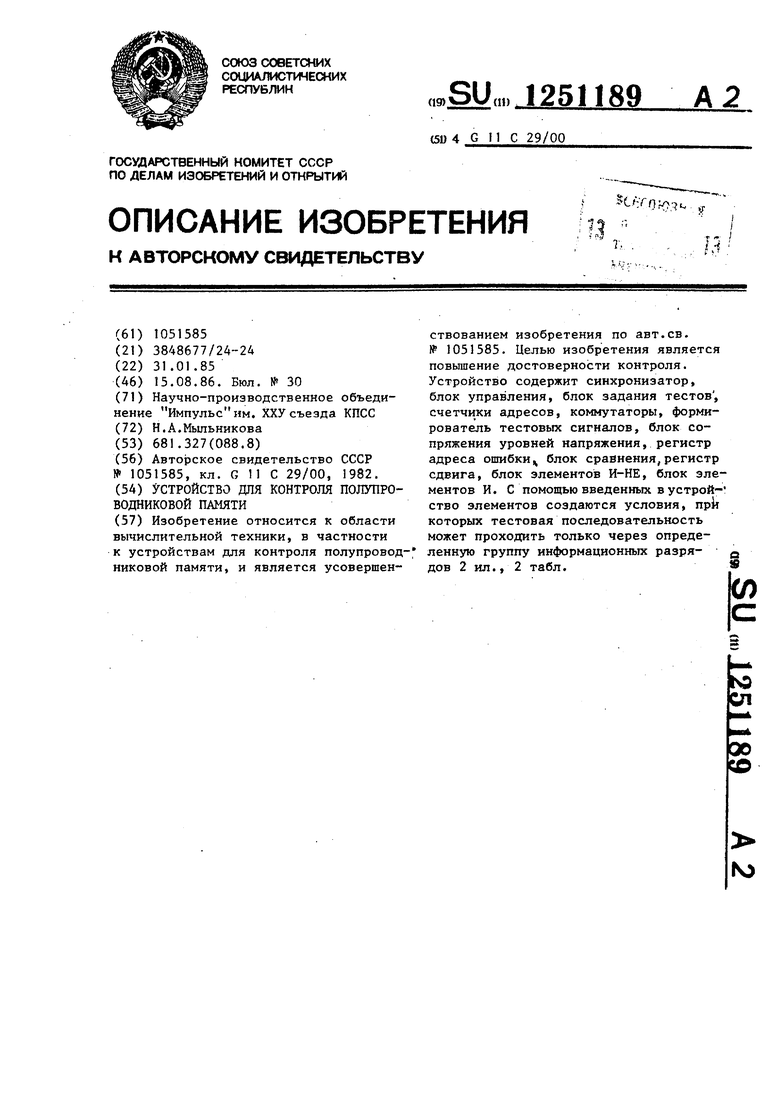

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример выбора группы информационных разря- дов.

Устройство содержит синхронизатор I, блок 2 управления, блок 3 задания тестов, первичный счетчик 4 адреса, первый коммутатор 5, второй счетчик 6 адреса, формирователь 7 тестовых сигналов, блк 8 сопряжения уровней напряжения, регистр 9 адреса ошибки, второй 10 и третий 11 коммутаторы, блок 12 сравнения, четвертый коммута тор 13, контролируемый блок 14 полупроводниковой памяти, регистр 15 сдвга, блок 16 элементов И-НЕ и блок 17 элементов И.

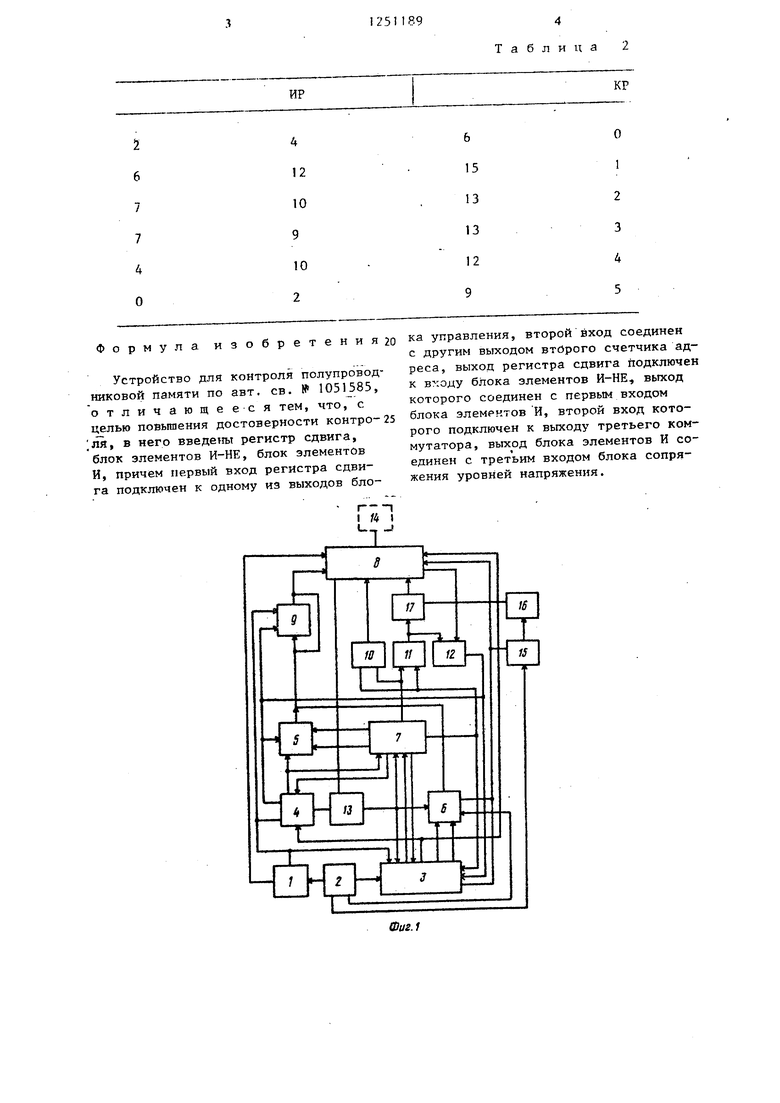

С помощью введенных в устройство элементов создаются условия, при которых тестовая последовательность может проходить только через определенную группу информационных разрядов (ИР). Для построения регистра сдвига можно использовать микросхему 53ШР1 Число выходов регистра сдвига равно числу проверяемых контрольных разрядов ( КР ). Каждый выход регистра подключен к входам трех определенных элементов И-НЕ, число элементов И-НЕ а также элементов И равно числу проверяемых ИР. При нулевом уровне сигнала , поступающего из блока 2 управления на вход R, регистр устанавли- вается в нулевое состояние, с вьтхо- дов всех элементов И-НЕ поступает единичный уровень сигнала, разреша- няций прохождение тестовой последовательности через все ИР. Работа пред- лагаемого устройства при этом не отличается от работы известного.

+ ++ + + , + + ч- +

++ + + + +

+ ++ + +

f ч- + + +

+ +

9I

Проверяется работоспособность во- ИР контролируемого ЗУ.

При единичном уровне сигнала, поступающего из блока 2 на вход R, регистр переводится в режим значения и сдвига, нулевой уровень появляется только на одном из выходов регистра и тестовая последовательность проходит только через три определенных ИР, остальные ИР заблокированы. Группа из трех ИР выбирается таким образом, чтобы в группе ОТ, формирующих данные КР согласно табл. 1, изменял свое состояние только один ИР, слеовательно, через данный КР проходит а же тестовая последовательность.

Состояние оста.пьных КР не меняет- ся, так как в группах формирующих их ИР состояние ИР либо не меняется, либо меняет состояние четного числа ИР. Б конце тестовой последовательности в устройстве с выхода второго счетчика 6 вырабатывается сигнал Конец проверки, который поступает на тактовый вход регистра и по которому нулевой уровень сигнала передвигается на следующий выход регистра.

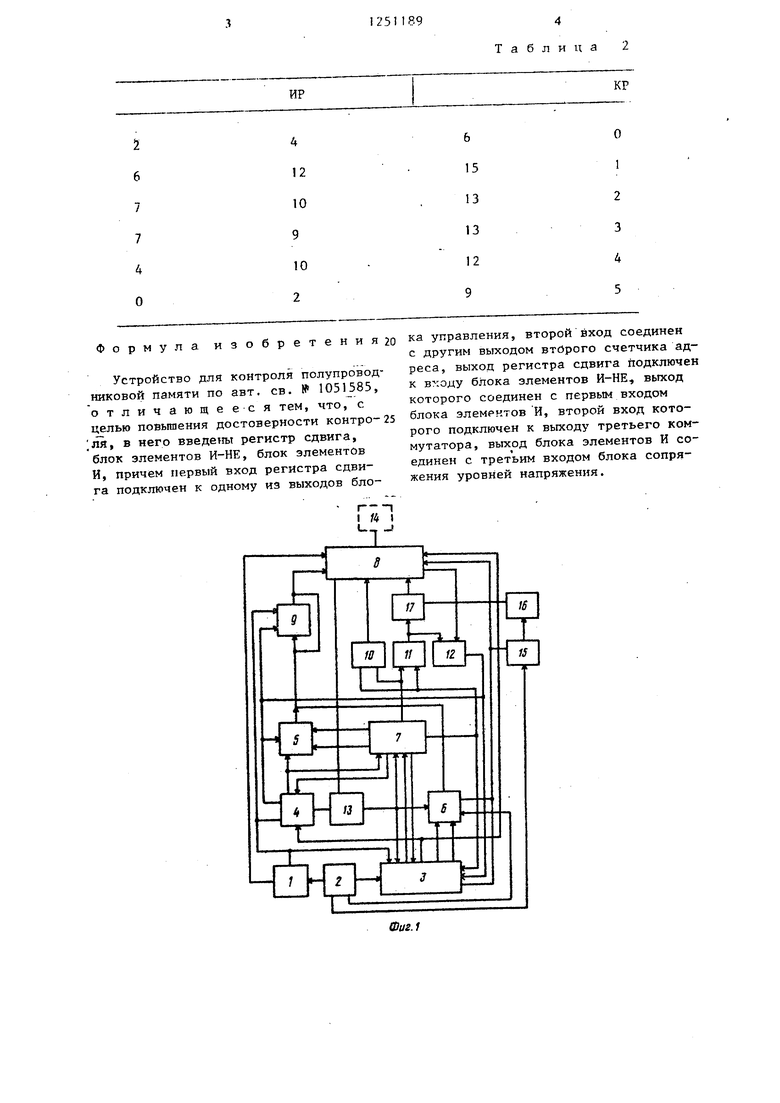

Каждый выход регистра соответствует проверке одного КР. В табл.2 приведен пример выбора группы из трех ИР, соответствующих проверке одного КР.

Так, если нулевой уровень сигнала на выходе, регистра разрешает прохождение тестовой последовательности через ИР7, ИР 10, ИР 13,, согласно табл. 1 в группе ИР, формирующих КР2, изменяет свое состояние только ИР7, в группах формирующих остальные КР, изменяют свое состояние два ИР. При неисправности в КР ЗУ вырабатывает сигнал ошибки, по которому происходит останов пульта. Выходы элементов И-НЕ подключаются к устройству сигнализации (не показано). По состоянию индикации определяются работающие ИР и согласно табл.2 определяется проверяемый КР.

Таблица 1

+

4-f +

+ +

+ +

ИР

Формула изобретения 20

Устройство для контроля полупроводниковой памяти по авт. св. № , отличающееся тем, что, с целью повышения достоверности контро-25 ;ля, в него введены регистр сдвига, блок элементов И-НЕ, блок элементов И, причем первый вход регистра сдвига подключен к одному из выходов блоTftl

с.

Таблица 2

КР

ка управления, второй вход соединен с другим выходом второго счетчика адреса, выход регистра сдвига подключен к входу блока элементов И-НЕ, выход которого соединен с первым входом блока элементов И, второй вход которого подключен к выходу третьего коммутатора, выход блока элементов И соединен с третьим входом блока сопряжения уровней напряжения.

кбЛикубЩ

f ()

KSAOKU

г l -

0-J

16

И-Hf

И-ffE

и HE

кбяокди

Редактор А. Огар

Составитель О. Кулаков

Техред И.Гайдош Корректор М. Максимишинец

44)9/51

Тираж 543Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

КРО

KP1

KP2

TfAT

1

ИР7

и

и

tfpf3

и

/cS/iOKi/3

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля логическихблОКОВ | 1979 |

|

SU842821A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1403097A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам для контроля полупровод- никовой памяти, и является усовершенствованием изобретения по авт.св. № 1051585. Целью изобретения является повьшение достоверности контроля. Устройство содержит синхронизатор, блок управления, блок задания тестов , счетчики адресов, коммутаторы, формирователь тестовых сигналов, блок сопряжения уровней напряжения, регистр адреса ошибки блок сравнения,регистр сдвига, блок элементов И-НЕ, блок элементов И. С помощью введенных в устрой- ство элементов создаются условия, при которых тестовая последовательность может проходить только через определенную группу информационных разря- g дов 2 ил., 2 табл. ISO

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-31—Подача