Нз(1Гн5ет( относится к вычислите jibnoii технике и может быть ис- польтонано juiH контроля, испытания и наладки дискретной аппаратуры, требуюпкч для своего функционирования упрлрллющих воздействий, подаваемых в реальном масштабе времени, например, работающей в составе авто- МсП изироплиной системы управления 6b.v. т ро протекающим и технологическими пронес .

Цель изобретения - повьшюние быстро;1е1:ствия устройства .

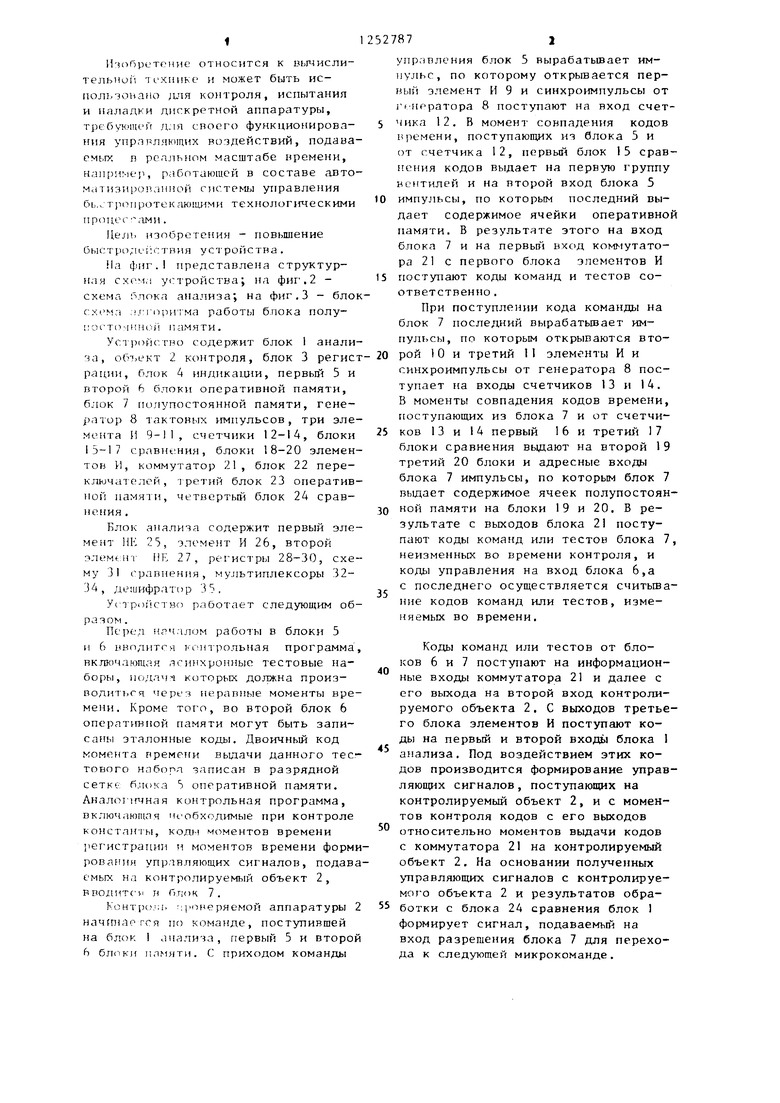

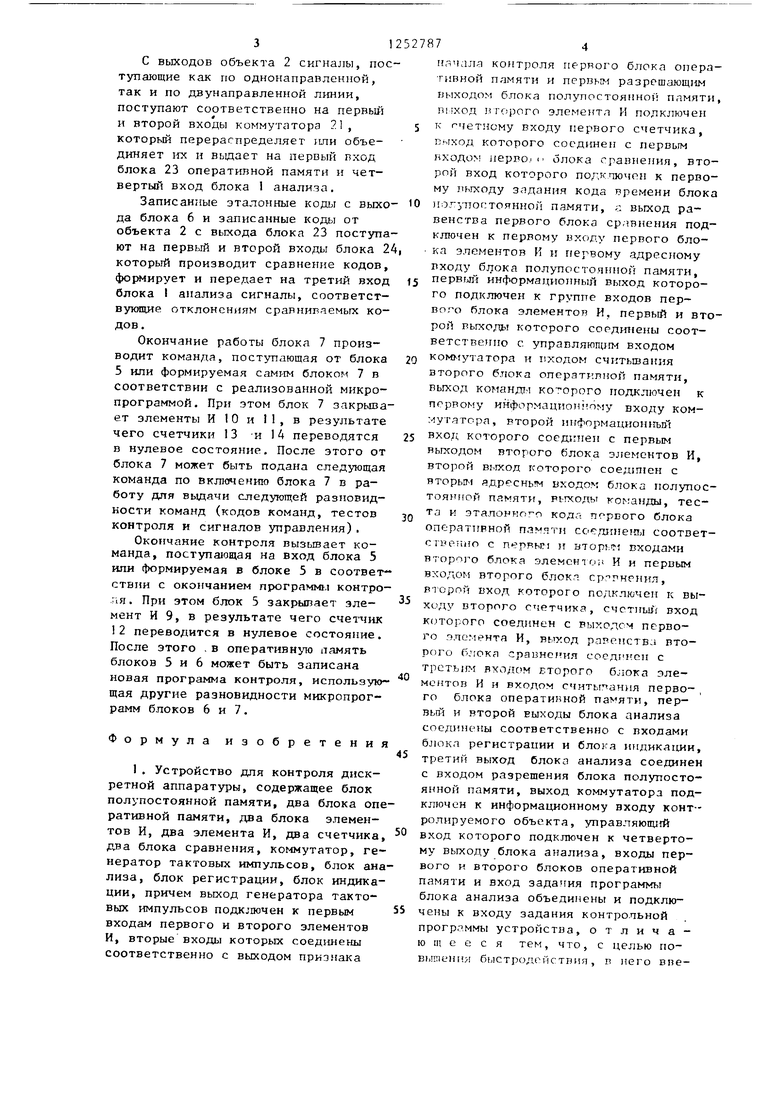

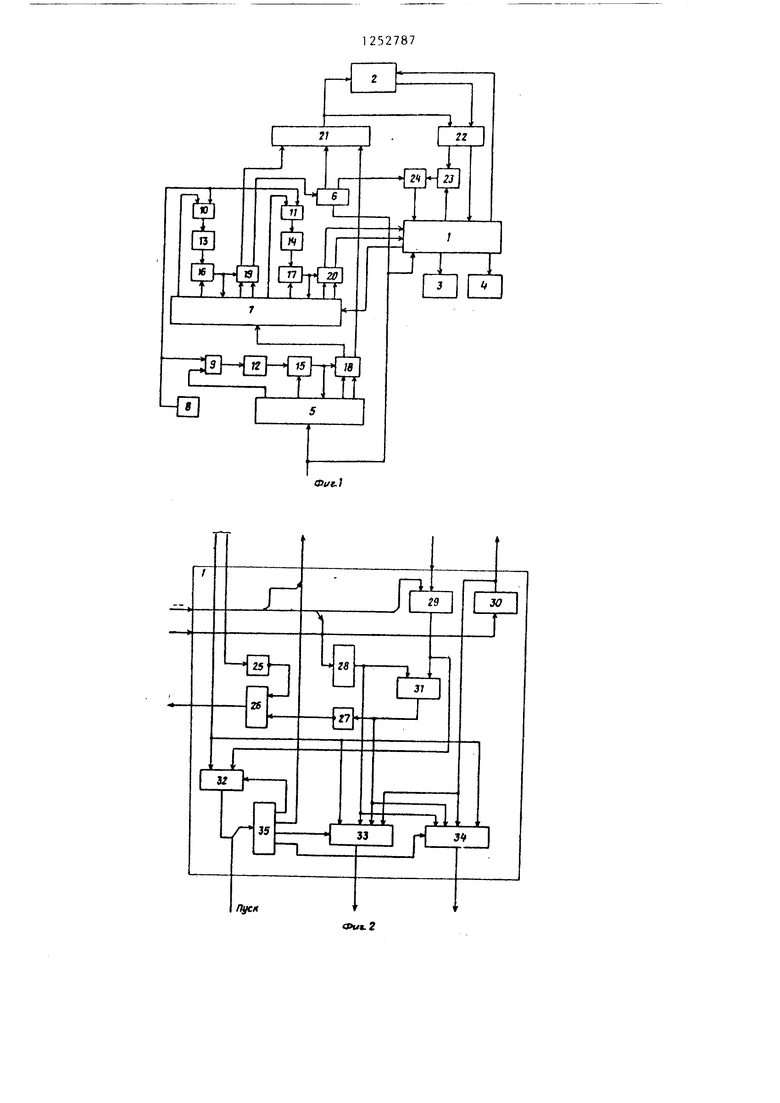

На фиг.I представлепа структурная схем, устройства; па фиг, 2 - схема Гхпока анализа; на фиг, 3 - блок с хем:) ,.г:гпрн ма работы блока полу- ; о I т о м I н { : 11 11 амяти.

Ус1ройство содержит блок 1 анали- ча, об7)ект 2 контроля, блок 3 регист рации, 4 индикащш, первый 5 и второй 6 блоки оперативной памяти, блок 7 полупостоянной памяти, генератор 8 тактовых импульсов, три элемента И 9-11, счетчики 12-14, блоки 15-17 сравнения, блоки 18-20 элементов И, коммутатор 21, блок 22 переключателей , третий блок 23 оперативной памяти, четвертый блок 24 сравнения ,

Блок анализа содержит первый элемент НЕ 25, элемент И 26, второй элем(;и | liE 27, регистры 28-30, схему 31 сравнения, мультиплексоры 32- 3 4 , д е ишфр а тор 3 5 .

У( ipoi iCTBo работает следующим образом .

Перед началом работы в блоки 5

и 6 вводится ч нтрольная программа вклк1чающая асинхронные тестовые наборы, подач которых должна произ- водитт)Ся через неравные моменты времени. Кроме того, во второй блок 6 операт Ю 1ой памяти могут быть записаны эталонные коды. Двоичный код момента времени выдачи данного тестового набора записан в разрядной сетко: блока S оперативной памяти. Лнадопгчная контрольная программа, включающая и обход1тмые при контроле константы, коды моментов времени регистрации и моментов времени форми ровар ия управляющих сигналов, подаваемых на контролируемый объект 2,

ВВОДИТС1 н блок 7.

Контро, :, ряемой аппаратуры 2 нач(П)аргся по команде, поступившей на бл(5к I анализа, первый 5 и второй Ь блпки памяти. С приходом команды

527871

управления блок 5 вырабатьшает импульс, по которому открьшается первый элемент И 9 и синхроимпульсы от i f-нератора 8 поступают на вход счет5 чика 12. В момент совпадения кодов времени, поступающих из блока 5 и от счетчика 12, первьаЧ блок 15 сравнения кодов выдает на первую группу вентилей и на второй вход блока 5

10 импульсы, по которым последний выдает содержимое ячейки оперативной памяти. В результате этого на вход блока 7 и на первый вхс д коммутатора 21 с первого блока элементов И

15 поступают коды команд и тестов соответственно.

При поступлении кода команды на блок 7 последний вырабатьшает импульсы, по которым открываются вто- 20 рой to и третий II элементы И и

синхроимпульсы от генератора 8 поступает на входы счетчиков 13 и 14. В моменты совпадения кодов времени, поступающих из блока 7 и от счетчи25 ков 13 и 14 первый 16 и третий 17 блоки сравнения выдают на второй 19 третий 20 блоки и адресные входы блока 7 импульсы, по которым блок 7 выдает содержимое ячеек полупостоян30 ной памяти на блоки 19 и 20. В результате с выходов блока 21 поступают коды команд или тестов блока 7, неизменных во времени контроля, и коды управления на вход блока 6,а с последнего осуществляется считывание кодов команд или тестов, изменяемых во времени.

35

Коды команд или тестов от блоков 6 и 7 поступают на информационные входы коммутатора 21 и далее с его выхода на второй вход контролируемого объекта 2. С выходов третьего блока элементов И поступают коды на первый и второй входь блока 1 анализа. Под воздействием этих кодов производится формирование управляющих сигналов, поступающих на контролируемый объект 2, и с моментов контроля кодов с его выходов относительно моментов выдачи кодов с коммутатора 21 на контролируемый объект 2. На основании полученных ут1равляющих сигналов с контролируе- мог о объекта 2 и результатов обра- ботки с блока 24 сравнения блок 1 формирует сигнал, подаваеьлй на вход разрешения блока 7 для перехода к следующей микрокоманде.

С выходов объекта 2 сигналы, поступающие как по однонаправленной, так и по двунаправленной линии, поступают соответственно на первый и второй входы коммутатора 21, который перераспределяет или объединяет 1-гх и вьщает на первый вход блока 23 оперативной памяти и чет- вертьо вход блока 1 анализа.

Записанные эталонные коды с выхода блока 6 и записанные коды от объекта 2 с выхода блока 23 поступают на первый и второй входы блока 24 который производит сравнение кодов, формирует и передает на третий вход блока I анализа сигналы, соответствующие отклонениям сравниваемых кодов.

Окончание работы блока 7 производит команда, поступающая от блока 5 или формируемая самим блоком 7 в соответствии с реализованной микропрограммой. При этом блок 7 закрьша- ет элементы И 10 и 11, в результате чего счетчики 13 и 14 переводятся в нулевое состояние. После этого от блока 7 может быть подана следующая команда по включению блока 7 в работу для выдачи следующей разновидности команд (кодов команд, тестов контроля и сигналов управления).

Окончание контроля вызьшает команда, поступающая на вход блока 5 или формируемая в блоке 5 в соответствии с окончанием программ, контро- пя. При этом блок 5 закрывает элемент И 9, в результате чего счетчик 12 переводится в нулевое состояние. После этого . в оперативную память блоков 5 и 6 может быть записана новая программа контроля, использук щая другие разновидности микропрограмм блоков 6 и 7.

Формула изобретения

1. Устройство для контроля дискретной аппаратуры, содержащее блок полупостоянной памяти, два блока оперативной памяти, два блока элементов И, два элемента И, два счетчика, два блока сравнения, коммутатор, генератор тактовых нлтульсов, блок анализа, блок регистрации, блок индикации, причем выход генератора тактовых импульсов подключен к первым входам первого и второго элементов И, вторые входы которых соед 1нены соответственно с выходом признака

нячала контроля первого блока оперативной памяти и первым разрешающ1-1м выходом блока полупостоянноГ памяти, пиход л горого элемент И подключен

5 к гчетному входу первого счетчика, выход которого соединен с первым Бходо Jieppoji блока сравнения, второй вход которого подключен к первому льгходу злдания кода времени блока

0 11о,г,1тостоянной памяти, а выход равенства первого блока ср-1внения подключен к первому входу первого бло- ка элементов И и первому адресному

входу блока полупостоянной памяти, 2 информационный выход которого подключен к группе входов первого блока элементов И. первый и второй выходы которого соединены соот- ветствеипо с управляющим входом 3 комк утатора и пходом считывания второго блока операт шиой памяти, выход команд которого подключен к первому информац11он ому входу коммутатора, второй информационный 5 вход которого соединен с первым

выходом второго блока элементов И, второй вьжод гсоторого соедшген с яторьи ядресньтм входом блока полупос- тояниой памяти, РЪГХОДЫ команды, теста и эталорко о кодг; первого блока оператпрной памяти со«;д1П егал соответ- стиенио с первым л вторТ; входами второго блока элемснтг.и И и первым

входом второго бЛОК,1 CpTHPflHn,

Я1орой вход которого подключеп к вы- хи;;у второго счетчика, счстпш вход к(,1торого соединен с выходом первого элемента И, выход рарел ства второго блекл сравноиия соедрг сп с третьим входом Еторого блока эле- ментон И и входом считы ания перво- , го блока оперативной памяти, первый и второй выходы блока анализа соединены соответственно с входами блокл регистрации и блока индикации, третий выход блока анализа соединен с входом разрешения блока полупосто- яиной памяти, выход коммутатора подключен к информационному входу конт-- ролируемого объекта, управляющий вход которого подключен к четвертому выходу блока анализа, входы первого и второго блоков оперативной памяти и вход задания программы блока анализа объединены и подклкг- 5 чены к входу задания контрольной

программы устройстна, отличающееся тем, что, с целью повышенна б,1стродойствия, в него впе0

5

0

5

0

дены блок переключателей, третий блок оперативной памяти, третий счетчик, третий и четвертый блоки сравнения, третий элемент И, третий блок элементов И, причем первый и второй входы третьего элемента И соединены соответственно с вторым разрешающим выходом блока полупостоянной памяти и выходом генератора тактовых импульсов, выход третьего элемента И подключен к счетному входу третьего счетчика, выход которого соединен с первым входом третьего блока сравнения, второй вход которого подключен к второму выходу задания кода времени блока полупостоянной памяти, выход равенства третьего блока сравнения подключен к входу третьего блока элементов И и третьему адресному входу блока полу- постояниой памяти, второй информационный выход которого соединен соответственно с группой входов третьего блока элементов И, первый и второй вькоды которого соединены с пер вьм и вторым информационными входами блока анализа соответственно, разрешающий вход блока анализа соединен с выходом равенства четвертого бло ка сравнения, первый вход которого соединен с выходом эталонов второго блока оперативной памяти, второй вход четвертого блока сравнения соединен с выходом третьего блока оперз тивной памяти, информационный вход которого соединен с первым выходом блока переключателей, второй выход которого соединен с третьим информа- ционньм входом блока анализа, первый и второй информационные входы блока переключателей соединены с входом и выходом контролируемого объекта, вход режима третьего блока оперативной памяти подключен к пятому выходу блока анализа.

2. Устройство по п. 1 , о т л и ч а ю щ е е с я тем, что блок анализа содержит три регистра, схему сравне ния, элемент И, два элемента НЕ, дешифратор и три мультиплексора, при

527876

чем вход первого элемента НЕ и управляющий вход первого мультиплексора образуют разрешающий вход блока, выход первого элемента НЕ соединен с первым входом элемента И, второй вход элемента И через второй элемент НЕ подключен к выходу сравнения схемы сравнения, первый и второй входы которой соединены соответственно с ;

10 Выходами первого и второго регистров, информащюнный вход первого регистра и первый информационный вход второго регистра образуют первый информационный вход блока, информа15 ционный вход третьего регистра является вторым информационные входом блока, первые информационные входы второго и третьего мультиплексоров объединены и подключены к выходу пер20 вого регистра, вторые информационные входы второго и третьего мультиплексоров объединены и подключены к выходу схемы сравнения, третьи информационные входы второго и третьего 25 мультиплексоров объединены и подключены к выходу третьего регистра , выход третьего регистра является четвертым выходом блока, первый информационный вход.первого мультиплексора

2Q соединен с выходом второго регистра,

первый, второй, третий выходы дешиф ратора соединены соответственно с вторым информационным входом первого мультиплексора, четвертым информационным входом второго и четвертым инфо1 1а- ционным входом третьего мультиплексоров , четвертый выход дешифратора является пятьвч выходом блока, выходы второго и третьего мультиплексо- .- ров являются соответственно первым и вторым выходами блока, выход элемента И является третьим выходом блока, второй информационный вход второго регистра является третьим информационным входом блока, управ35

45

лякхцие входы первого, второго и третьего мультиплексоров объединены, выход первого мультиплексора подключен к входу дешифратора и является входом задания программы блока.

г

22

0

I

J3

I

« T-4 e

гч 23

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| УСТРОЙСТВО ДЛЯ ТЕЛЕУПРАВЛЕНИЯ И ТЕЛЕСИГНАЛИЗАЦИИ | 1995 |

|

RU2111545C1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Устройство для контроля дискретных объектов | 1987 |

|

SU1539781A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство программного управления роботами гальванической линии | 1983 |

|

SU1124250A1 |

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

Изобретение предназначено для контроля испытания и наладки дискретной аппаратуры. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство, содержащее генератор тактовых импульсов, блок анализа, блоки регистрации и индикации, два блока оперативной Iпамяти, блок полупостоянной памяти, два счетчика, две схемы сравнения, два блока элементов И, два злемента И, коммутатор, введены третий блок элементов И, третий элемент И, третья и четвертая схемы сравнения, третий блок оперативной памяти. 1 з.п. ф-лы, 3 ил.

и -H 15 I

Jo;

л;

35

ч ЗЗП pi 34.

РигЗ

Редактор В.Петраш

Составитель И.Сафронова

Техред в. КадарКорректор Е. Сирохман

Заказ 4621/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССГ

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для контроля цифровых узлов | 1977 |

|

SU643876A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дискретной аппаратуры | 1978 |

|

SU792259A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1984-03-13—Подача