Изобретение относится к вычислительной технике и может быть использовано при построении специализированных процессоров. ,

Целью изобретения является расширение класса решаеь4.1х задач за счет возможности вычисления гиперболических функций синуса и косинуса комплексного переменного.

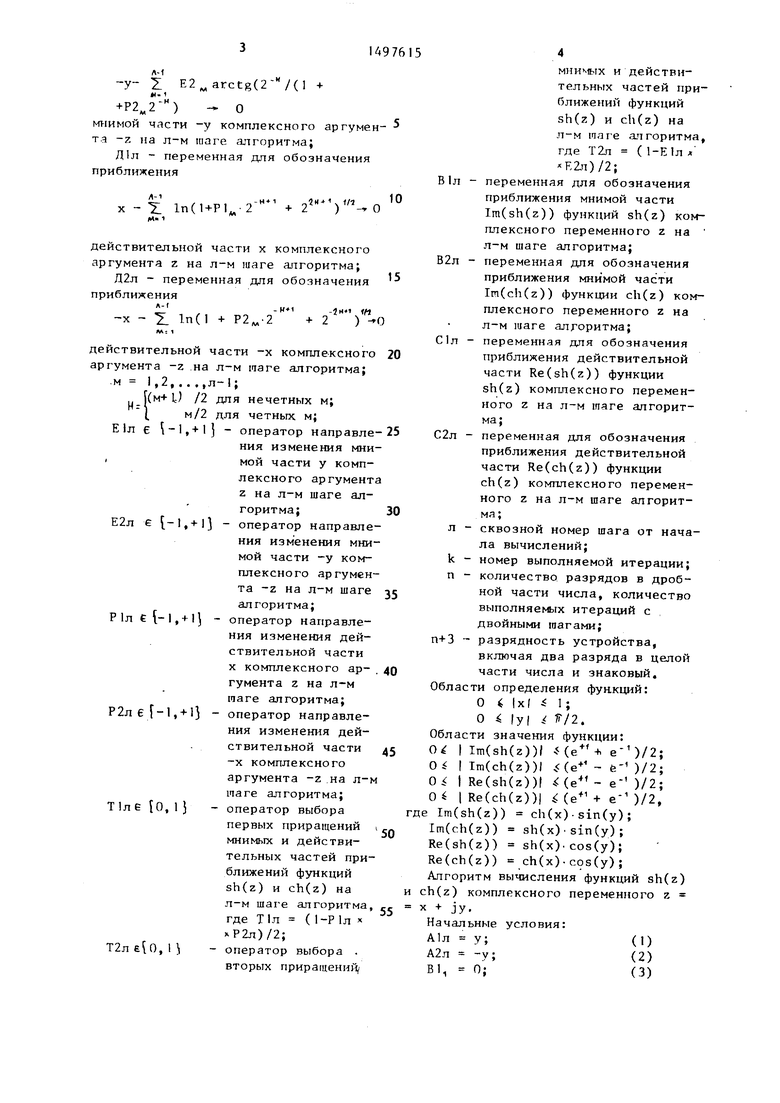

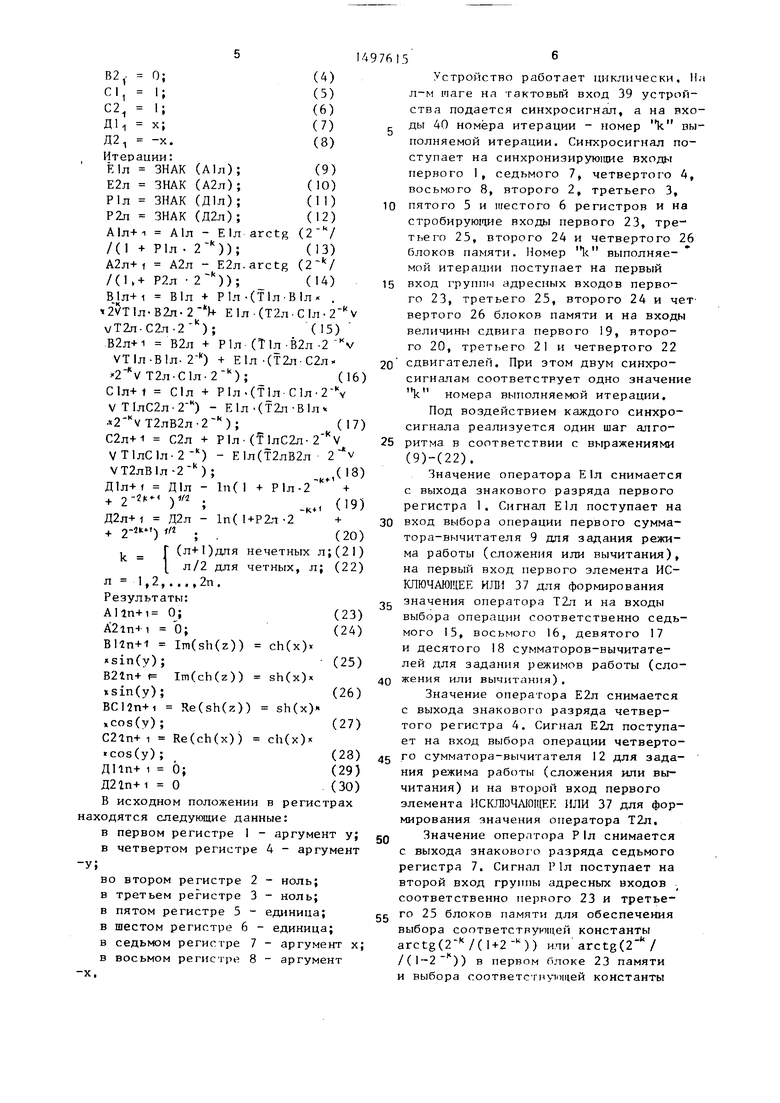

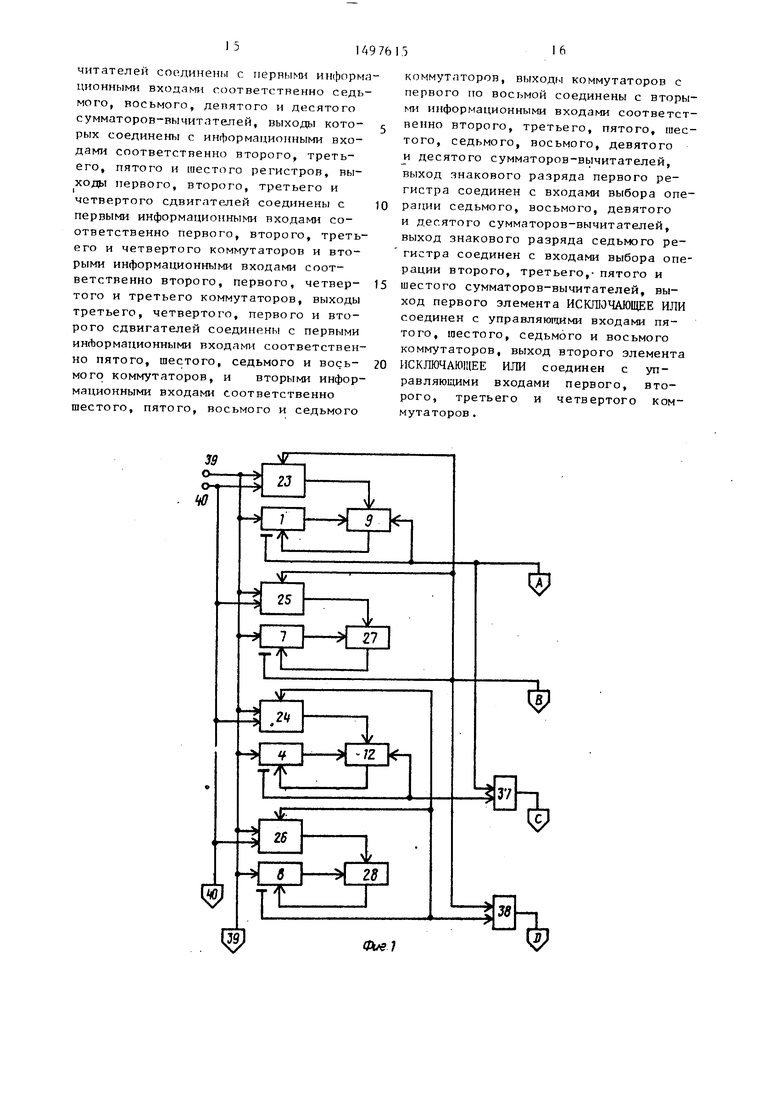

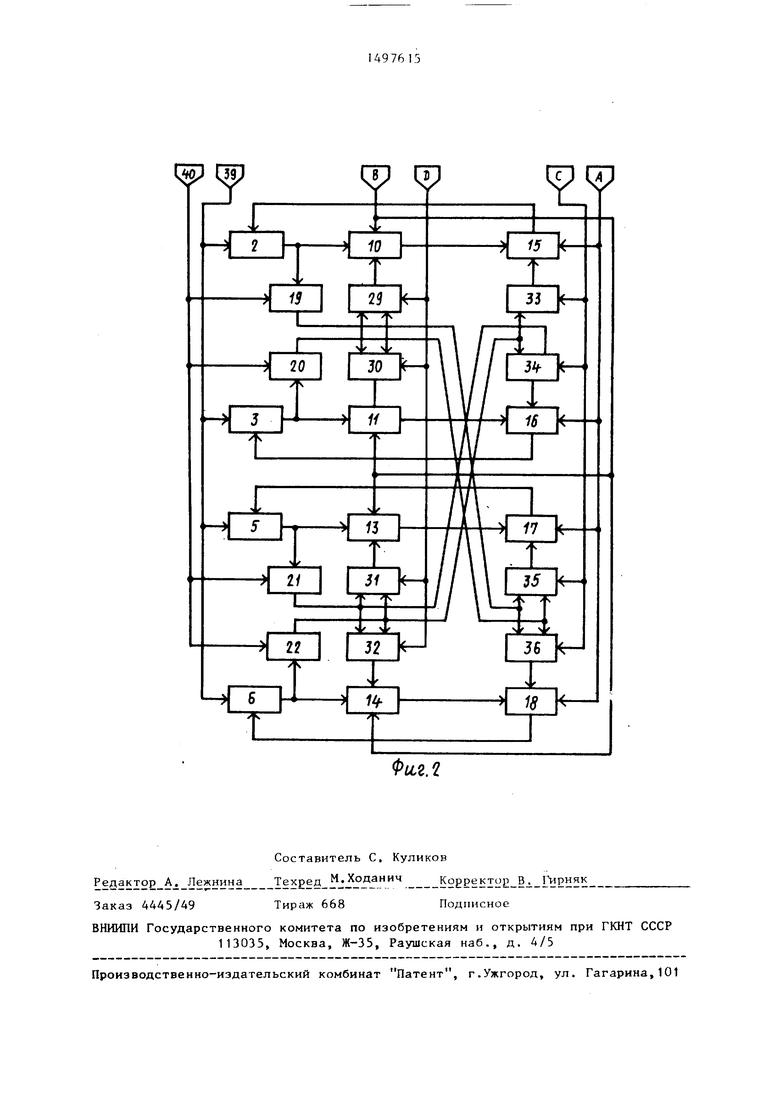

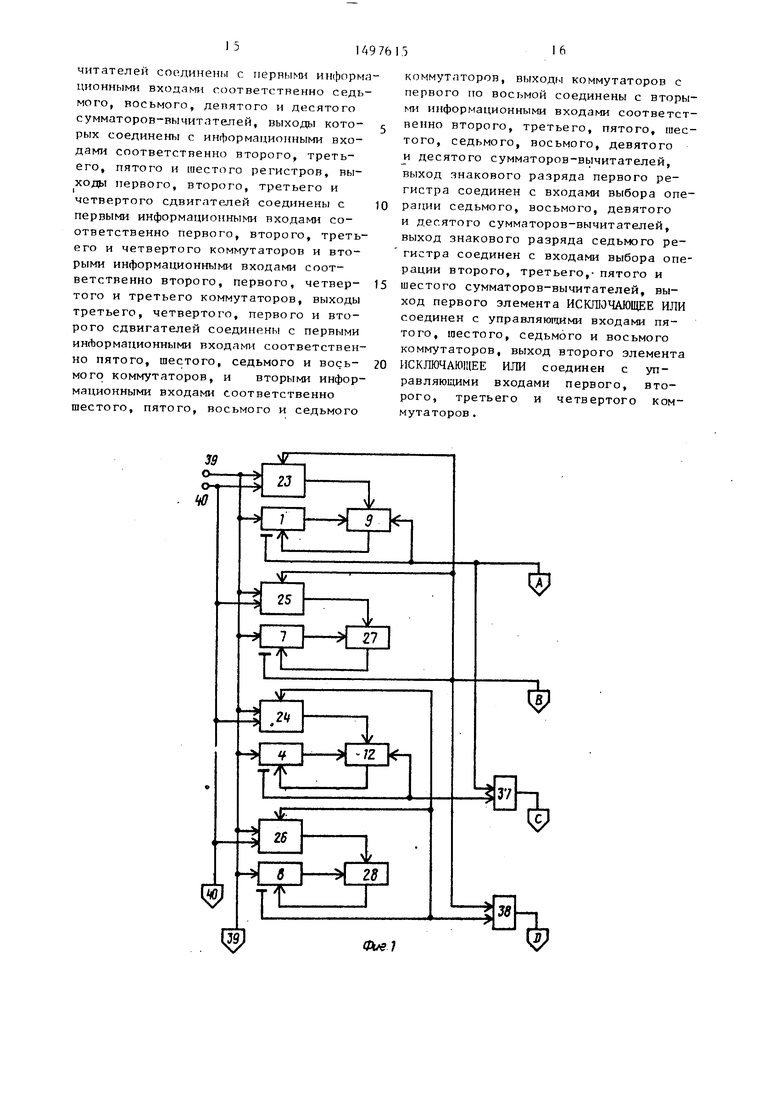

На Лиг, 1 и 2 представлена функциональная схема предлагаемого устройства.

Устройство содержит с первого по восьмой регистры 1-8, с первого по десятый сумматоры-вычитатели 9-18, с первого по четвертый сдвигатели 19-22, с первого по четвертый блоки памяти 23-26, первый 27 и второй 28 вычи- татели, с Т1ервог 5 по восьмой кoм ryтa- торы 29-36, первый 37 и второй 38

элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход 39 и вход 40 номера итерации.

Устройство функционирует следующим образом.

Устройство вычисляет гиперболические синус и косинус:

sh(z) sh(x) .cos(y) + .ich(x) X sin(y),

ch(z) ch(x).cos(y) + jsh(x)x X sin(y)

комплексного переменного z x + jy, где j V -1, no следующему алгоритму.

AlЛ - переменная для обозначения приближения

у L El.arctg ((1+Р1м2

)ho

мнимой части у комплексного аргумента г на л-м шаге алгоритма;

А2л - переменная для обозначения приближения

.{ э

ел

Л-1

Z E2 arctg(2-/(l +

«-1 -)

О

-

мнимой части -у комплексного ар гумен та -Z на л-м шаге алгоритма;

Д1л - переменная для обозначения приближения

Л- и 1 )u i f/ j

X - Т 1п( н- 2 ) -0 м- 1

действительной части х комплексного аргумента z на л-м шаге алгоритма;

Д2л - переменная для обозначения приближения

А-(

-X frt

1п(1 + Р2„ 2 +2 ) --О

Н

ействительной части -х комплексного 20 ргумента -z .на л-м шаге алгоритма; м 1,2,...,л- 1;

(м+ U /2 для нечетных м; (м/2 для четных м;

Е1л е Ч-1,+ 1} - оператор направле-25 ния изменения мнимой части у комплексного аргумента z на л-м шаге алгоритма;30Е2л -1,+ оператор направления изменения мнимой части -у комплексного аргумента -Z на л-м шаге 5 алгоритма;

Р1л t t-1,+1 - оператор направления изменения действительной части X комплексного ар- . 40 гумента z на л-м шаге алгоритма;

Р2л е f-1 , - оператор направления изменения действительной части д5 -X комплексного аргумента -z на л-м шаге алгоритма; Т 1л 6 {о, 15 - оператор выбора

первых приращений i - мнимых и действительных частей приближений функций sh(z) и ch(z) на л-н шаге алгоритма, с где Т 1л ( 1-Р 1л Р2л)/2;

, - оператор выбора . вторых приращений/

- 5

О

20

-25 а30

. 40

д5м

i - , с

54

мнимых и действительных частей приближений функций sh(z) и ch(z) на л-м таг е алгоритма, где Т2л ( 1-Е 1л л Е2л)/2;

В 1л - переменняя для обозначения приближения мнимой части Im(sh(z)) функций sh(z) комплексного переменного z на л-м шаге алгоритма; В2л - переменная для обозначения приближения мни мой части Im(ch(z)) функции ch(z) комплексного переменного z на л-м шаге алгоритма; С 1л - переменная для обозначения приближения действительной части Re(sh(z)) функции sh(z) комплексного переменного z на л-м шаге алгоритма;

С2л - переменная для обозначения приближения действительной части Re(ch(z)) функции ch(z) комплексного переменного z на л-м шаге алгоритма;

л - сквозной номер шага от начала вычислений;

k - номер выполняемой итерации; п - количество разрядов в дробной части числа, количество выполняемых итераций с двойными шагами; п+3 - разрядность устройства,

включая два разряда в целой части числа и знаковый. Области определения функций: О 4 |х( 1; О |у( . Г/2. Области значения функции: 0 I Im(sh(z))l v( е- )/2; 0 I Im(ch(z))l .( fe- )/2; 0, I Re(sh(z))( .( е )/2; Oi I Re(ch(z))| (е + е )/2, где Im(sh(z)) ch(x)sin(y); Im(ch(z)) sh(x)sin(y); Re(sh(z)) sh(x) cos(y); Re(ch(z)) ch(x)-cos(y); Алгоритм вычисления функций sh(z) и ch(z) комплексного переменного z X + jy.

Начальные условия: А1л у;(1)

А2л -у;(2)

ВЦ 0;(3)

0; 1; 1; х; -X.

ации: ЗНАК (А1л); ЗНАК (А2л); ЗНАК (Д1л); ЗНАК (Д2л);

(4) (5) (6) (7) (8)

(9) (10)

(II) (12)

А1л+1 А1л - Е1л arctg ( /(} и- Р1л . 2-));(13)

А2л+t А2л - Е2л. arctg ( /(U+ Р2л 2)); (14)

В1л+1 В 1л + Р1л (Т1л В л« . «2 /Т1л-В2л-2 Ц- Е1л .(Т2л.С1л-2 vT2л-C2л .2);(15)

В2Л-И В2л + Р1л (Т1л В2л-2 VT 1л-В 1л. 2) + Е1л .(T2лC2л-.

-« I

2 Ч Т2Л-С1Л.2);

(16)

С1л+1 С1л + Р1л .(Т|л-С1л 2- V Т 1лС2л 2) - Е1л (Т2л В1лх

- 2-Чт2лВ2л-2 );

,-к.

(17)

k

Г (лн 1 л,

25

30

35

С2л+1 С2л + Р1л-(Т2лС2л-2 V уТ1лС1л-2-) - Е1л(Т2лВ2л УТ2лВ1л-2 ) ;,( 8)

Д1л+1 Д1л - 1п(1 + Р1л-2 + 2-2 Г ;.,„ (19)

Д2л+1 Д2л - 1п(1+Р2л-2+

+ ) ; .(20)

(л+1)для нечетных л;(21) 1/2 для четных, л; (22) л 1,2, . .., 2п . Результаты:

Alln+i 0;(23)

A2ln 1 0;(24)

ВИп+1 Im(sh(z)) ch(x)x xsin(y);(25)

B2ln+ 1 Im(ch(z)) sh(x)x40

xsin(y);(26)

ВС12П+1 Re(sh(z)) sh(x) xcos(y);(27)

C2 :n+ 1 Re(ch(x)) clUx) cos(y);(28) 45

ДИП+ 1 0;(29)

Д21П+1 0(30)

В исходном положении в регистрах аходятся следующие данные:

в первом регистре 1 - аргумент у; сп в четвертом регистре 4 - аргумент

у;

во втором регистре 2 - ноль; в третьем регистре 3 - ноль; в пятом регистре 5 - единица; в шестом регистре 6 - единица; в седьмом регистре 7 - аргумент х; в восьмом регистре 8 - аргумент X.

55

10

15

0

25

0

5

0

5

п

5

Устройство работает циклически. На л-м шаге на тактовый вход 39 устройства подается синхросигнал, а на входы 40 номера итерации - номер k выполняемой итерации. Синхросигнал поступает на синхронизирующие входы первого 1, седьмого 7, четвертого 4, восьмого 8, второго 2, третьего 3, пятого 5 и шестого 6 регистров и на стробируюпие входы первого 23, третьего 25, второго 24 и четвертого 26 блоков памяти. Номер 1с выполняемой итерации поступает на первый вход группы адресных входов первого 23, третьего 25, второго 24 и четвертого 26 блоков памяти и на входы величины сдвига первого 19, второго 20, третьего 21 и четвертого 22 сдвигателей. При этом двум синхросигналам соответствует одно значение k номера выполняемой итерации.

Под воздействием каждого синхросигнала реализуется один шаг алгоритма в соответствии с выражениями (9)-(22).

Значение оператора Е1л снимается с выхода знакового разряда первого регистра 1. Сигнал Е1л поступает на вход выбора операции первого сумма- тора-вычитателя 9 для задания режима работы (сложения или вычитания), на первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 37 для формирования значения оператора Т2л и на входы выбора операции соответственно седьмого 15, восьмого 16, девятого 17 и десятого 18 сумматоров-вычитате- лей для задания режимов работы (сложения или вычитания).

Значение оператора Е2л снимается с выхода знакового разряда четвертого регистра 4. Сигнал Е2л поступает на вход выбора операции четвертого сумматора-вычитателя 12 для задания режима работы (сложения или вычитания) и на второй вход первого элемента ИСКЛ ОЧА101ЦЕЕ ИЛИ 37 для формирования значения оператора Т2л,

Значение оператора Р1л снимается с выхода знаковог о разряда седьмого регистра 7. Сигнал Р1л поступает на второй вход группы адресных входов соответственно первого 23 и третьего 25 блоков памяти для обеспечения выбора соответствующей константы arctg(2- /(1+2 -)) или arctg(2 / /()) в первом блоке 23 памяти и выбора соответствующей константы

1 / , . т - ,, -JUK V2 , x , ., -K I

ln(l+2 +2 ) или ln(l-2 +2 ) в I peTf.GM блоке 25 памяти, ил первый пход второго илементл ИСКЛЮ ШОЩЕК ИЛИ 38 для (Ьормировяния значения one- рлгора Г 1л и на нходД выбора операции соотнетственно второго 10, третьего II, пятого 13 и шестого 1А сум- м,1торов-яычитлтелей для задания режимов работы (сложения или вычитания).

Значение оператора Р2л снимается с выхода знакового разряда восьмого регистра 8. Сигнал Р2л поступает на второй вход группы адресных входов соответственно второго 24 и четверто- го 26 блоков памяти для обеспечения выбора соответствующей константы arctg((I+2 )) или arctg(2- / /(1-2 )) во втором блоке 25 памяти и выбора соответствующей константы In ( +2 ) или 1п(1-2- ) в четвертом.блоке 26 памяти, на второй вход второго элемента ИСКЛЮЧАЮ- П ЕЕ ИЛИ 38 для формирования значения оператора Т 1л.

,Значение оператора Т 1л формируется на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 38. Сигнал Т 1л поступает на управляющие входы соответственно первого 29, второго 30, третьего 31 и четвертого 32 коммутаторов для задания режимов работы. Если Т 1л О, то в первом 29, втором 30, третьем 31 и четвертом 32 коммутаторах выполняется передача чисел с первых информа- ционных входов. Если Т 1л 1, то в первом 29, втором 30, третьем 31 и четвертом 32 коммутаторах выполняется передача чисел с вторых информационных входов.

Значений оператора Т2л формируется на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 37. Сигнал Т2л поступает на управляющие входы соответственно пятого 33, luecToi o 34, седьмого 35 и восьмого 36 коммутаторов. Если , то в пятом 33, шестом 34, седьмом 35 и восьмом 36 коммутаторах выполняется передача чисел с первых информационных входов. Ксли Т2л 1, то в пя- том 33, шестом 34, седьмом 35 и восьмом 36 коммутаторах выполняется передача чисрлг с вторых информационных нходов.

3 соответствии с номером к итерации и значриием оператора Р1л из первого блока 2) памяти считывается константа arctj , (2 /(1+Р1л-2 ).

Предьщу1Г(ее тиачение переменной А1л и ее приращение arctg( / ( I-t- +Р1л 2- ) поступают с выходов первого регистра 1 и выходов первого блока 23 памяти соответственно на первые и вторые информационные входы первого сумматора-вычитателя 9, в результате на его выходах формируется новое значение переменной , которое поступает на информационные входы первого регистра I, где и фиксируется,

В соответствии с номером к итерации и значением оператора Р2л- из второго блока 24 памяти считывается константа arctg(2/( 1+Р2л 2 ) .

Предыдущее значение переменной А2л и ее приращение arctg((1+Р2л 2 ) поступают с выходов четвертого регистра 4 и выходов второго блока 24 памяти соответственно на первые и вторые информационные входы четвер того сумматора-вычитателя 12, в результате на его выходах формируется новое значение переменной А2л+ (, которое поступает на информационные входы четвертого регистра 4, где и. фиксируется.

Предыдущее значение переменной В 1л поступает с выходов второго регистра 2 на первые информационные входы второго сумматора-вычитателя 10 и на информационные входы первого сдвигателя 19, где в соответствии с номером к итерации сдвигается на к разрядов вправо, в результате на выходах первого сдвигателя 19 формируется величина , которая поступает на первые информационные входы первого 29 и седьмого 35 коммутаторов и на вторые информационные входы второго 30 и восьмого 36 коммутаторов .

Предыдущее, значение переменной С 1л поступает с выходов третьего регистра 3 на первые информа1Д1онные входы третьего сумматора-вычитателя 11 и на информационные входы второго сдвигателя 20, где в соответствии с номером к итерации сдвигается на к разрядов вправо, в результате на выходах второго сдвигателя 20 формируется величина В2л «2 , которая поступает на первые информационные входы второго 30 и восьмого 36 коммутаторов и на вторые информационные входы первого 29 и седьмого 35 коммутаторов .

914

Предыду1чее значение переменной В2л поступает с выходов пятот-о регистра 5 на первые информационные входы пятого сумматора-вычитателя 13 и на информационные входы третьего сдвигателя 21, где в соотпетствии с номером к итерации сдвигается на к разрядов вправо, в результате на выходах третьего сдвигателя 2I фор- мируется величина , которая поступает на первые информационные входы третьего 21 и пятого 33 коммутаторов и на вторые информационные входы четвертого 32 и шестого 34 коммута- торов.

Предыдущее значение переменной С2л поступает с выходов шестого регистра 6 на первые инфоркГационные входы шестого суммлтора-вычитателя 1 и на информационные входы четвертого сдвигателя 22, где в соответствии с номером к итерации сдвигается на к разрядов вправо, в результате на выходах четвертого сдвигателя 22 формируется величина С2л 2 , которая поступает на первые информационные входы четвертого 32 и шестого 34 коммутаторов и на вторые информационные входы третьего 31 и пятого 33 коммутаторов.

В зависимости от значения оператора Т1л в первом коммутаторе 29 величины В1л2 и В2л2 поступают с первых или вторых информагшонных входов на выходы, т,е, на выходах первого коммутатора 29 формируется величина (Т1л В1л-2 уТ1л В2Л-2 ), которая поступает на вторые информационные входы второго сумматора-вычитателя 10

В зависимости от значения оператора Т 1л во втором коммутаторе 30 величины В2л2 и поступают с первых или вторых информационных входов на выходы, т.е. на выходах второ- го коммутатора 30 формируется величина (Т1лВ2л2 Т1лВ1л2 ), которая поступает на вторые информационные входы третьего сумматора-вычитателя 11.

В зависимости от значения оператора Т 1л в третьем коммутаторе 31 величины С1л-2 и С2л 2 поступают с первых или вторых информационных входов на выходы, т.е. на выходах третьего коммутатора 31 формируется величина (Т1лС1л-2 % Т1лС2л 2 ), которая поступает на вторые информац::он-

Q 5

о 5 О

Q

g

5

0

5

ные входы ПЯТ01-О сумматора-вычитлте- ля 13.

В зависимости от значения оператора Т 1л в четвертом коммутаторе 32 величиш.1 С2л-2 и С 1л 2 поступают с или вторых информационных входов на выходы, т.е. на выходах четвертого коммутатора 32 фop D pyeтv If

ся величина (Т1л С2л 2 VTlji-CLn-2 ), которая поступает на вторые информационные входы шестого сумматора-вычитателя 14.

В зависимости от значения оператора Т2л в пятом коммутаторе 33 величины С 1л-2 и С2 2 поступают с первых или вторых информационных входов на выходы, т.е. на выходах пятого коммутатора 33 формируется величина (Т2л С 1л С2л 2 ), которая поступает на вторые информационные входы седьмого сумматора-вычитателя 15.

В зависимости от значения оператора Т2л в шестом коммутаторе 34 величины С2л-2 и С 1л 2 поступают с первых или вторых информационных входов на выходы, т.е. на выходах шестого коммутатора 34 формируется величина (Т 2лС2л 2 уТ2л С1л-2 ), которая поступает на вторые информационные входы восьмого сумматора-вычитателя 16,

В зависимости от значения оператора Т2л в седьмом KOMNryTaTope 35 величины В1л2 и В2л2 поступают с первых или вторых иtIфopмaциoнныx входов на выходы, т.е. на выходах седь- мог о коммутатора 35 форьшруется величина ( Т2лВ2л 2), которая поступает на вторые инфоргационные входы девятого сумматора-вычитателя 7,

В зависимости от значения оператора Т2л в восьмом коммутаторе 36 величины В2л-2 и В 1л 2 поступают с первых или вторых информационных входов на выходы, т.е. на выходах восьмого комммутатора 36 формируется величина (Т2л В2л-2 Т2л В1л-2 ), которая поступает на вторые информационные входы десятого сумматора-вы- читателя 18.

В зависимости от значения оператора Р 1л во втором сумматоре-вычита- теле 10 выполняется операция сложения или вычитания предыдущего значения переменной В 1л и ее приращения (Т 1л Bb -2 vTl.-i В2л 2-), н результате нл вь ходпх второго е:умматора-ны- читателя 10 (Ьорьтнруетси величина (В 1л + Р1л (Т 1л BLT2 vTLn В2л-2- ) которая поступает на первые информационные входы седьмого сумматора-вы- читателя 15, где в зави симости от значения оператора Е 1л выполняется операция сложения или вычитания величины В1л+Р1л(Т1л В1л-2 Т1л В2л-2 и ее приращения (Т2л С 1л-2 УТ2л С2л ), в результате на выходах седьмого сумматора-вычитателя 15 формируется новое значение переменной В1л+1 которое поступает на информационные входы второго регистра 2, где и фиксируется ,

В зависимости от значения оператора Р 1л в третьем сумматоре-вычитате- ле 11 выполняется операция сложения или вычитания, предыдущего значени-я переменной В2л и ее приращения (Т1л В2л-2 УТ1л В1л 2), в результате на выходах третьего сумматора- вычитателя 1I формируется величина В2л + Р 1л (Т 1л В2л.2- УТ1л В 1л 2), которая поступает на первые информационные входы восьмого сумматора-вычитателя 16, где в зависимости от значения опер атора Е 1л выполняется операция сложения или вычитания величины В2л Р 1л(т 1л В2л (Т1л ВЫ «2 ) и ее приращения (Т2л УТ2л С 1л 2 ), в результате на выходах восьмого сумматора-вычитателя 16 формируется новое значение переменной В2л+ Г, которое поступает на информационные входы третьего регистра 3, где и фиксируется,

В зависимости от значения оператора Р 1л в пятом сумматоре-вычитате- ле 13 выполняется операция сложения или вычитания предыдущего значения переменной и ее приргЛцения (Jbi С2л-2 УТ.1л С 1л-2 , в результате на выходах пятого сумматора-вычитателя 1 3 формируется величина С 1л .+ -|-Р1л(Т1л С1л 2 УТ1л С2л-2), которая поступает на первые информационные входы девятого сумматора-вычитателя 17, где в зависимости от значения оператора Е1л выполняется операция сложения или В1 1читания величин) С 1л + Р1л (Т 1л С Т 1л С2Л-2 ) и ее приращения (Т2л В1л-2 /Т2л В2л х «2 ), в результате на выходах девятого сумматора-вычитчтеля 17 формируется новое зяаче1ГИР- переменной , которое nociynnoT на информа

0

5

0

5

0

5

0

ционные вход(1 пятого регистра 5, где и фиксируется.

В зависимости от значения оператора Р1л в шестом сумматоре-вычитате- ле 14 выполняется операция сложения или вычитания предьщущего значения переменной С2л и ее приращения ( С2л 2 VTbi С1л-2 ), в результате на выходах шестого сумматора-вычитателя 14 Формируется величина С2л+ +Р1л(Т1л С2л 2- УТ1л С1Л.2), которая поступает на первые информационные входы десятого сумматора-вычита- 5 теля 18, где в зависимости от значения оператора Е 1л выполняется операция сложения или вычитания величины С2л Р 1л(Т 1л С2л-2 УТ1л ) и ее приращения (Т2л В2л-2 УТ2л В 1л « 2), в результате на выходах десятого сумматора-вычитателя 18 формируется новое значение переменной С2л+1, которое поступает на информационные входы щестого регистра 6, где и фиксируется .

В соответствии с номером к итерации и значением оператора Р1л из третьего блока 25 памяти считывается константа 1п( 1+Р 1л - 2 + 2) Предыдущее значение переменной Д1лиее приращение 1п( 1+Р 1л-2 +2 ) поступают с выходов седьмого регистра 7 и выходов третьего блока 25 памяти на входы уменьшаемого и входы вычитаемого первого вычитателя 27, в результате на его выходах формируется новое значение переменной Д1л+и, которое поступает на информационные входы седьмого регистра 7, где и фиксируется .

В соответствии с номером к итерации и значением оператора Р2л из четвертого блока 26 памяти считывается константа 1п ( 1+Р2л-2 V

Предыдущее значение переменной Д2л и ее приращение 1п( И-Р2л-2 - +2 У поступают с выходов восьмого регистра 8 и выходов четвертого блока 26 памяти на входы уменьшаемого и входы вычитаемого второго вычитателя 28, в результате на его выходах формируется новое значение переменной Д2л+ , которое поступает на информационные входы восьмого регистра 8, где и фиксируется,

Все итерационные шаги выполняются в устройстве аналогично рассмотренному.

5

После выполнения п итераций с двойными luaraNtti в регистрах зафиксированы следующие результаты:

в первом регистре I -

в четвертом регистре 4 - A27n-i-l 0

во втором регистре 2 - B 2n+i

Im(sh(z))ch(x)sin(y);

в третьем регистре 3 - В22и+1

Im(ch(z)) sh(x)«siny;

в пятом регистре 5 - C12n+i

Re(sh(z)) sh(x)cos(y);

в шестом регистре 6 - C22n- i

Re(ch(z)) ch(x)-cosCy) ;

в седьмом регистре 7 - 0

в восьмом регистре 8 Д22п+ 0

Форм у л а и 3 о б р.е-т е н и я

Устройство для вычисления гипер- болических синуса и косинуса, содержащее три регистра, три суммятора-вы- читателя, два сдвигателя, первый блок памяти, причем выходы первого, второго и третьего регистров соединены с первыми информационными входами соответственно первого, второго и третьего сумматоров-вычитателей, выходы первого сумматора-вычитателя соединены с информационными входами пер- вого регистра, выходы первого блока памяти соединены с вторыми информационными входами первого сумматора-вычитателя, выходы второго и третьего регистров соединены с информационными входами соответственно первого и второго сдвигателей, тактовый вход устройства соединен с синхронизирующими входами первого, второго и третьего регистров и стробирующим входом

первого блока памяти, вход номера

итерации устройства соединен с входами величины сдвига первого и второго сдвигателей и с первым входом группы адресных входов первого блока памяти, выход знакового разряда первого регистра соединен с входом выбора операции первого сумматора- вычитателя, отличающееся

тем, что, с целью расигирения класса решаемых задач за счет возможности вычисления гиперболических синуса и косинуса комплексного переменного, в него введены регистры с четвертого по восьмой, сумматоры-нычитатели с четвертого по десятый, третий и четвертый сдвигатели, второй, третий и четвертый блоки памяти, первый и второй вычитатели, коммутаторы с перво,Q

jj

OQ 5 ,Q .„ 0

5

0

5

го по восьмой, первый и иторой элементы HCKinOMAIOliJKE ИЛИ, причем выходы четвертого, пятого и шестого регист- ров соединены с первыми информационными рходами соответственно четвертого, пятого и шестого сумматоров-вычитателей, выходы четвертого сумматора-вычитателя соединены с информационными входами четвертого регистра, выходы второго блока памяти соединены с вторыми информационными входами четвертого сумматора-вычитателя, выходы пятого и inecToro регистров соединены с информационными входами соответственно третьего и четвертого сдвигателей, тактовый вход устройства соединен с синхронизирующими входами четвертого, пятого и шестого регистров и стробирующим входом второго блока памяти, вход номера итерации устройства соединен с входами величины сдвига третьего и четвертого сдвигателей и первым входом группы адресных входов второго блока памяти, выход знакового разряда четвертого регистра соединен с входом выбора операции четвертого сумматора-вычитате- ля, выходы третьего и четвертого блоков памяти соединены с входами вычитаемого соответственно первого и второго вычитателей, выходы которых соединены с информационными входами соответственно седьмого и восьмого регистров, выходь которых соединены с входами уменьшаемого соответственно первого и второго вычитателей, тактовый вход устройства соединен с синхронизирующими входами седьмого и восьмого регистров и стробирук щими входами третьего и четвертого блоков памяти, вход номера итерации устройства соединен с первыми входами группы адресных входов третьего и четвертого блоков памяти, выходы знаковых разрядов первого и четвертого регистров соединены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы знаковых разрядов седьмого и восьмого регистров соединены с вторыми входа№1 группы адресных входов соответственно первого и второго блоков памяти, вторыми входами группы адресных входов соответственно третьего и четвертого блоков памяти и соответстверпю с первым и вторым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, рыхп;ь1 второго, третьего, пятого и iijecT4r T сумматорон-пщчитателей соединены с первыми информационными входами соответственно седьмого, восьмого, девятого и десятого сумматоров-вычитлтелей, выходы кото- рых соединены с информационными входами соответственно второго, третьего, пятого и шестого регистров, выходы первого, второго, третьего и четвертого сдвигателей соединены с первыми информационными входами соответственно первого, второго, третьего и четвертого коммутаторов и вторыми информационными входами соответственно второго, первого, четвер- того и третьего коммутаторов, выходы третьего, четвертого, первого и второго сдвигателей соединены с первыми инАормационными входами соответственно пятого, шестого, седьмого и вось- МО го коммутаторов, и вторыми информационными входами соответственно шестого, пятого, восьмого и седьмого

коммутаторов, выходр коммутаторов с первого по восьмой соединены с вторы- т информационными входами соответственно второго, третьего, пятого, шестого, седьмого, восьмого, девятого и десятого сумматоров-вычитателей, выход знакового разряда первого регистра соединен с входами вьгбора операции седьмого, восьмого, девятого и десятого сумматоров-вычитателей, выход знакового разряда седьмого регистра соединен с входами выбора операции второго, третьего,- пятого и шестого сумматоров-вычитателей, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющими входами пятого, шестого, седьмого и восьмого коммутаторов, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющими входами первого, второго, третьего и четвертого коммутаторов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для вычисления функции @ | 1987 |

|

SU1456954A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

| Устройство для вычисления эллиптических функций | 1987 |

|

SU1474641A2 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных процессоров. Целью изобретения является расширение класса решаемых задач за счет вычисления гиперболических функций синуса и косинуса комплексного переменного. Устройство содержит регистры , сумматоры-вычитатели, сдвигатели, блоки памяти, первый и второй вычитатели, коммутаторы, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход , вход номера операции. 2 ил.

Ж сзэ:

.с J 1А

Авторы

Даты

1989-07-30—Публикация

1987-11-23—Подача