Изобретение относится к вычислительной технике и может быть использовано в процессорах цифровых электронных вычислительных машин.

Цель изобретения - расширение области применения устройства за счет выявления конфликтов при обращении к смежным регистрам общего назнечения.

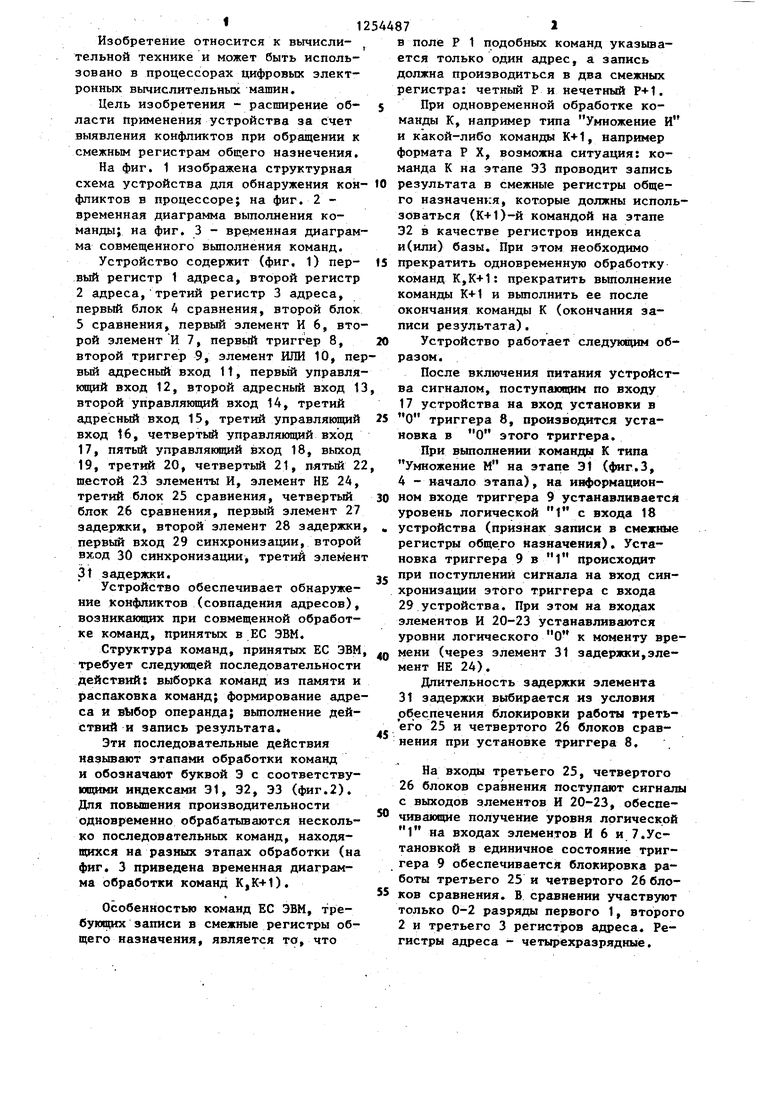

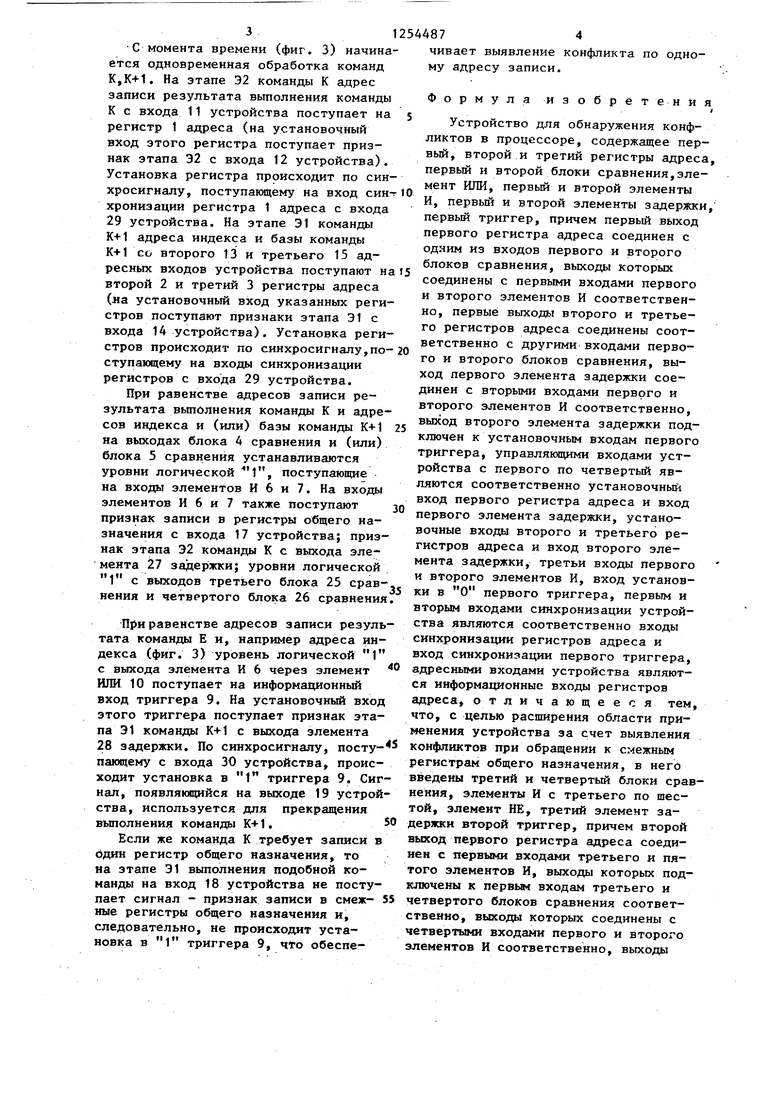

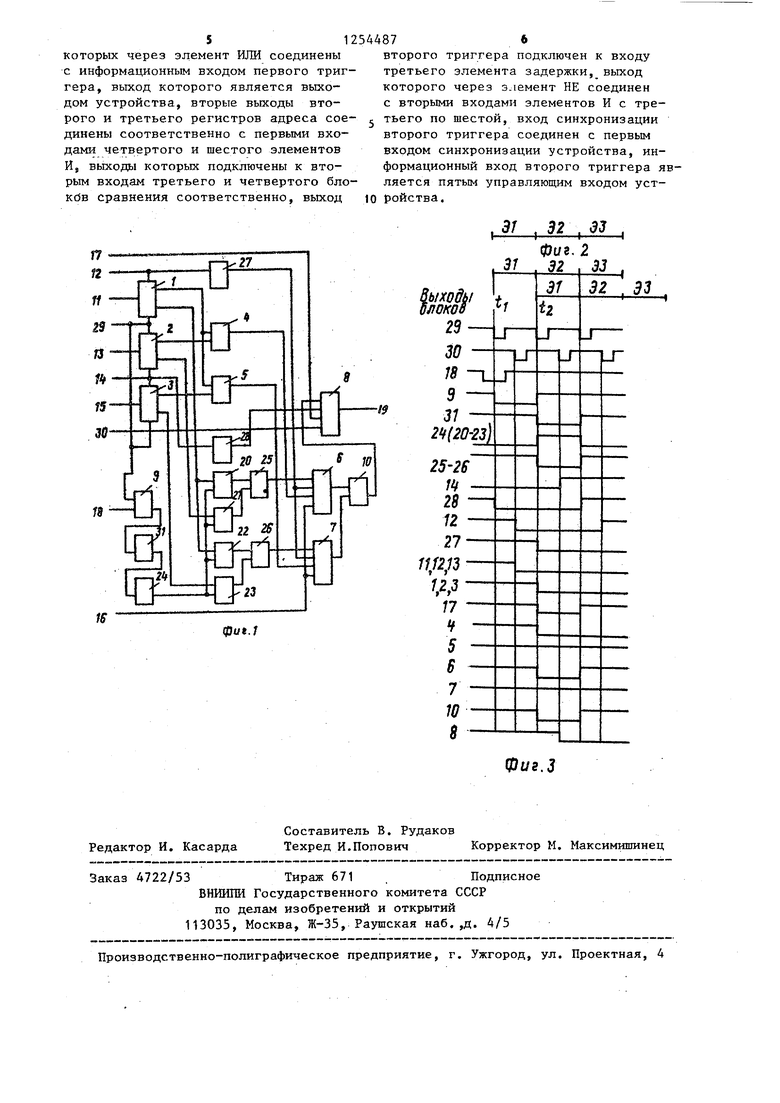

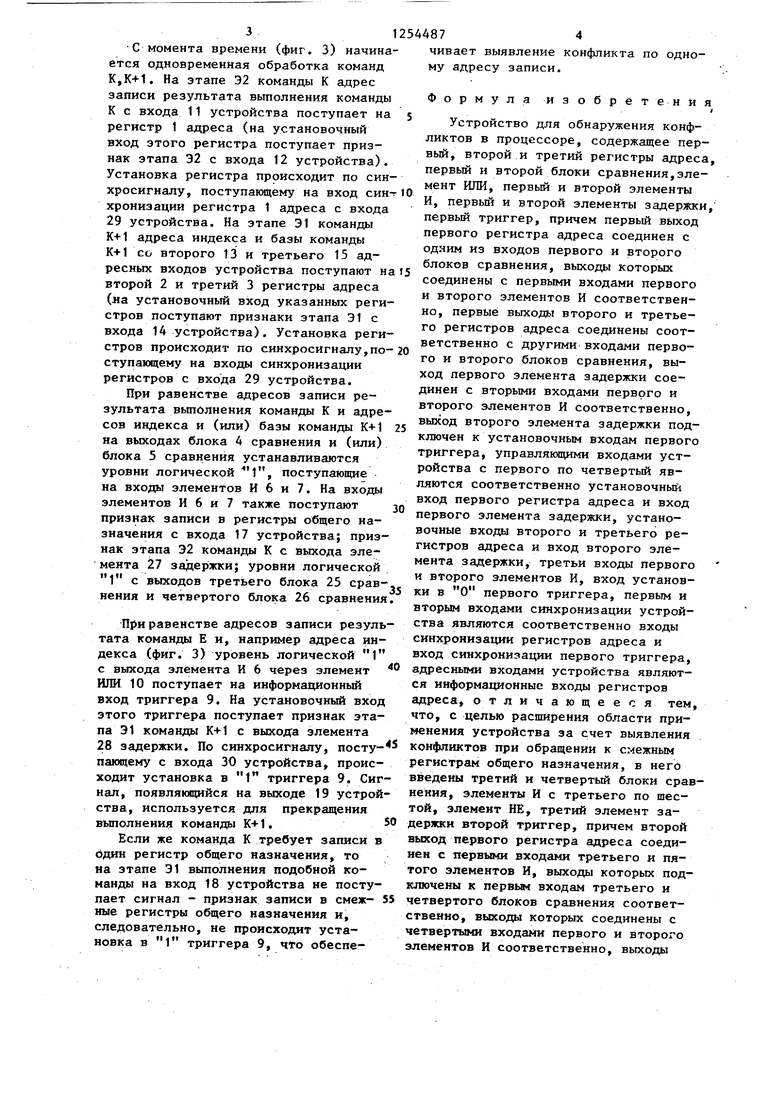

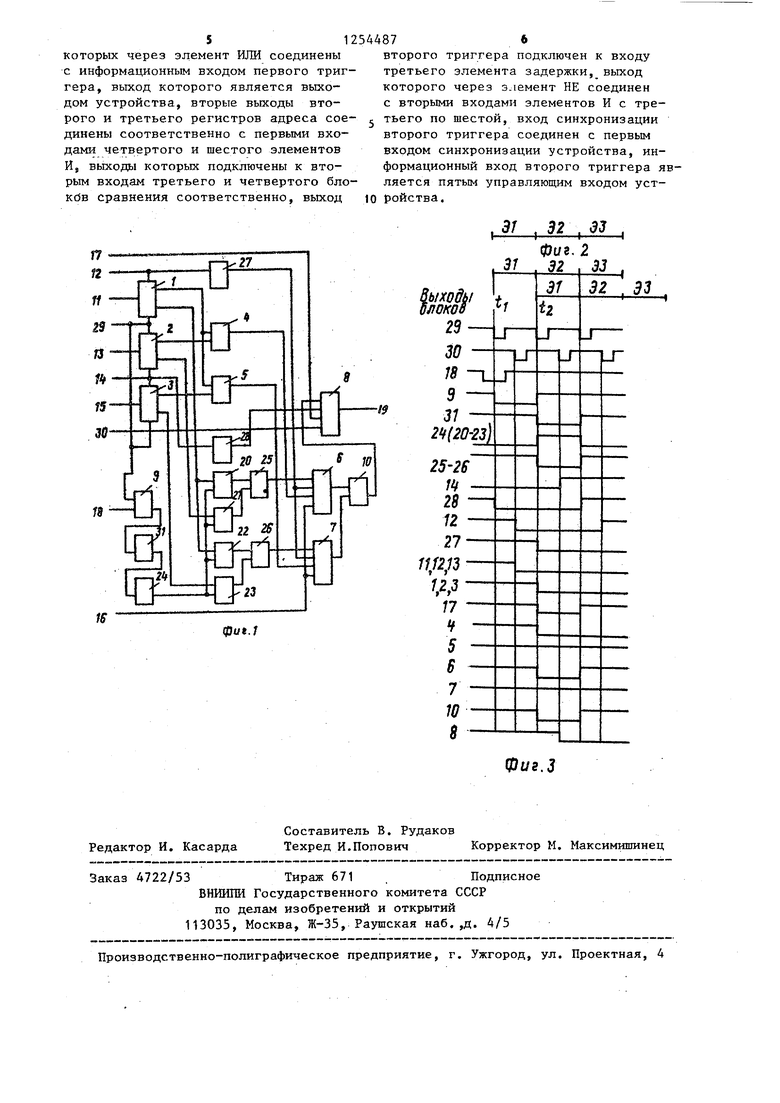

На фиг. 1 изображена структурная схема устройства для обнаружения конфликтов в процессоре; на фиг. 2 - временная диаграмма вьтолнения команды; на фиг. 3 - вре енная диаграмма совмещенного выполнения команд.

Устройство содержит (фиг, 1) первый регистр 1 адреса, второй регистр 2 адреса, третий регистр 3 адреса, первый блок 4 сравнения, второй блок 5 сравнения, первый элемент И 6, второй элемент И 7, первый триггер 8, второй триггер 9, элемент ИЛИ 10, первый адресный вход И, первьй управляющий вход 12, второй адресный вход 13 второй управляющий вход 14, третий адресный вход 15, третий управляющий вход 16, четвертый управляющий вход 17, пятый управлякиций вход 18, выход 19, третий 20, четвертый 21, пятый 22 шестой 23 элементы И, элемент НЕ 24, третий блок 25 сравнения, четвертый блок 26 сравнения, первый элемент 27 задержки, второй элемент 28 задержки первый вход 29 синхронизации, второй вход 30 синхронизации, третий элемент

31 задержки.

Устройство обеспечивает обнаружение конфликтов (совпадения адресов), возникающих при совмещенной обработке команд, принятых в ЕС ЭВМ.

Структура команд, принятых ЕС ЭВМ требует следующей последовательности действий: выборка команд из памяти и распаковка команд; формирование адреса и выбор операнда; вьтолнение действий и запись результата.

Эти последовательные действия называют этапами обработки команд и обозначают буквой Э с соответствующими индексами Э1, Э2, ЭЗ (фиг,2). Для повышения производительности одновременно обрабатываются несколько последовательных команд, находящихся на разньа этапах обработки (на фиг. 3 приведена временная диаграмма обработки команд KiK-fl).

Особенностью команд ЕС ЭВМ, требующих записи в смежные регистры общего назначения, является то, что

o

5

0

5

.

30

5

45

50

55

в поле Р 1 подобных команд указывается только один адрес, а запись должна производиться в два смежных регистра: четный Р и нечетный Р+1.

При одновременной обработке команды К, например типа Умножение И и какой-либо команды К-«-1, например формата Р X, возможна ситуация: команда К на этапе ЭЗ проводит запись результата в смежные регистры общего назначения, которые должны использоваться (К+1)-й командой на этапе Э2 в качестве регистров индекса и(или) базы. При этом необходимо прекратить одновременную Обработку команд К,К+1: прекратить вьтолнение команды К+1 и вьтолнить ее после окончания команды К (окончания записи результата).

Устройство работает следующим образом.

После включения питания устройства сигналом, поступающим по входу 17 устройства на вход установки в О триггера 8, производится установка в О этого триггера.

При выполнении команды К типа Умножение М на этапе Э1 (фиг.3, 4 - начало этапа), на информационном входе триггера 9 устанавливается уровень логической 1 с входа 18 устройства (признак записи в смежные регистры общего назначения).. Установка триггера 9 в 1 происходит при поступлений сигнала на вход синхронизации этого триггера с входа 29 устройства. При этом на входах элементов И 20-23 устанавливаются уровни логического О к моменту времени (через элемент 31 задержки,элемент НЕ 24).

Длительность задержки элемента 31 задержки выбирается из условия обеспечения блокировки работы третьего 25 и четвертого 26 блоков сравнения при установке триггера 8,

На входы третьего 25, четвертого 26 блоков сравнения поступают сигналы с выходов элементов И 20-23, обеспечивающие получение уровня логической 1 на входах элементов И 6 и 7.Установкой в единичное состояние триггера 9 обеспечиваете блокировка работы третьего 25 и четвертого 26 блоков сравнения, В сравнении участвуют только 0-2 разряды первого 1, второго 2 и третьего 3 регистров адреса. Регистры адреса - четырехразрядные.

С момента времени (фиг, 3) начинается одновременная обработка команд К,К+1, На этапе 32 команды К адрес записи результата выполнения команды К с входа 11 устройства поступает на регистр 1 адреса (на установочный вход этого регистра поступает признак этапа 32 с входа 12 устройства). Установка регистра происходит по синхросигналу, поступающему на вход синт хронизации регистра 1 адреса с входа 29 устройства. На этапе 31 команды К+1 адреса индекса и базы команды К+1 со второго 13 и третьего 15 адресных входов устройства поступают на второй 2 и третий 3 регистры адреса (на установочный вход указанных регистров поступают признаки этапа 31 с входа 14 устройства). Установка регистров происходит по синхросигналу,поступающему на входы синхронизации регистров с входа 29 устройства.

При равенстве адресов записи результата вьтолнения команды К и адресов индекса и (или) базы команды К+1 на выходах блока 4 сравнения и (или) блока 5 сравнения устанавливаются уровни логической I, поступающие на входы элементов И 6 и 7. На входы элементов И 6 и 7 также поступают признак записи в регистры общего назначения с входа 17 устройства; признак этапа 32 команды К с выхода элемента 27 задержки; уровни логической 1 с выходов третьего блока 25 срав

нения и четвертого блока 26 сравнения.

Устройство для обнаружения конфликтов в процессоре, содержащее пер вый, второй и третий регистры адрес первый и второй блоки сравнения,эле мент ИЛИ, первый и второй элементы И, первый и второй элементы задержк первый триггер, причем первый выход первого регистра адреса соединен с одним из входов первого и второго блоков сравнения, выходы которых соединены с первыми входами первого и второго элементов И соответственно, первые выходы второго и третьего регистров адреса соединены соответственно с другими входами первого и второго блоков сравнения, выход первого элемента задержки соединен с вторыми входами первого и второго элементов И соответственно, выход второго элемента задержки подключен к установочным входам первого триггера, управлякицими входами устройства с первого по четвертый являются соответственно установочный вход первого регистра адреса и вход первого элемента задержки, установочные входы второго и третьего регистров адреса и вход второго элемента задержки, третьи входы первого и второго элементов И, вход установки в О первого триггера, первым и вторым входами синхронизации устройства являются соответственно входы синхронизацки регистров адреса и вход синхронизации первого триггера, адресными входами устройства являются информационные входы регистров адреса, отличающееся тем что, с целью расширения области применения устройства за счет выявления

При равенстве адресов записи результата команды Е и, например адреса индекса (фиг. 3) уровень логической 1 с выхода элемента И 6 через элемент ШЖ 10 поступает на информационный вход триггера 9. На установочный вход этого триггера поступает признак этапа 3t команды К+1 с выхода элемента 28 задержки. По синхросигналу, посту- конфликтов при обращении к смежным пающему с входа 30 устройства, проис- регистрам общего назначения, в него ходит установка в 1 триггера 9. Сигнал, появляющийся на выходе 19 устройства, используется для прекращения ньшолнения команда1 К+1.

Если же команда К требует записи в один регистр общего назначения, то на этапе 31 выполнения подобной команды на вход 18 устройства не постувведены третий и четвертый блоки срав нения, элементы И с третьего по шестой, элемент НЕ, третий элемент задержки второй триггер, причем второй выход первого регистра адреса соединен с первыми входами третьего и пятого элементов И, выходы которых подключены к первьм входам третьего и

пает сигнал - признак записи в смеж- 55 четвертого блоков сравнения соответные регистры общего назначения и, следовательно, не происходит установка в 1 триггера 9, что обеспеs10 15 20

25

0

5

чивает выявление конфликта по одному адресу записи.

Формула изобретения

f

Устройство для обнаружения конфликтов в процессоре, содержащее первый, второй и третий регистры адреса, первый и второй блоки сравнения,элемент ИЛИ, первый и второй элементы И, первый и второй элементы задержки, первый триггер, причем первый выход первого регистра адреса соединен с одним из входов первого и второго блоков сравнения, выходы которых соединены с первыми входами первого и второго элементов И соответственно, первые выходы второго и третьего регистров адреса соединены соответственно с другими входами первого и второго блоков сравнения, выход первого элемента задержки соединен с вторыми входами первого и второго элементов И соответственно, выход второго элемента задержки подключен к установочным входам первого триггера, управлякицими входами устройства с первого по четвертый являются соответственно установочный вход первого регистра адреса и вход первого элемента задержки, установочные входы второго и третьего регистров адреса и вход второго элемента задержки, третьи входы первого и второго элементов И, вход установки в О первого триггера, первым и вторым входами синхронизации устройства являются соответственно входы синхронизацки регистров адреса и вход синхронизации первого триггера, адресными входами устройства являются информационные входы регистров адреса, отличающееся тем, что, с целью расширения области применения устройства за счет выявления

конфликтов при обращении к смежным регистрам общего назначения, в него

конфликтов при обращении к смежным регистрам общего назначения, в него

введены третий и четвертый блоки сравнения, элементы И с третьего по шестой, элемент НЕ, третий элемент задержки второй триггер, причем второй выход первого регистра адреса соединен с первыми входами третьего и пятого элементов И, выходы которых подключены к первьм входам третьего и

ственно, выходы которых соединены с четвертыми входами первого и второго элементов И соответственно, вьосоды

которых через элемент ИЛИ соединены с информационным входом первого триггера, выход которого является выходом устройства, вторые выходы второго и третьего регистров адреса соединены соответственно с первыми входами четвертого и шестого элементов И, выходы которых подключены к вторым входам третьего и четвертого бло- кбв сравнения соответственно, выход

IS

(Put.j

Редактор И. Касарда

Составитель В. Рудаков

Техред И,Попович Корректор М. Максимишинец

Заказ 4722/53Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. ,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

второго триггера подключен к входу третьего элемента задержки, выход которого через элемент НЕ соединен с вторьми входами элементов И с тре5 тьего по шестой, вход синхронизации второго триггера соединен с первым входом синхронизации ycTpovicTBa, информационный вход второго триггера яляется пятым управляющим входом уст10 ройства.

.3/ ,32 ,J ,

фуг. 2 31

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2017 |

|

RU2644505C1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Запоминающее устройство | 1982 |

|

SU1016832A1 |

| Устройство программного управления | 1991 |

|

SU1781671A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах цифровых электронных вычислительных машин. Цель изобретения - расширение области применения устройства за счет выявления конфликтов при обращении к смежным регистрам общего назначения. Устройство содержит регистры адреса, блоки сравнения, элементы И, триггеры, элемент ИЛИ, элемент НЕ. Устройство обеспечивает обнаружение конфликтов (совпадение адресов), возникающих при совмещенной обработке команд, принятых в ЕС ЭВМ. Использование устройства в ЭБМ обеспечивает повьппение производительности ЭВМ за счет своевременного выявления возможного конфликта и вы:- хода из режима совмещенной обработки команд только в этом случае. 3 ил.

| Запоминающее устройство | 1976 |

|

SU613402A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Техническое описание, раздел ТО 1, приложение 3, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| . | |||

Авторы

Даты

1986-08-30—Публикация

1985-01-02—Подача