Изобретение относится к вычислительной технике и может быть использовано для сложения двоично-десятичных чисел в арифметических устройствах ЦВМ .

Цель изобретения - увеличение быстродействия.

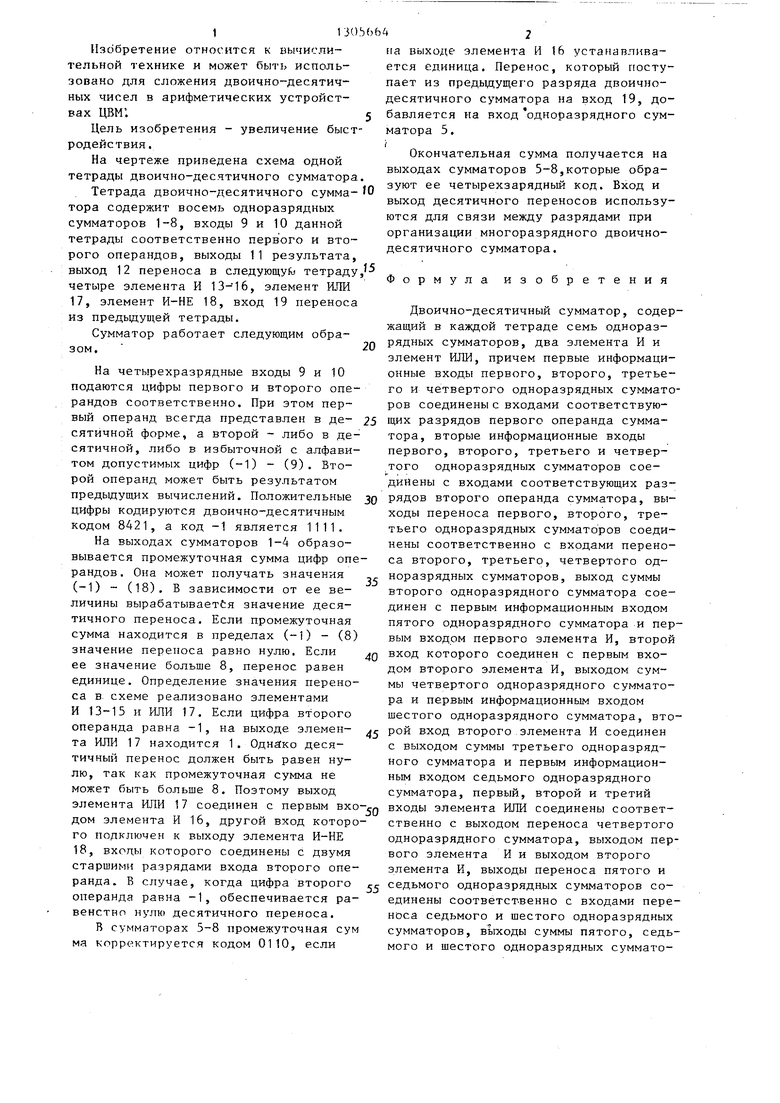

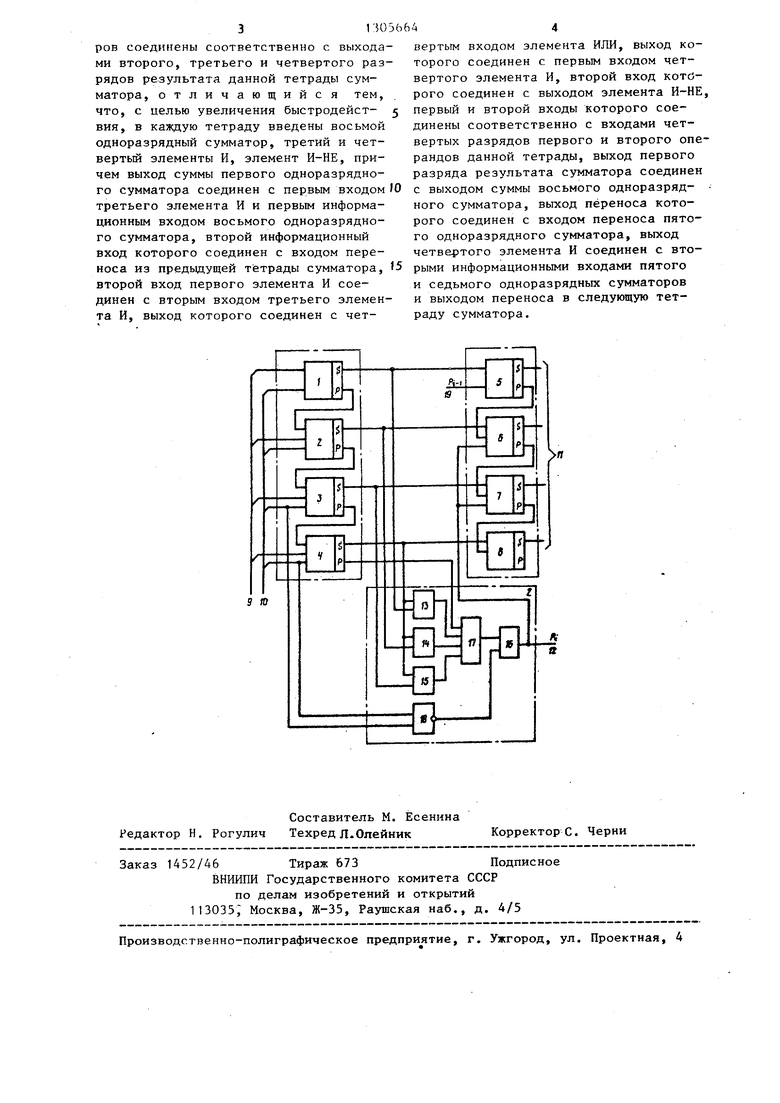

На чертеже приведена схема одной тетрады двоично-десятичного сумматора

Тетрада двоично-десятичного сумма- тора содержит восемь одноразрядных сумматоров 1-8, входы 9 и 10 данной тетрады соответственно первого и второго операндов, выходы 11 результата, выход 12 переноса в следующую тетраду четыре элемента И 13- 1б, элемент ИЛИ 17, элемент И-НЕ 18, вход 19 переноса из предыдущей тетрады.

Сумматор работает следующим образом.

На четырехразрядные входы 9 и 10 подаются цифры первого и второго операндов соответственно. При этом первый операнд всегда представлен в де- сятичной форме, а второй - либо в десятичной, либо в избыточной с алфавитом допустимых цифр (-1) - (9). Второй операнд может быть результатом предьщущих вычислений. Положительные цифры кодируются двоично-десятичным кодом 8421, а код -1 является 1111.

На выходах сумматоров 1-4 образовывается промежуточная сумма цифр операндов. Oiia может получать значения (-1) (18). В зависимости от ее величины вырабатывается значение десятичного переноса. Если промежуточная сумма находится в пределах (-1) - (8) значение переноса равно нулю. Если ее значение больше 8, перенос равен единице. Определение значения переноса в. схеме реализовано элементами И 13-15 и ИЛИ 17. Если цифра второго операнда равна -1, на выходе элемента ИЛИ 17 находится 1. Однако десятичный перенос должен быть равен нулю, так как промежуточная сумма не может быть больше 8. Поэтому выход элемента ИЛИ 17 соединен с первым входом элемента И 16, другой вход которого подключен к выходу элемента И-НЕ 18, входы которого соединены с двумя старшими разрядами входа второго операнда. В случае, когда цифра второго операнда равна -1, обеспечивается равенство нулю десятичного переноса.

В сумматорах 5-8 промежуточная сум ма корректируется кодом 0110, если

О 5

0

0

35

5

на выходе элемента И 16 устанавливается единица. Перенос, который поступает из предьщущего разряда двоично- десятичного сумматора на вход 19, добавляется на вход одноразрядного сумматора 5. (

Окончательная сумма получается на

выходах сумматоров 5-8,которые образуют ее четырехзарядный код. Вход и выход десятичного переносов используются для связи между разрядами при организации многоразрядного двоично- десятичного сумматора.

Формула изобретения

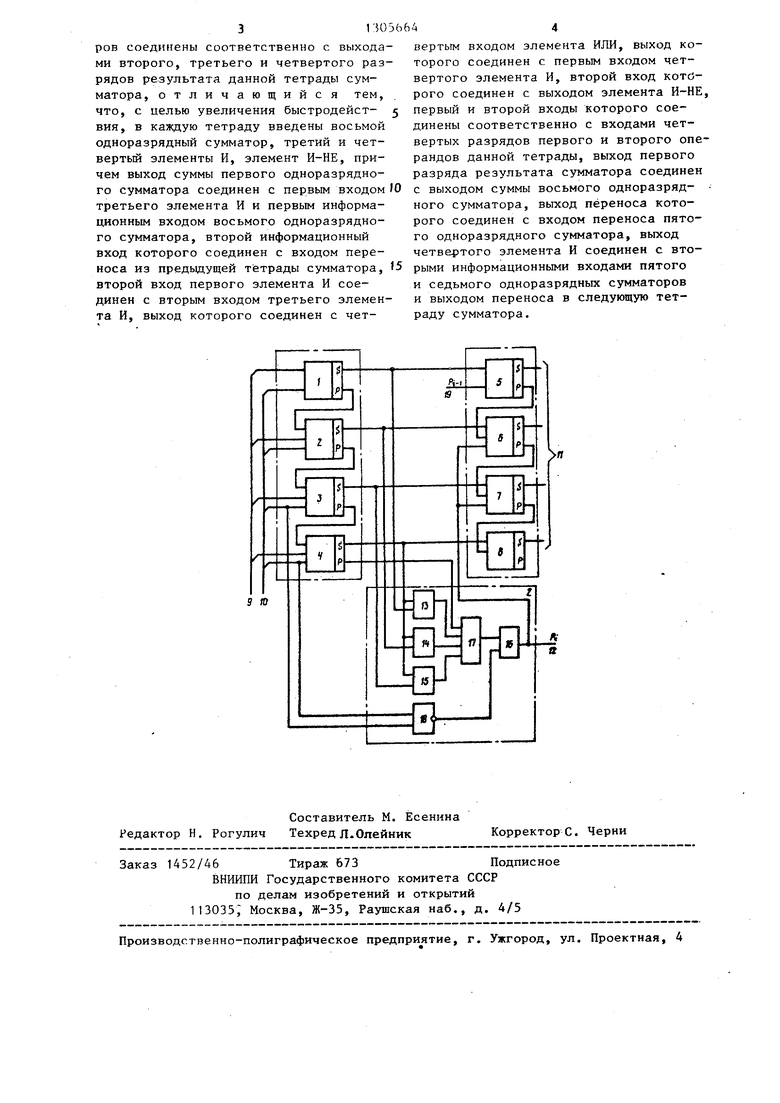

Двоично-десятичный сумматор, содержащий в каждой тетраде семь одноразрядных сумматоров, два элемента И и элемент ИЛИ, причем первые информационные входы первого, второго, третьего и четвертого одноразрядных сумматоров соединены с входами соответствующих разрядов первого операнда сумматора, вторые информационные входы первого, второго, третьего и четвертого одноразрядных сумматоров соединены с входами соответствующих разрядов второго операнда сумматора, выходы переноса первого, второго, третьего одноразрядных сумматоров соединены соответственно с входами переноса второго, третьего, четвертого одноразрядных сумматоров, выход суммы второго одноразрядного сумматора соединен с первым информационным входом пятого одноразрядного сумматора и первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И, выходом суммы четвертого одноразрядного сумматора и первым информационным входом шестого одноразрядного сумматора, рой вход второго элемента И соединен с выходом суммы третьего одноразрядного сумматора и первым информационным входом седьмого одноразрядного сумматора, первый, второй и третий

входы элемента ИЛИ соединены соответственно с выходом переноса четвертого одноразрядного сумматора, выходом первого элемента И и выходом второго элемента И, выходы переноса пятого и

седьмого одноразрядных сумматоров соединены соответственно с входами переноса седьмого и шестого одноразрядных сумматоров, выходы суммы пятого, седьмого и шестого одноразрядных суммато40

ров соединены соответственно с выходами второго, третьего и четвертого разрядов результата данной тетрады сумматора, отличающийся тем, что, с целью увеличения быстродейст- j ВИЯ, в каждую тетраду введены восьмой одноразрядный сумматор, третий и четвертый элементы И, элемент И-НЕ, причем выход суммы первого одноразрядного сумматора соединен с первым входом 10 с выходом суммы восьмого одноразрядтретьего элемента И и первым информационным входом восьмого одноразрядного сумматора, второй информационный вход которого соединен с входом переноса из предьщущей тетрады сумматора, J5 второй вход первого элемента И соединен с вторым входом третьего элемента И, выход которого соединен с четвертым входом элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, второй вход котй- рого соединен с выходом элемента И-НЕ, первый и второй входы которого соединены соответственно с входами четвертых разрядов первого и второго операндов данной тетрады, выход первого разряда результата сумматора соединен

ного сумматора, выход переноса которого соединен с входом переноса пятого одноразрядного сумматора, выход четвертого элемента И соединен с вторыми информационными входами пятого и седьмого одноразрядных сумматоров и выходом переноса в следующую тетраду сумматора.

5 Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный сумматор в избыточной системе счисления | 1985 |

|

SU1256015A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Десятичный сумматор в избыточной системе счисления | 1988 |

|

SU1594524A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Устройство для суммирования фибоначчиево-десятичных кодов | 1981 |

|

SU945862A1 |

Изобретение относится к вычислительной технике и может быть использовано для сложения двоично-десятичных чисел в арифметических устройствах ЦВМ. Целью изобретения является Новьшзение быстродействия двоично-десятичного сумматора за счет исключения зависимости значения десятичного переноса в старший разряд от его значения из младшего разряда. Результат вычислений представляется в избыточном знакоразрядном коде, а операндами сумматора могут быть либо два числа в обычном двоично-десятичном представлении, закодированных кодом 8Д21, либо одно десятичное число и одно избыточное, которое Может быть результатом предьщущих вычислений. Двоично- десятичный сумматор содержит входную тетраду двоичных сумматоров, выходную тетраду двоичных сумматоров и блок формирования переноса. Отличительная особенность заключается в отсутствии связи между входом десятичного переноса и блоком формирования переноса, а также в том, что блок формирования переноса содержит дополнительный элемент И и элемент И-НЕ. 1 ил. I (Л со о СП О5 05

Составитель М. Есенина Редактор Н. Рогулич Техред л.Олейник

Заказ 1452/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректоре. Черни

| Рабинович З.Л,, Романаускас Б.А, Типовые операции в вычислительных машинах, - К.: Техника, 1980, с | |||

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Цифровые электронные вычислительные машины | |||

| - К.: Высшая школа, 1983, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-23—Публикация

1985-04-03—Подача